- •1) Логические элементы. Таблицы соответствия, переключательные функции.

- •2) Кнф и днф переход от одной формы к другой

- •4) Карты Карно

- •5) Rs триггер на элементах и-не

- •6) Rs триггер на элементах или-не

- •7) Синхронный двухтактный rs – триггер

- •11) Регистры последовательный и параллельный

- •12) Трехразрядный последовательный регистр

- •13) Универсальный регистр

- •14) Суммирующий счетчик с последовательным переносом

- •15)Вычитающий счетчик с последовательным переносом

- •16) Трехразрядный реверсивный счетчик на 2-х тактном т-триггере

- •17) Счетчик со сквозным переносом

- •18) Кольцевой счетчик

- •19) Дешифраторы

- •20) Прямоугольный дешифратор.

- •21) Каскадный дешифратор.

- •22) Шифраторы

- •23) Сумматоры

- •24) Полусумматор

- •25) Мультиплесоры

- •26) Демультиплексоры

- •27) Зу эвм. Иерархическая структура памяти эвм

- •28) Зу с непосредственной адресацией

- •29) Сверхоперативное зу с непосредственной адресацией

- •30) Ассоциативное зу

- •31) Созу с ассоциативной адресацией

- •32) Комбинационное алу магистрального типа

- •33) Накапливающее алу

- •34)16-Разрядное универсальное алу

- •35) Алу для сложения чисел с фиксированной запятой

- •36) Алу для умножения чисел с фиксированной запятой.

- •37)Четыре способа умножения чисел с фиксированной запятой в алу

- •38) Центральное устройство управления процессором

- •39) Основные характеристики системы прерывания и диаграмма прерываний

- •40) Блок прерываний процессора

- •41) Блок синхронизации процессора.

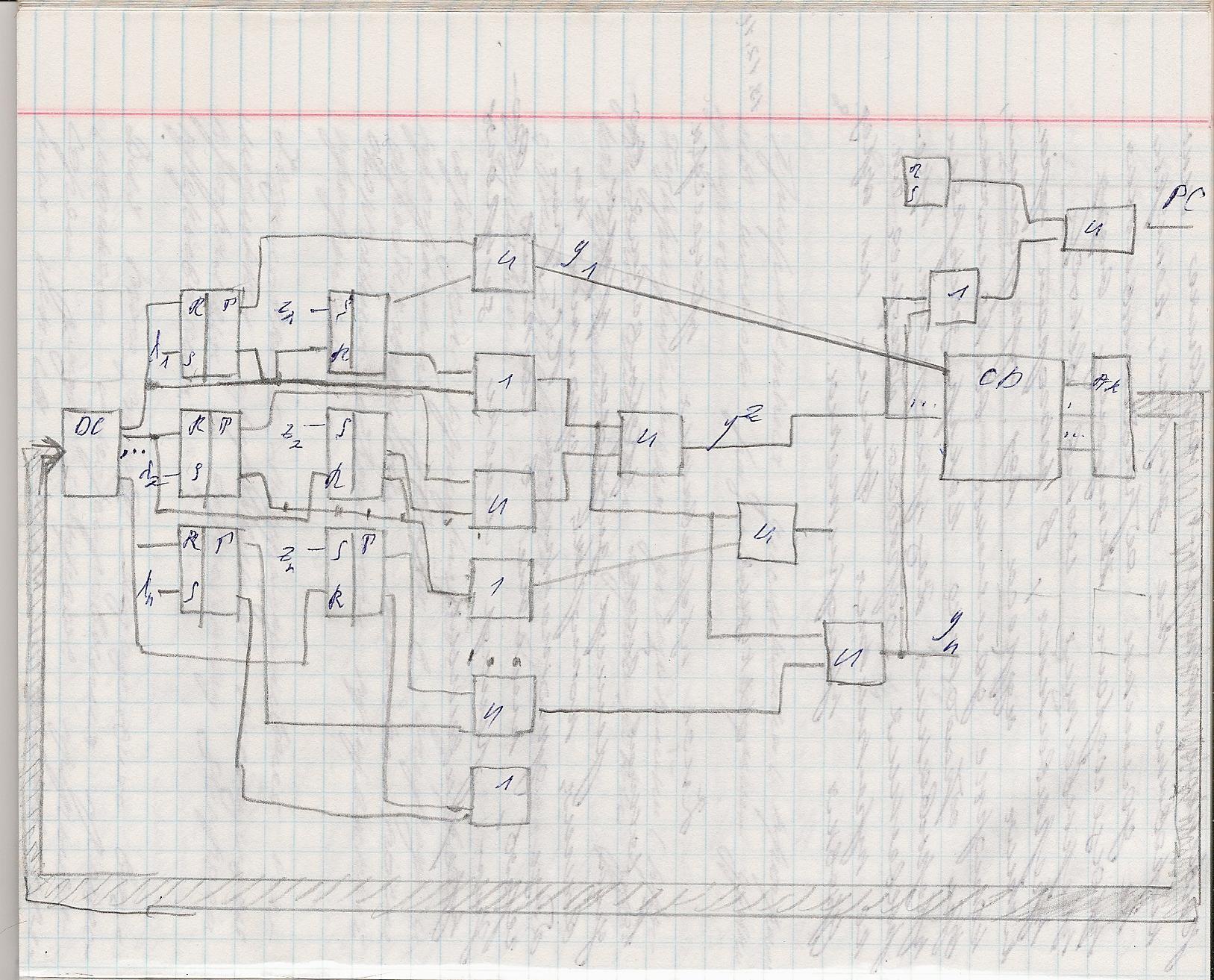

40) Блок прерываний процессора

В состав блока прерывания входит регистр запроса прерывания, который строится на базе однотактных RS – триггеров также входит в регистр маски запросов прерывания.

1-ый блок триггеров – регистр запроса прерывания;

2-ой блок триггеров – SZ – регистр маски запроса прерывания;

3-ий блок триггеров – сигнал выработки запроса прерывания;

ДС – дешифратор; СД – шифратор; РгК – регистр команд.

На входы «S» регистра запроса прерывания подается запрос прерывания α1-αn

на вход S регистра маски подается программно - формируемая маска прерывания ( Z1,...,Zn)

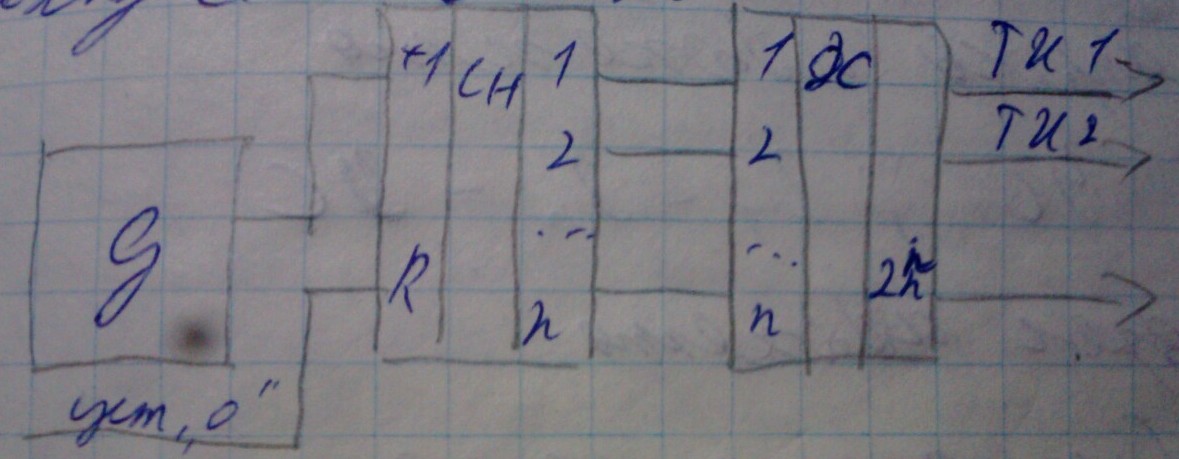

41) Блок синхронизации процессора.

БС состоит:

1) Генератор импульсов вырабатывающий УС.

2) Синхроимпульсы поступают на информационный вход суммирующего счетчика.

3) Выходы счетчика соединяются со входами дешифратора и в зависимости от кода слова на входе дешифратора формируется единичный импульс на одном из выходов дешифратора.

Этот импульс при подключении ко входам дешифратора задаётся порядок их работы.

Между бс и устройствами формируется серия синхроимпульсов на информационный вход счётчика.