- •Лекция №1 Определение распределенной информационно-вычислительной системы

- •1.1. Определение распределенной системы

- •1.2. Задачи

- •1.2.1. Соединение пользователей с ресурсами

- •1.2.2. Прозрачность

- •1.2.3. Открытость

- •1.2.4. Масштабируемость

- •1.3. Концепции аппаратных решений

- •1.3.1. Мультипроцессоры

- •1.3.2. Гомогенные мультикомпьютерные системы

- •1.3.3. Гетерогенные мультикомпьютерные системы

- •1.4. Концепции программных решений

- •1.4.1. Распределенные операционные системы

- •1.4.2. Сетевые операционные системы

- •1.4.3. Программное обеспечение промежуточного уровня

- •1.5. Модель клиент-сервер

- •1.5.1. Клиенты и серверы

- •1.5.2. Разделение приложений по уровням

- •1.5.3. Варианты архитектуры клиент-сервер

- •1.6. Итоги

- •Вопросы и задания

- •Содержание

1.3.1. Мультипроцессоры

Мультипроцессорные системы обладают одной характерной особенностью: все процессоры имеют прямой доступ к общей памяти. Мультипроцессорные системы шинной архитектуры состоят из некоторого количества процессоров, подсоединенных к общей шине, а через нее — к модулям памяти. Простейшая конфигурация содержит плату с шиной или материнскую плату, в которую вставляются процессоры и модули памяти.

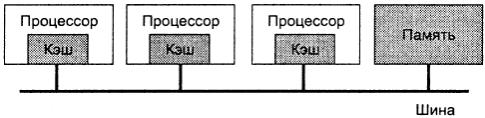

Поскольку используется единая память, когда процессор A записывает слово в память, а процессор В микросекундой позже считывает слово из памяти, процессор В получает информацию, записанную в память процессором А. Память, обладающая таким поведением, называется согласованной (coherent). Проблема такой схемы состоит в том, что в случае уже 4 или 5 процессоров шина оказывается стабильно перегруженной и производительность резко падает. Решение состоит в размещении между процессором и шиной высокоскоростной кэш-памяти (cache memory), как показано на рис. 1.5. В кэше сохраняются данные, обращение к которым происходит наиболее часто. Все запросы к памяти происходят через кэш. Если запрошенные данные находятся в кэш-памяти, то на запрос процессора реагирует она и обращения к шине не выполняются. Если размер кэш-памяти достаточно велик, вероятность успеха, называемая также коэффициентом кэш- попаданий (hit rate), велика и шинный трафик в расчете на один процессор резко уменьшается, позволяя включить в систему значительно больше процессоров. Общепринятыми являются размеры кэша от 512 Кбайт до 1 Мбайт, коэффициент кэш-попаданий при этом обычно составляет 90 % и более.

Рис. 1.5. Мультипроцессорная система с шинной архитектурой

Однако введение кэша создает серьезные проблемы само по себе. Предположим, что два процессора, A и B, читают одно и то же слово в свой внутренний кэш. Затем A перезаписывает это слово. Когда процессор B в следующий раз захочет воспользоваться этим словом, он считает старое значение из своего кэша, а не новое значение, записанное процессором A. Память стала несогласованной, и программирование системы осложнилось. Кэширование, тем не менее, активно используется в распределенных системах, и здесь мы вновь сталкиваемся с проблемами несогласованной памяти. Мы вернемся к проблемам кэширования и согласованности в главе 6.

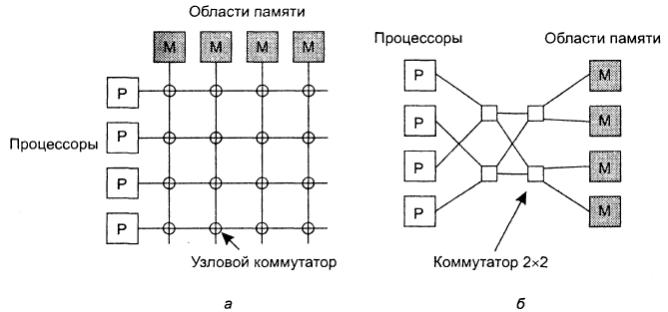

Проблема мультипроцессорных систем шинной архитектуры состоит в их ограниченной масштабируемости, даже в случае использования кэша. Для построения мультипроцессорной системы с более чем 256 процессорами для соединения процессоров с памятью необходимы другие методы. Один из вариантов — разделить общую память на модули и связать их с процессорами через коммутирующую решетку (crossbar switch), как показано на рис. 1.6, а. Как видно из рисунка, с ее помощью каждый процессор может быть связан с любым модулем памяти. Каждое пересечение представляет собой маленький электронный узловой коммутатор (crosspoint switch), который может открываться и закрываться аппаратно. Когда процессор желает получить доступ к конкретному модулю памяти, соединяющие их узловые коммутаторы мгновенно открываются, организуя запрошенный доступ. Достоинство узловых коммутаторов в том, что к памяти могут одновременно обращаться несколько процессоров, хотя если два процессора одновременно хотят получить доступ к одному и тому же участку памяти, то одному из них придется подождать.

Рис. 1.6. Коммутирующая решетка (а). Коммутирующая омега-сеть (б)

Недостатком коммутирующей решетки является то, что при наличии п процессоров и п модулей памяти нам потребуется n2 узловых коммутаторов. Для больших значений п это число может превысить наши возможности. Обнаружив это, человечество стало искать и нашло альтернативные коммутирующие сети, требующие меньшего количества коммутаторов. Один из примеров таких сетей — омега-сеть (omega network), представленная на рис. 1.6, б. Эта сеть содержит четыре коммутатора 2x2, то есть каждый из них имеет по два входа и два выхода. Каждый коммутатор может соединять любой вход с любым выходом. Если внимательно изучить возможные положения коммутаторов, становится ясно, что любой процессор может получить доступ к любому блоку памяти. Недостаток коммутирующих сетей состоит в том, что сигнал, идущий от процессора к памяти или обратно, вынужден проходить через несколько коммутаторов. Поэтому, чтобы снизить задержки между процессором и памятью, коммутаторы должны иметь очень высокое быстродействие, а дешево это не дается.

Люди пытаются уменьшить затраты на коммутацию путем перехода к иерархическим системам. В этом случае с каждым процессором ассоциируется некоторая область памяти. Каждый процессор может быстро получить доступ к своей области памяти. Доступ к другой области памяти происходит значительно медленнее. Эта идея была реализована в машине с неунифицированным доступом к памяти (NonUniform Memory Access, NUMA). Хотя машины NUMA имеют лучшее среднее время доступа к памяти, чем машины на базе омега-сетей, у них есть свои проблемы, связанные с тем, что размещение программ и данных необходимо производить так, чтобы большая часть обращений шла к локальной памяти.