- •Введение

- •Раздел «Создание и эволюция эвм» Глава 1. Научные предпосылки создания эвм

- •Управление и информация

- •Информация и ее свойства

- •Экономическая информация

- •Три формы адекватности информации

- •Меры информации

- •Синтаксические меры информации

- •Семантическая мера информации

- •Прагматическая мера информации

- •Показатели качества информации

- •Репрезентативность

- •Содержательность

- •Достаточность

- •Доступность

- •Актуальность

- •Своевременность

- •Точность

- •Достоверность

- •Устойчивость

- •Защищенность

- •Полезность

- •Информатика

- •Наука информатика

- •Информационные технологии

- •Индустрия информатики

- •Вопросы для самопроверки

- •Глава 2. История создания вычислительной техники

- •Механические счетные машины

- •Электромеханические счетные машины

- •Электронные вычислительные машины

- •Вопросы для самопроверки

- •Глава 3. Эволюция эвм

- •Вопросы для самопроверки

- •Глава 4. Основные классы вычислительных машин

- •Большие компьютеры

- •Серверы и рабочие станции

- •Рабочие станции

- •Серверы

- •Малые компьютеры

- •Микрокомпьютеры

- •Персональные компьютеры

- •Наколенные компьютеры

- •Компьютеры-блокноты (ноутбуки)

- •Нетбуки

- •Планшетные компьютеры

- •Райтеры

- •Электронные книги Ридеры

- •Карманные компьютеры

- •Периферийные устройства кпк

- •Коммуникаторы (смартфоны)

- •Электронные секретари

- •Электронные записные книжки

- •Вычислительные системы

- •Многомашинные и многопроцессорные вс

- •Высокопараллельные многопроцессорные вычислительные системы

- •Ассоциативные и потоковые вс

- •Ассоциативные вычислительные системы

- •Потоковые вычислительные системы

- •Суперкомпьютеры

- •Кластерные суперкомпьютеры

- •Вопросы для самопроверки

- •Раздел 2. «Информационно-логические основы построения эвм» Глава 5. Представление информации в эвм

- •Представление чисел с фиксированной и плавающей запятой

- •Алгебраическое представление двоичных чисел

- •Прочие системы счисления

- •Двоично-десятичная система счисления

- •Шестнадцатеричная система счисления

- •Выполнение арифметических операций в компьютере

- •Особенности выполнения операций над числами с плавающей запятой

- •Выполнение арифметических операций над числами, представленными в дополнительных кодах

- •Особенности выполнения операций в обратных кодах

- •Выполнение арифметических операций в шестнадцатеричной системе счисления

- •Особенности представления информации в пк

- •Вопросы для самопроверки

- •Глава 6. Логические основы построения эвм

- •Основы алгебры логики

- •Логический синтез вычислительных схем

- •Электронные технологии и элементы

- •Полевые транзисторы

- •Планарные микросхемы

- •Электронные и логические схемы

- •Триггер

- •Регистр

- •Дешифратор

- •Логические операции, выполняемые в компьютере

- •Or (или) — логическое сложение

- •Xor (исключающее или)

- •Not (не) — операция отрицания

- •Вопросы для самопроверки

- •Раздел 3 Архитектура персонального компьютера Глава 7. Основные блоки эвм и их назначение

- •Структурная схема эвм

- •Микропроцессор

- •Системная шина

- •Основная память

- •Внешняя память

- •Источник питания

- •Внешние устройства

- •Дополнительные интегральные микросхемы

- •Элементы конструкции пк

- •Функциональные характеристики эвм

- •Производительность, быстродействие, тактовая частота

- •Разрядность микропроцессора и кодовых шин интерфейса

- •Типы системного и локальных и внешних интерфейсов

- •Емкость оперативной памяти

- •Виды накопителей на жестких магнитных дисках

- •Тип и емкость накопителей на гибких магнитных дисках

- •Наличие, виды и емкость кэш-памяти

- •Аппаратная и программная совместимость с другими типами компьютеров

- •Возможность работы в многозадачном режиме

- •Надежность

- •Глава 8. Микропроцессоры

- •Микропроцессоры типа cisc

- •Микропроцессоры Over Drive

- •Микропроцессоры Pentium

- •Микропроцессоры Pentium Pro

- •Микропроцессоры Pentium mmx и Pentium II

- •Микропроцессоры Pentium III

- •Микропроцессоры Pentium 4

- •Эффективные технологии в мп Intel

- •Архитектура Intel Net Burst

- •Многоядерные микропроцессоры

- •Микропроцессоры линейки core

- •Процессоры Core Penryn

- •Микропроцессоры типа risc

- •Микропроцессоры типа vliw

- •Физическая и функциональная структура микропроцессора

- •Устройство управления

- •Арифметико-логическое устройство

- •Микропроцессорная память

- •Универсальные регистры

- •Сегментные регистры

- •Регистры смещений

- •Регистр флагов

- •Статусные флаги

- •Управляющие флаги

- •Интерфейсная часть мп

- •Вопросы для самопроверки

- •Глава 9. Системные платы и чипсеты

- •Разновидности системных плат

- •Чипсеты системных плат

- •Чипсет i965 (Broadwater)

- •Глава 10. Интерфейсная система пк

- •Шины расширений

- •Локальные шины

- •Интерфейсы pci

- •Интерфейс agp

- •Периферийные шины

- •Интерфейсы ide/ata

- •Интерфейс scsi

- •Интерфейс rs 232

- •Интерфейс ieee 1284

- •Универсальные последовательные интерфейсы

- •Последовательная шина usb

- •Стандарт ieee 1394

- •Последовательный интерфейс sata

- •Последовательный интерфейс sas

- •Семейство последовательных интерфейсов pci Express

- •Прикладные программные интерфейсы

- •Беспроводные интерфейсы

- •Интерфейсы IrDa

- •Интерфейс Bluetooth

- •Интерфейс wusb

- •Семейство интерфейсов WiFi

- •Семейство интерфейсов WiMax

- •Интерфейс WiBro

- •Прочие интерфейсы

- •Вопросы для самопроверки

- •Глава 11. Основная память пк

- •Статическая и динамическая оперативная память

- •Основная память

- •Физическая структура основной памяти

- •Оперативные запоминающие устройства

- •Виды модулей оперативной памяти

- •Типы оперативной памяти

- •Постоянные запоминающие устройства

- •Логическая структура основной памяти

- •Вопросы для самопроверки

- •Глава12. Внешние запоминающие устройства

- •Размещение информации на дисках

- •Адресация информации на диске

- •Накопители на жестких магнитных дисках

- •0,85" Винчестеры Toshiba

- •Дисковые массивы raid

- •Накопители на гибких магнитных дисках

- •Накопители на оптических дисках

- •Неперезаписываемые оптические диски cd-rom

- •Оптические диски с однократной записью

- •Оптические диски с многократной записью

- •Оптические универсальные диски dvd

- •Маркировка скоростных характеристик cd и dvd

- •Эффективные технологии хранения информации на cd и dvd

- •Многослойный cd

- •Millipede-диск

- •Флуоресцентные оптические диски

- •Особенности организации флуоресцентных дисков

- •Прочие технологии

- •Накопители на магнитооптических дисках

- •Накопители на магнитной ленте

- •Устройства флэш-памяти

- •Твердотельные накопители на базе флэш-памяти

- •Вопросы для самопроверки

- •Глава 13. Видеотерминальные устройства

- •Видеомониторы на элт

- •Монохромные мониторы

- •Цветные мониторы

- •Виды развертки изображения на мониторе

- •Цифровые и аналоговые мониторы

- •Размер экрана монитора

- •Вертикальная (кадровая) развертка

- •Строчная развертка

- •Разрешающая способность мониторов

- •Частотная полоса пропускания

- •Эргономичность электронно-лучевых мониторов

- •Видеомониторы на плоских панелях

- •Мониторы на жидкокристаллических индикаторах

- •Tmos – мониторы

- •Плазменные мониторы

- •Электролюминесцентные мониторы

- •Светоизлучающие мониторы

- •Мониторы на основе «электронной бумаги»

- •Стереомониторы

- •Видеоконтроллеры

- •Вопросы для самопроверки

- •Глава 14. Внешние устройства пк

- •Клавиатура

- •Графический манипулятор мышь

- •Принтеры

- •Матричные принтеры

- •Струйные принтеры

- •Лазерные принтеры

- •Термопринтеры

- •Твердочернильные принтеры

- •Сервисные устройства

- •Сетевые принтеры

- •С канеры

- •Типы сканеров

- •Форматы представления графической информации в пк

- •Форматы растровой графики

- •Д игитайзеры

- •Основные характеристики дигитайзеров

- •Плоттеры

- •Типы плоттеров

- •Вопросы для самопроверки

- •Глава 15. Средства мультимедиа

- •Системы речевого ввода и вывода информации

- •Системы распознавания речи

- •Системы, ориентированные на распознавание отдельных слов, команд и вопросов

- •Системы распознавания предложений и связной речи

- •Системы идентификации по образцу речи

- •Механизм распознавания речи

- •Системы синтеза речи

- •Компьютерные средства обеспечения звуковых технологий

- •Звуковые платы (карты)

- •Компьютерные средства обеспечения видеотехнологий

- •Вопросы для самопроверки

- •Раздел 4. Компьютерные сети Глава 16. Основы построения компьютерных сетей

- •Классификация и архитектура компьютерных сетей

- •Виды компьютерных сетей

- •Модель взаимодействия открытых систем

- •Локальные вычислительные сети

- •Виды локальных вычислительных сетей

- •Одноранговые локальные сети

- •Серверные локальные сети

- •Корпоративные компьютерные сети

- •Глобальная информационная сеть Интернет

- •Протоколы, используемые в сети

- •Программное обеспечение компьютерных сетей

- •Информационное обеспечение сетей

- •Вопросы для самопроверки

- •Глава 17.Техническое обеспечение компьютерных сетей

- •Серверы и рабочие станции

- •Рабочие станции

- •Серверы

- •Маршрутизаторы и коммутирующие устройства

- •Методы коммутации

- •Коммутация сообщений

- •Коммутация пакетов

- •Методы маршрутизации

- •Варианты адресации компьютеров в сети

- •Методы маршрутизации, используемые в сетях

- •Модемы и сетевые карты

- •Модемы для аналоговых каналов связи

- •Протоколы передачи данных

- •Модемы для цифровых каналов связи

- •Сетевые карты

- •Линии и каналы связи

- •Цифровые каналы связи

- •Раздел 5. Программное управление Глава 18. Программное управление — основа автоматизации вычислительного процесса После изучения главы вы должны знать:

- •Алгоритмы и языки программирования

- •Состав машинных команд

- •Пример программы на яск

- •Программное обеспечение компьютера

- •Системное программное обеспечение

- •Операционные системы компьютеров

- •Прикладное программное обеспечение

- •Прикладные программы для офиса

- •Корпоративные прикладные программы

- •Режимы работы компьютеров

- •Однопрограммный режим

- •Многопрограммный режим

- •Система прерываний программ в пк

- •Адресация регистров и ячеек памяти в пк

- •Относительная адресация

- •Стековая адресация

- •Вопросы для самопроверки

- •Глава 19.Элементы программирования на языке Ассемблер

- •Основные компоненты языка ассемблер Алфавит языка

- •Константы (числа и строки) Только целые числа

- •Строки (литералы)

- •Команды (операторы)

- •Директивы (псевдооператоры)

- •Модификаторы

- •Адресация регистров и ячеек памяти в Ассемблере

- •Непосредственная адресация

- •Прямая адресация регистров мпп

- •Адресация ячеек оп

- •Основные команды языка ассемблер

- •Команды пересылки данных

- •Арифметические команды

- •Команды сложения, вычитания и сравнения

- •Команды приращения

- •Команды умножения

- •Команды деления

- •Логические команды

- •Команды безусловной передачи управления

- •Команды перехода к подпрограмме и выхода из подпрограммы

- •Команда перехода к подпрограмме: call opr

- •Команда выхода из подпрограммы

- •Команды условной передачи управления

- •Команды условной передачи управления для беззнаковых данных

- •Команды условной передачи управления для знаковых данных

- •Команды условной передачи управления для прочих проверок

- •Команды управления циклами

- •Команды прерывания

- •Основные директивы ассемблера

- •Директивы определения идентификаторов

- •Директивы определения данных

- •Директивы определения сегментов и процедур

- •Директивы управления трансляцией

- •Программирование процедур работы с устройствами ввода-вывода

- •Программирование работы с дисплеем

- •Видеооперации с прерыванием 21h dos

- •Программирование работы с клавиатурой

- •Некоторые аспекты создания исполняемых программ

- •Процедуры формирования программы

- •Структура программы на языке ассемблера для создания файла exe

- •Программа вычисления квадратного корня

- •Основные сведения о листинге программы

- •Последовательность работы пк при выполнении программы

- •Краткие сведения об отладчике программ debug

- •Основные команды отладчика debug

- •Вопросы для самопроверки

- •Заключение. Перспективы развития информационных систем

- •Литература

Триггер

Среди

многих элементарных схем в компьютере

наибольшее распространение получила

схема триггера

– статического запоминающего и

логического элемента. На триггерах

строятся системы статической памяти,

регистры, счетчики, делители частоты и

еще множество других компьютерных схем.

Триггер – элемент, который может

находиться в одном из двух устойчивых

состояний, условно именуемых состояниями

«0» и «1». Триггер имеет также два выхода:

выход «0» (иногда именуемый

-выходом),

выход «1» (именуемый иногда q-выходом).

Если триггер находится в состоянии «0»,

то у него на выходе q «высокое» напряжение

(порядка нескольких вольт или даже

меньше), на выходе

низкое

(обычно нулевое) напряжение, если триггер

находится в состоянии «0», то напряжения

распределены наоборот.

-выходом),

выход «1» (именуемый иногда q-выходом).

Если триггер находится в состоянии «0»,

то у него на выходе q «высокое» напряжение

(порядка нескольких вольт или даже

меньше), на выходе

низкое

(обычно нулевое) напряжение, если триггер

находится в состоянии «0», то напряжения

распределены наоборот.

Триггера могут иметь раздельные входы: R (Reset) — вход установки «0», S (Set) — вход установки «1». Каждый вход устанавливает триггер в соответствующее состояние, такие триггеры часто называют R-S триггерами.

Триггеры могут иметь счетный вход T (toggle, релаксатор), очередной импульс «1» на счетном входе изменит состояние триггера. Такие триггеры часто называют T-триггерами. Триггер, установленный в какое либо состояние, сохраняет его до тех пор, пока импульс, поданный на один из входов, не изменит это состояние. Логические схемы R-S триггера (a) и T триггера (b) показаны на рис.6.11.

Рис. 6.11 Логические схемы R-S триггера (a) и T триггера (b)

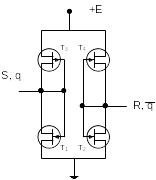

Проследив напряжения на входах и выходах триггера можно видеть, что состояние триггера статически поддерживается его напряжениями. Например, сигнал «1», поступивший на вход S, на выходе триггера установит низкое напряжение, поступающее оттуда на вход R, и будет восприниматься как сигнал установки триггера в состояние «0». Аналогичная картина наблюдается при установке триггера в состояние «0: высокое напряжение, поступающее в этом случае с выхода на вход R будет поддерживать триггер в состоянии «0». При подаче импульса «1» на счетный вход T этот импульс пройдет только через тот вентиль (схему «AND»), который пропускает его на раздельный вход, переключающий триггер. Например, если триггер находится в состоянии «1», при поступлении импульса на вход T будет открыт вентиль, пропускающий импульс на вход R, и триггер переключится в состояние «0». Принципиальная электрическая КМОП схема R-S триггера, выполненного по транзисторно-транзисторной технологии, показана на рис. 6.12.

Рис. 6.12 R-S триггер на КМОП транзисторах

Триггера используются при организации запоминающих регистров и счетчиков. При этом в регистрах обычно используются триггера с раздельными входами, а в счетчиках – со счетными. Считывание информации с триггеров обычно выполняется с помощью схем AND.

Регистр

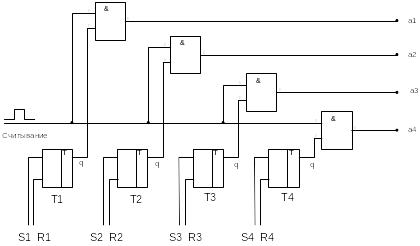

Логическая схема 3-х разрядного регистра с вентилями (схемами «AND») для ввода и считывания информации показана на рис. 6.13.

Рис. 6.13 Логическая схема регистра

В каждом i-м разряде регистр содержит R-S триггер Тi и подключенную к нему для считывания информации схему AND-вентиль. Считывание информации из регистра при подаче импульса считывания, опрашивающего схемы «AND» всех триггеров, на разрядные выходы ai поступит «1» через те вентили, триггера которых были в состоянии «1». Запись информации в регистр может выполняться в однотактном или двухтактном режимах. В однотактном режиме на соответствующий вход каждого триггера подается «1». В двухтактном режиме все входы R всех триггеров подключаются к одному проводу установки «0», по которому сначала все триггеры обнуляются, а затем на входы S тех триггеров, которые нужно установить в «1», подается соответствующий импульс.

Счетчик

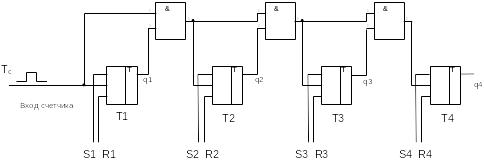

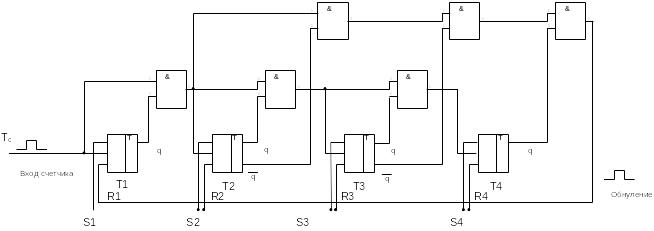

На рис. 6.14 показана логическая схема 4-х разрядного двоичного счетчика. Этот счетчик 16-м импульсом сбрасывается в 0.

Рис. 6.14 Логическая схема двоичного счетчика

На счетный вход каждого следующего триггера через вентили пройдет импульс со входа счетчика только, если все предыдущие триггера стояли в состоянии «1». На рис. 6.15 показана логическая схема десятичной тетрады двоично-десятичного счетчика – он представляет собой двоичный счетчик с циклом обнуления через 10 импульсов (считает от 0 до 9).

Рис. 6.15 Логическая схема тетрады двоично-десятичного счетчика

Импульс обнуления счетчика формируется от каждого 10-го импульса, поступающего на вход счетчика (при наличии в счетчике кода 1001, то есть 9). Запись информации в счетчик не через счетный вход и считывание показаний счетчика выполняется так же, как в двоичном регистре.