- •Структура эвм

- •Структура машинного цикла

- •Структура и типы команд

- •3Х адресные команды

- •2Х адресные команды

- •1О адресные команды

- •Процессоры семейства pdp-11. Вычислительные системы параллельной обработки данных. Параллельная обработка как архитектурный способ повышения производительности.

- •Преимущества параллельной архитектуры:

- •Классификация систем параллельной обработки данных.

- •Классификация мультипроцессорных систем по способу организации основной памяти.

- •Мультипроцессорные системы с распределительной памятью

- •Топология из 4х процессорных блоков. Двумерный гиперкуб.

- •Способы организации внутренней памяти мультипроцессорных систем.

- •Топология внутренних связей многопроцессорных систем.

- •Сеть связи через общую шину.

- •Общая шина с арбитром.

- •Кольцевая структура.

- •Связи типа «звезда».

- •Улучшение возможностей связывания между процессорами.

- •Коммутаторы внутренних связей.

- •Однокаскадный коммутатор «Тасовка».

- •Многокаскадная коммутирующая сеть «Омега».

- •Состояние производства использования высокопроизводительных вычислительных систем.

- •Развитие архитектурных систем с общей разделяемой памятью.

- •Шина слежения за когерентностью данных.

- •Мультипроцессорная система Power Scale.

- •Архитектура вычислительных систем с распределенной разделяемой памятью.

- •Архитектура numa.

- •Развитие архитектуры мп для высокопроизводительных вычислительных систем.

- •Увеличение состава и числа функциональных устройств.

- •Интеграция функции.

- •Тенденция изменения архитектуры систем параллельной обработки на кристалле.

- •Вычислительные системы на кристалле.

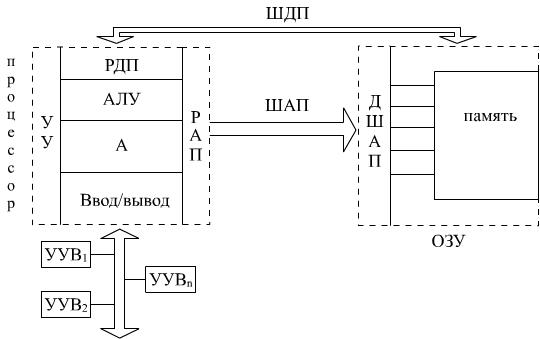

Структура эвм

В современных компьютерах реализуется Фан Теймана. В этой концепции архитектура ЭВМ поддерживает следующие принципы:

-

Двоичное кодирование внутреннего содержания.

-

Программное управление работы машины.

-

Однородность использованной памяти.

-

Адресуемая память.

В классическом случае машина по принципам Фан Теймана содержит следующие блоки:

-

Оперативная память.

-

Арифметико-логическое устройство.

-

Устройство управления.

-

Устройство ввода/вывода.

Структурная схема

ЭВМ в этом случае имеет след вид:

Оперативная память предназначена для хранения, как команд, так и данных, представляющие собой двоичные коды и на первый взгляд не различимы. Это принципиально важно, поскольку позволяет иметь память с единой адресацией, что позволяет упростить программирование.

АЛУ – арифметико-логическое устройство

УУ – устройство управления

РАП – регистр адреса памяти

ШАП – шина адреса памяти

РДП – регистр данных памяти

ДАП – дешифратор адреса памяти

Блок управления формирует сигналы управления (последовательность микроопераций) для выполнения команд программирования.

Регистр адреса памяти содержит адрес той ячейки, в которой будет происходить обращение в данный момент. Выбор этой ячейки по адресу осуществляется с помощью дешифратора адреса памяти. Обмен данными (и командами) между процессором и памятью осуществляется по шине данных в памяти. Этот обмен происходит через регистр данных в памяти.

Любая ЭВМ работает синхронно с поступлением тактовых импульсов от внутреннего генератора. Выполнение программы является сложным процессом и поэтому на её выполнение требуется несколько периодов тактовых импульсов. Время выполнения команды называется циклом. Если команда простая, то она выполняется за один машинный цикл, а если сложная, то может потребоваться несколько машинных циклов.

Структура машинного цикла

Машинный цикл схематично можно представить следующим образом:

Совокупность цикла выборки и исполнительного цикла составляет машинный цикл.

Структура и типы команд

Для работы компьютера команда задает операцию и те данные, над которыми эта операция должна быть выполнена. Обычно тип операции задаётся кодом внутри команды. Также внутри команды задаются тем или иным способом операнды, т.е. в общем случае команда задает следующие условия: какую выполнить операцию, с какими операндами её выполнить и куда поместить результат? Информация по каждому из этих разделов задается в команде в специальном коде. В общем случае команда состоит из следующих полей:

![]()

Регистр команд служит для хранения команды в процессе её дешифрации и выполнения. К каждому полю регистра команд подключен свой дешифратор.

На выходе дешифратора в зависимости от кода операции появляется сигнал, который запускает соответствующую цепочку действий по выполнению операции. Код способа адресации и код адреса операнда с помощью операндов позволяют вычислить физические адреса операнда.

В случае 2х местной операции, т.е. операции с двумя операндами, команда должна задавать:

-

Операцию

-

Адрес 1го операнда

-

Адрес 2го операнда

-

Адрес сохранения адресата

-

Адрес следующей команды

Если все эти адреса задать в явном виде, то команда будет иметь следующие поля:

![]()

Чтобы иметь возможность строить длинные программы, эти поля адресов должны иметь достаточное количество разделов. Поскольку современные ЭВМ должны иметь 16р., 32р., 64р., то длинная команда не укладывается в одномашинное слово 16разрядов, т.е. необходимо будет размещать машинную команду в несколько машинных слов и соответственно в несколько ячеек памяти, т.е. резко удлиняется процесс выборки команд, а следовательно падает быстродействие ЭВМ.

Существует несколько способов, которые позволяют сократить длину команды.