- •Структура эвм

- •Структура машинного цикла

- •Структура и типы команд

- •3Х адресные команды

- •2Х адресные команды

- •1О адресные команды

- •Процессоры семейства pdp-11. Вычислительные системы параллельной обработки данных. Параллельная обработка как архитектурный способ повышения производительности.

- •Преимущества параллельной архитектуры:

- •Классификация систем параллельной обработки данных.

- •Классификация мультипроцессорных систем по способу организации основной памяти.

- •Мультипроцессорные системы с распределительной памятью

- •Топология из 4х процессорных блоков. Двумерный гиперкуб.

- •Способы организации внутренней памяти мультипроцессорных систем.

- •Топология внутренних связей многопроцессорных систем.

- •Сеть связи через общую шину.

- •Общая шина с арбитром.

- •Кольцевая структура.

- •Связи типа «звезда».

- •Улучшение возможностей связывания между процессорами.

- •Коммутаторы внутренних связей.

- •Однокаскадный коммутатор «Тасовка».

- •Многокаскадная коммутирующая сеть «Омега».

- •Состояние производства использования высокопроизводительных вычислительных систем.

- •Развитие архитектурных систем с общей разделяемой памятью.

- •Шина слежения за когерентностью данных.

- •Мультипроцессорная система Power Scale.

- •Архитектура вычислительных систем с распределенной разделяемой памятью.

- •Архитектура numa.

- •Развитие архитектуры мп для высокопроизводительных вычислительных систем.

- •Увеличение состава и числа функциональных устройств.

- •Интеграция функции.

- •Тенденция изменения архитектуры систем параллельной обработки на кристалле.

- •Вычислительные системы на кристалле.

Развитие архитектуры мп для высокопроизводительных вычислительных систем.

Основные характерные способы повышения производительности:

-

увеличение ёмкости и памяти внутри кристалла;

-

увеличение состава и числа функционирующих устройств.

Рассмотрим организацию внутрикристальной памяти. Традиционно такая память включает регистры процессора и встроенную КЭШ память одного, либо двух уровней. В последних разработках, кроме встроенных КЭШей, на кристалл размещают динамическую память DRAM. Такая память используется не только как буфер, но и как часть рабочей операционной памяти. Фирмой IMB на кристалле достигнут размер памяти 16мб, со скоростью обмена с ядром процессора 50гб в сек, но при этом малая память занимает всего лишь 20% площади кристалла.

Существенной частью внутрикристаллической памяти процессора является его регистры. В архитектуре имеется не один, а несколько регистровых наборов (регистровых файлов). Каждый регистровый файл обслуживает один вычислительный процесс, т.е. поток команд. Этот поток называется Тред- Tred. В общем случае в каждом процессоре может быть n-регистровых файлов. В каждом такте происходит переключение процессора на работу к очередным регистрам файла. Поэтому запрос, выданный в ОП, может обрабатываться в течении n-1 такта вплоть до того момента времени, пока процессор не вернется на начальный регистровый файл. Выбор значения n определяется соотношением времени доступа в память ко времени выполнения команд.

Увеличение состава и числа функциональных устройств.

С ростом уровня интеграции возникает задача распределения дополнительных ресурсов на кристалле между функциональными блоками системы. Хотя память и является ресурсом, не производящим вычисления, но размещение её на кристалле уменьшает задержки, связанные с изменениями из памяти затребованных данных и команд. За счет этого увеличение ёмкости памяти на кристалле дает прирост производительности системы. Однако, при достижении определенной ёмкости памяти, прирост производительности оказывается меньше, чем тот, который можно достичь за счет размещения на кристалле других функциональных модулей. В этом случае основная проблема заключается в том, что дополнительные функциональные узлы необходимо эффективно загружать.

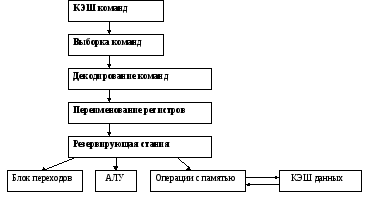

Параллельное выполнение команд в процессоре предполагает использование следующих механизмов:

- переименование регистров с целью устранения зависимостей ресурсов;

- предсказание – переход;

- динамическое назначение команд на исполнение параллельно-работающими процессов;

В некоторых МП системах динамическое назначение команд на исполнительные устройства осуществляет блок, который называется резервирующая станция. Этот блок состоит из совокупности элементов ассоциативной памяти. Каждый элемент этой станции содержит позиции для размещения следующих информации:

1) код операции, имя первого операнда, его значение, признаки доступности первого операнда;

2) имя второго операнда, его значения, признак доступности второго операнда;

3) имя регистра результата;

Схема организации динамического распределения:

Резервирующая станция работает следующим образом: когда завершается исполнение очередной команды и вырабатывается результат, то имя этого результата сравнивается с именами операндов в резервирующей станции. Если в резервирующей станции обнаруживается команда, которая ждет этого результата, то данные записываются в соответствующую позицию элемента ассоциативной памяти и устраняется признак их доступности. Когда у команды доступны все операнды - есть исполнение. Таким образом здесь используется механизм управления потоком команд, основанный на потоке данных.