7. Конструкторско-технологический раздел

7.1. Разработка функциональной схемы ацп

Задача АЦ- преобразователя состоит в преобразовании входного напряжения в пропорциональное ему число. При этом можно выделить три принципиально различных метода:

параллельный,

весовой (последовательных приближений),

числовой.

В первом случае входное напряжение одновременно сравнивают с n опорными напряжениями и точно определяют, между какими двумя уровнями оно лежит. При этом результат получают в один шаг. Конечно, аппаратурные затраты в этом случае очень велики, так как для каждого возможного числа необходим компаратор. Для области измерений от 0 до 100 с единичным шагом необходимо, следовательно, 100 компараторов.

При весовом (последовательных приближений) методе результат не может быть получен за один шаг, поскольку на каждом шаге определяется лишь один разряд двоичного числа. Сначала устанавливают, превышает ли входное напряжение опорное напряжение старшего разряда. Если оно выше, то старший разряд получает значение «1» и из входного напряжения вычитается опорное. Остаток сравнивают с соседним младшим разрядом и т. д. Очевидно, что для этого необходимо столько шагов сравнения, сколько разрядов в числе и сколько опорных напряжений.

Простейший метод- числовой. В этом случае подсчитывается число суммирований опорного напряжения младшего разряда, необходимое для получения входного напряжения. Если максимальное число, которое может быть представлено, равно n, то необходимо,. следовательно, максимум n шагов для получения результата. В Таблице 7.1 приведены важнейшие характеристики всех способов. На практике часто используют комбинации различных способов.

Таблица 7.1. Сравнение различных методов АЦ преобразований.

|

Метод |

Число шагов |

Число источников опорного напряжения |

Примечание |

|

Параллельный |

1 |

n |

Большие аппаратурные затраты |

|

Весовой |

1d n |

1d n |

|

|

Числовой |

n |

1 |

Простой, медленный |

При разработке схемы АЦП следует учитывать ряд факторов:

точность (разрядность АЦП - 12 разрядов (11+знак));

быстродействие;

точность установки;

необходимые питающие напряжения;

источник опорного напряжения;

диапазон аналогового напряжения (10в);

модуль должен работать в составе ПЭВМ IBM PC/AT или совместимых с ней ЭВМ;

модуль должен обеспечивать обмен информацией с IBM PC/AT через интерфейс AT-BUS в режиме программной передачи;

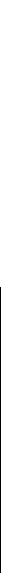

формат данных, передаваемых через интерфейс AT-BUS при записи 16-ти разрядное слово со знаком. Отрицательные значения представлены в дополнительном коде.

Формат слова

данных

Рисунок 7.1

Можно насчитать с полдюжины основных способов А/Ц- преобразования, каждый из которых обладает своими преимуществами и ограничениями. В нашем случае мы применим наиболее широко распространенные типы преобразователя: последовательных приближений.

Метод последовательных приближений популярен вследствие того, что объединяет разрешающую способность до 12 разрядов и выше с исключительно малым временем преобразования (менее 12 мкс для преобразования 12 разрядов). Достоинством этого метода является также и то, что время преобразования фиксировано и не зависит от амплитуды входного сигнала, что позволяет преобразователю эффективно взаимодействовать с микропроцессором. К недостаткам метода можно отнести его восприимчивость к изменению входного сигнала во время преобразования (включая шум) и более высокую стоимость преобразователя в пересчете на разряд, чем при использовании АЦП с интегрированием.

Последовательные приближения аналогичны взвешиванию массы на точных весах при использовании гирь с заранее известной массой, которые образуют двоичную (или двоично-десятичную) последовательность. Каждую "гирю" добавляют по очереди "на весы", начиная с самой тяжелой. Если ее масса выходит за пределы шкалы, то ее удаляют, если нет — оставляют. Затем пробуют следующую гирю и т. д. После того как испробованы все гири, сумма весов оставшихся на весах гирь представляет собой точное значение неизвестного веса. Если шкала смещена на 1/2 МР (т.е. первый переход происходит при +1/2 МР вместо нуля), сумма весов, оставшихся на весах, оказывается в пределах ± 1/2 МР правильного значения.

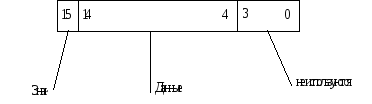

Преобразователь последовательных приближений содержит ЦАП, компаратор напряжения или тока, генератор тактовых импульсов, сдвиговый регистр, управляющую логическую цепь и выходной регистр (рис.7.2 ). Основным управляющим входом служит линия начала преобразования. Поскольку выходные данные неверны до тех пор, пока преобразование не закончено, линия состояния преобразования (или окончания преобразования) сигнализирует о том, что преобразователь "занят", пока осуществляется преобразование.

Схема АЦП

последовательных приближений

Рисунок 7.2

Обычно процесс начинается с установки всех разрядов в “0”. Затем, начиная со старшего значащего разряда, каждый разряд по очереди временно устанавливается в “1”. Если выходное напряжение ЦАП не превышает напряжения входного сигнала, то этот разряд остается в состоянии “1”, в противном случае он возвращается в “0”. Для n-разрядного АЦП потребуется n таких шагов. Происходящий процесс можно описать как процесс бинарного поиска, начинающегося с середины. А/Ц- модуль с последовательным приближением имеет вход «Начало преобразования» и выход «Конец преобразования». Цифровой выход всегда выдается в параллельной форме (все разряды сразу по n отдельным выходным линиям), а и в последовательной форме (n последовательных выходных битов, начиная с СЭР по одной выходной линии).

АЦП с последовательным приближением являются сравнительно точными и быстрыми и требуют всего n установок на ЦАП для обеспечения n-разрядной точности. Типичное время преобразованию колеблется в диапазоне от 1 мкс до 5 мкс (при точности от 8 до 12 разрядов) Этот тип преобразователя работает на коротких выборках из входного напряжения и если его входной сигнал меняется во время преобразования, то ошибка не превышает величину происходящего за это время изменения; однако выбросы на входном сигнале катастрофичны. Несмотря на общую вполне допустимую точность, эти преобразователи могут иметь довольно необычные нелинейности и «пропущенные коды»

При разработке схемы АЦП ставилась задача удовлетворить всем требованиям, предъявляемых техническим заданием. Наиболее важными из которых являются:

точность (разрядность АЦП - 12 разрядов (11+знак));

быстродействие;

необходимые питающие напряжения;

источник опорного напряжения;

диапазон аналогового напряжения (10в);

модуль должен обеспечивать обмен информацией с IBM PC/AT через интерфейс AT-BUS в режиме программной передачи;

Для обмена данными между ЦП и ОЗУ или адаптерами внешних устройств все компьютеры используют магистраль-набор обобщенных «линий» (проводников), по которым осуществляется обмен двоичными словами. (Многие магистрали допускают также обмен данными непосредственно между адаптерами внешних устройств, хотя такие возможности используются менее часто.) Использование магистрали с обобщенными линиями значительно упрощает меж соединения, поскольку в противном случае потребовались бы многожильные кабели, соединяющие каждую пару взаимодействующих друг с другом устройств. Магистраль состоит из набора линий данных (их обычно столько же, сколько разрядов (бит) ПЭВМ - 32), нескольких линий адреса для определения того, какое устройство будет «вещать», а какое «слушать», подключившись к соответствующим линиям, а также набора управляющих линий, которые определяют, какое действие выполняется (передача данных от или к ЦП, обработка прерывании, прямой доступ к ОЗУ я т.п.). Все линии данных, равно как и ряд других линий, являются двунаправленными - они либо подключены к выходу элементов с тремя состояниями, либо в некоторых случаях к открытому коллекторному выходу логических элементов с нагрузочными резисторами (эти резисторы обычно устанавливают на конце магистрали, при этом они дополнительно выполняют функцию согласования для уменьшения отражений сигналов в линиях магистрали), могут оказаться необходимыми и в случае применения устройств с тремя состояниями в том случае, когда магистраль имеет большую физическую длину.

Элементы с тремя состояниями или с открытым коллектором подключаются таким образом, чтобы их можно было перенести в отключенное состояние, поскольку при нормальной работе магистрали в каждый момент времени только одно устройство должно выставлять данные на соответствующие линии данных.

Для того чтобы переслать данные на магистраль с разделяемыми ресурсами (мультиплексируемую), необходимо описать сами данные, приемник, а также момент, когда данные являются достоверными. Таким образом, магистраль имеет шину данных (для передачи данных), адресную шину (для того чтобы идентифицировать устройство ввода-вывода или адрес в памяти) и несколько линий синхронизации, или стробирования (которые сообщают, когда передаются данные). Обычно в шине данных предусматривается столько же проводников, сколько разрядов в компьютерном слове, чтобы можно было сразу передать все слово. Однако в РС-AT есть только 16 проводников шины данных (D0-D15); за один цикл передачи можно переслать байт, но для того, чтобы переслать 32-разрядное слово, необходимо выполнить два цикла передачи. Количество разрядов шины адреса определяет количество адресуемых устройств. IВМ РС общается но своей магистрали как с памятью. Передаваемые данные синхронизуются стробирующими импульсами, передаваемыми по дополнительным проводникам магистрали. Для того чтобы реализовать описанную схему, существуют два пути: предусмотреть отдельные линии «чтение» и «запись» и возбуждать на той или другой нз этих линий сигналы, синхронизирующие передачу данных; иметь одну линию стробирующих сигналов (STROBE) и одну линию READ/WRITE, причем импульс на линии STROBE синхронизирует передачу данных в направлении, которое определяется уровнем сигнала на линии READ/WRITE. IВМ РС использует схему (действующий уровень сигнала низкий) с линиями “чтение/запись” названными IOR, IOW, MEMR и MEMW. Поскольку РС различает память и устройства ввода-вывода, то и линий этих четыре, по два строба (чтения и записи) на тот и другой тип ввода-вывода.

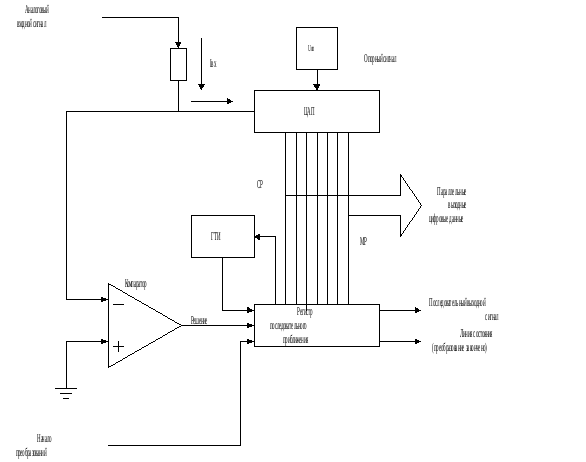

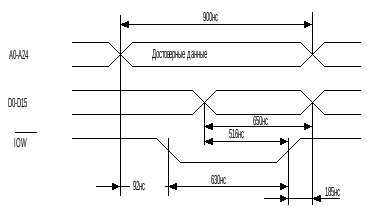

Цикл ввода-вывода

при записи (все измерения в нс.)

Рисунок 7.3

Буферный преобразователь необходим для уменьшения нагрузки на шину АТ-ВUS и в то же время служит для подключение в определенный момент времени шины данных к внутренней магистрали узла. В качестве буферного преобразователя выбираем микросхемы К580ВА86 на D0-D15 и К533АП5 на сигнал IOW. Блок дешифрации адреса строим на двух мультиплексорах К533ПС1 и резистивной матрице, определяющей базовый адрес. По умолчанию принимаем базовый адрес равным 300h.

В связи с выше перечисленными требованиями выгодно реализовать схему АЦП на специализированной для этих целей микросхеме, серийно выпускаемой в стране, например типа К594ПА1. Это цифро-аналоговый преобразователь, имеющий 12 - разрядную входную шину и возможность определения положительной и отрицательной величины опорного сигнала. Время преобразования удовлетворяет требованиям.

Перебор счетных комбинаций на входе ЦАП осуществляем при помощи регистра последовательного приближения К533ИР17. Он предназначен для построения 12 разрядных АЦП, работающих по методу последовательный приближений. Применяем ее с 12- разрядной микросхемой ЦАП К594ПА1 и интегральным компаратором К521СА3. Этот регистр имеет динамический счетный вход “С”, на который подается импульсы с генератора собранного на инверторе К130ЛН1, конденсаторе и резисторе. Частота импульсов зависит от параметров резистора и конденсатора и подбирается с целью обеспечить максимальное быстродействие. Для большей гибкости схемы, заложена возможность программного изменения частоты работы генератора, для этого использована микросхема “Программируемый таймер” из микропроцессорного комплекта КР580, в данном случае это КР580ВИ53.

Триггер К533ТМ2 используем для подачи сигнала остановки (разрешения) преобразования регистра последовательного приближения.

Для разгрузки цифровых микросхем, входной сигнал проходит через повторитель выполненный на операционном усилители типа К140УД14. Последовательно со входом ставим тока ограничивающий резистор на 10 кОм. С выхода усилителя сигнал поступает на логический преобразователь уровня К564ПУ6 для согласования аналоговых сигналов с цифровыми и канала АЦП. Сигнал выбранный на преобразователе уровня поступает на компаратор. Для наиболее точного сравнения входного сигнала с выходом ЦАП используем компаратор К521СА3, который подходит по параметрам сравниваемого напряжения и быстродействию.

Для временного хранения цифровой информации (входной преобразованный из аналогового в цифровой) используем триггеры на основе К533ТМ9, для обеспечения разрядности возьмем две такие микросхемы.

Для расширяемости схемы и возможности добавления схемы ЦАП на выходы триггеров подключаем мультиплексоры К533КП11. Выбор канала мультиплексора производится с системной шины сигналами AS0 и AS1, с помощью дешифратора собранного на микросхеме К533ИД7.

С выходов мультиплексоров результат преобразований передаются на шину данных ЭВМ IBM PC AT через двунаправленные буферные преобразователи К580ВА86. Они, буферные преобразователи служат для уменьшения нагрузки на системную шину. Программное управление ими производим с помощью цифровых компараторов К533ПС1.

В качестве источника опорного напряжения выбираем параметрический стабилизатор, так как наиболее простой в реализации и с достаточными стабилизирующими свойствами при токе до 100 мА. Напряжение стабилизации - 10В. На специализированную микросхему ЦАП К594ПА1 опорное напряжение поступает через построечные резисторы типа СП-0,125-100.

В схеме используется сигналы логической единицы - ‘1’ и логического нуля ‘0’. Логический ноль получаем соединением вывода с землей схемы, а логическую единицу - через сопротивление МЛТ-0,125-1кОм на основной источник питающего напряжения - 5В, взятый с системной магистрали.

Исходя из справочных данных для обеспечения устойчивой работы устройства на высокой частоте необходимо включать в схему фильтрующие конденсаторы из расчета один конденсатор на пять микросхем серии К533.

АЦП разработан в виде платы со стандартным разъемом, устанавливаемой в слот ISA компьютера типа IBM PC AT. Имеет габаритные размеры 350х145х35. На плате имеется два разъема, один из которых предназначен для установки в слот компьютера, другой для подключения выхода нормирующего преобразователя к плате АЦП. Плата изготовлена из текстолита толщиной 1,5 мм, отверстия металлизированные. Разъем крепиться к плате по средствам двух болтов М3 и двух соответствующих гаек.

Элементы устанавливаются на плату с одной стороны, используемые микросхемы имеют пластмассовые корпуса с прямоугольными выводами (корпуса 201.14-3, 201.16-6), устанавливаемые на печатные платы с односторонним или двусторонним расположением печатных проводников в металлизированные отверстия с зазором, который обеспечивается конструкцией выводов и планарные корпусами с отформованными выводами (корпуса 401.14-3,4018.24-1), устанавливаемые на платы с односторонним или двусторонним расположением проводников следующими способами: вплотную на печатную плату, с зазором 0,3 мм или вплотную на прокладку.