- •Раздел 4. Микропроцессоры семейства intel

- •Тема 4.1. Модели мп семейства intel и их сравнительная характеристика

- •Тема 4.2. Организация однокристальных 16-разрядных микропроцессоров

- •Стандартная архитектура 16-разрядного микропроцессора intel 8086.

- •Программная модель микропроцессора intel 8086.

- •Организация памяти.

- •Стандартная архитектура 16-разрядного микропроцессора intel 8086.

- •Программная модель микропроцессора intel 8086.

- •Сегментные регистры (cs, ds, ss, es),

- •Регистр адреса командIp,

- •Регистр флагов f.

- •Регистр флагов f

- •3. Организация памяти.

- •Тема 4.3. Система команд мп, форматы команд, классификация команд, способы адресации

- •Формат команды микропроцессора

- •Режимы адресации операндов

- •Тема 4.4. Система прерываний микроЭвм

- •Типы прерываний и особых ситуаций. Приоритеты прерываний и особых ситуаций

- •Механизм обработки прерываний

- •Типы прерываний и особых ситуаций. Приоритеты прерываний и особых ситуаций

- •Аппаратные прерывания

- •Программные прерывания

- •Исключительные ситуации

- •Механизм обработки прерываний

- •Тема 4.5. Сопроцессоры

- •Общие сведения и технические характеристики. Форматы команд и обрабатываемых данных. Система команд арифметического сопроцессора

- •Структура арифметического сопроцессора

- •Общие сведения и технические характеристики. Форматы команд и обрабатываемых данных. Система команд арифметического сопроцессора

- •Структура арифметического сопроцессора

- •Тема 4.6. Архитектура 32-разрядных мп

- •Регистровая структура мп 80486

- •Типы данных 32-разрядных мп

- •Система команд, форматы команд и способы адресации мп 80486

- •Тема 4.7. Реальный режим работы мп

- •Тема 4.8. Защищенный режим работы мп

- •Дескрипторы сегментов и их таблицы. Типы сегментов и дескрипторов

- •Страничная и сегментная организация памяти. Преобразование адресов в защищенном режиме

- •Средства поддержки мультизадачности и защиты. Механизмы защиты

- •Тема 4.9. Виртуальный режим работы мп

- •Виртуальная память. Средства поддержки виртуальной памяти

- •Пространство виртуальных адресов. Механизм преобразования адресов

- •Виртуальная память. Средства поддержки виртуальной памяти

- •Пространство виртуальных адресов. Механизм преобразования адресов

- •Сегментно - страничное распределение

Регистр флагов f

Регистр флагов F хранит признаки результатов выполнения арифметических и логических операций и управляющие признаки. Управляющие признаки можно установить или сбросить программно.

Таблица – Назначение флагов

|

Флаг |

№ бита |

Назначение флага |

|

CF |

0 |

Флаг переноса – фиксирует значение переноса, возникающего при сложении байтов или слов, а также значение выдвигаемого бита в операциях сдвига |

|

PF |

2 |

Флаг четности (паритета) – используется для контроля правильности передачи данных, устанавливается при четном количестве единиц в результате операции |

|

AF |

4 |

Флаг вспомогательного переноса – используется только для двоично-десятичной арифметики; устанавливается в единицу, если арифметическая операция приводит к переносу из младшей тетрады в старшую |

|

ZF |

6 |

Флаг нулевого результата – устанавливается при нулевом результате операции |

|

SF |

7 |

Флаг знака результата – дублирует значение старшего бита результата; SF=0 для положительных чисел и SF=1 – для отрицательных |

|

TF |

8 |

Флаг трассировки или пошагового режима, применяемого при отладке программ. При TF=1 микропроцессор переходит в пошаговый режим работы, когда автоматически генерируется сигнал внутреннего прерывания после выполнения каждой команды с целью перехода к соответствующей подпрограмме, которая обеспечивает индикацию содержимого внутренних регистров микропроцессора |

|

IF |

9 |

Флаг разрешения прерывания – при IF=1 микропроцессор воспринимает и реагирует на запросы прерывания (прерывания разрешены), при IF=0 прерывания запрещены |

|

DF |

10 |

Флаг направления – используется для задания направления обработки строк данных; DF=0 – обработка строки от меньших адресов к большим, DF=1 – от больших адресов к меньшим |

|

OF |

11 |

Флаг переполнения – сигнализирует о потере старшего бита результата сложения или вычитания в связи с переполнением разрядной сетки при работе со знаковыми числами |

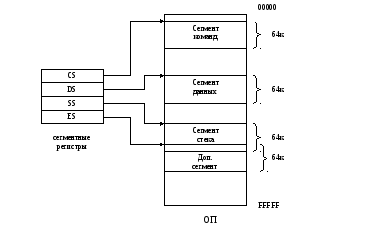

3. Организация памяти.

Шина адреса микропроцессора INTEL 8086 имеет 20 разрядов, что позволяет непосредственно адресовать оперативную память емкостью 1 Мбайт, т.е.220 ячеек. Память логически организована как одномерный массив байтов, каждый из которых имеет 20-разрядный физический адрес. Весь обмен информацией между микропроцессором и оперативной памятью осуществляется с использованием физических адресов. Как только устройство шинного интерфейса микропроцессора обращается к памяти, формируется физический адрес требуемой ячейки оперативной памяти. Физический адрес представляется 20-разрядным числом и однозначно определяет любую из 1 Мбайт ячеек памяти.

Обычно программа состоит из нескольких частей – кодовой, информационной и стековой. Так как заранее неизвестны длины этих составляющих, то удобно, чтобы при программировании каждая из них имела собственную нумерацию слов, отсчитываемых с нуля. Для этого организуют систему сегментированной памяти. Все пространство памяти представляет собой набор сегментов. Сегменты в памяти могут следовать друг за другом непрерывно, могут перекрываться или находиться на некотором расстоянии друг от друга. Физическая ячейка памяти может принадлежать одному или нескольким сегментам. Каждый сегмент представляет собой отдельную логическую единицу информации, содержащую совокупность данных или программный код и расположенную в адресном пространстве пользователя.

Рисунок 3 – Расположение сегментов в пространстве памяти

Микропроцессор позволяет независимо адресовать 4 программных сегмента в памяти:

-

сегмент команд,

-

сегмент данных,

-

сегмент стека,

-

дополнительный сегмент.

Каждой составляющей программы выделяется сегмент памяти. Сегмент – это независимая и отдельно адресуемая единица памяти. В каждом сегменте устанавливается своя собственная нумерация слов. Физический адрес памяти определяется номером сегмента и адресом внутри сегмента.

Каждому сегменту программой назначается начальный адрес, являющийся адресом первого байта сегмента в пространстве памяти. Начальный адрес сегмента хранится в соответствующем сегментном регистре.

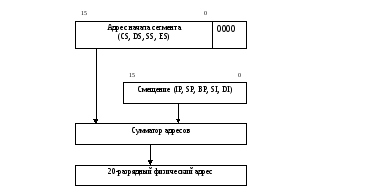

Так как микропроцессора INTEL 8086 является 16-разрядным, то все операции при вычислении физического адреса производятся с 16-разрядными адресными объектами. Логический адрес ячейки памяти состоит из двух 16-разрядных значений:

-

начального адреса сегмента,

-

внутрисегментного смещения, которое определяет расстояние от начала сегмента до адресуемой ячейки памяти.

Сегмент может начинаться только по адресу кратному 16. В сегментном регистре хранится 16 старших битов 20-разрядного начального адреса сегмента. Четыре младших бита адреса принимаются равными нулю и дописываются справа к содержимому сегментного регистра при вычислении физических адресов ячеек памяти. Изменяя содержимое сегментных регистров, можно передвигать сегменты в границах всей памяти. Внутри программы все адреса памяти относительны к началу сегмента.

Для хранения относительных адресов ячеек памяти внутри сегментов (смещений относительно начала сегментов) используются регистры смещений IP, SP, BP, SI, DI.

Схема формирования физического адреса ячейки памяти представлена на рисунке 4.

Рисунок 4 – Схема формирования 20-разрядного физического адреса

Выборка команд из памяти осуществляется из текущего сегмента команд по адресу, сформированному путем суммирования содержимого сегментного регистра CS и смещения, в качестве которого используется содержимое регистра указателя команд IP. После выборки из памяти программ очередного байта команды содержимое IP увеличивается на единицу.

Указательные регистры SP и BP предназначены для доступа к данным в текущем сегменте стека. Стековые команды всегда обращаются к текущему сегменту стека по адресу SS : SP. Если при вычислении адреса используется регистр BP, то ячейки стекового сегмента рассматриваются как оперативная память с произвольной выборкой.

Индексные регистры SI и DI содержат смещения, которые относятся к текущему сегменту данных.

Сегментная организация памяти обеспечивает возможность создания позиционно независимых или динамически перемещаемых программ, что необходимо в мультипрограммной среде для эффективного использования оперативной памяти. Чтобы обеспечить позиционную независимость, все смещения в программе должны задаваться относительно фиксированных значений, содержащихся в сегментных регистрах. Это позволяет произвольно перемещать программу в адресном пространстве памяти, изменяя только содержимое сегментных регистров.