- •Раздел 4. Микропроцессоры семейства intel

- •Тема 4.1. Модели мп семейства intel и их сравнительная характеристика

- •Тема 4.2. Организация однокристальных 16-разрядных микропроцессоров

- •Стандартная архитектура 16-разрядного микропроцессора intel 8086.

- •Программная модель микропроцессора intel 8086.

- •Организация памяти.

- •Стандартная архитектура 16-разрядного микропроцессора intel 8086.

- •Программная модель микропроцессора intel 8086.

- •Сегментные регистры (cs, ds, ss, es),

- •Регистр адреса командIp,

- •Регистр флагов f.

- •Регистр флагов f

- •3. Организация памяти.

- •Тема 4.3. Система команд мп, форматы команд, классификация команд, способы адресации

- •Формат команды микропроцессора

- •Режимы адресации операндов

- •Тема 4.4. Система прерываний микроЭвм

- •Типы прерываний и особых ситуаций. Приоритеты прерываний и особых ситуаций

- •Механизм обработки прерываний

- •Типы прерываний и особых ситуаций. Приоритеты прерываний и особых ситуаций

- •Аппаратные прерывания

- •Программные прерывания

- •Исключительные ситуации

- •Механизм обработки прерываний

- •Тема 4.5. Сопроцессоры

- •Общие сведения и технические характеристики. Форматы команд и обрабатываемых данных. Система команд арифметического сопроцессора

- •Структура арифметического сопроцессора

- •Общие сведения и технические характеристики. Форматы команд и обрабатываемых данных. Система команд арифметического сопроцессора

- •Структура арифметического сопроцессора

- •Тема 4.6. Архитектура 32-разрядных мп

- •Регистровая структура мп 80486

- •Типы данных 32-разрядных мп

- •Система команд, форматы команд и способы адресации мп 80486

- •Тема 4.7. Реальный режим работы мп

- •Тема 4.8. Защищенный режим работы мп

- •Дескрипторы сегментов и их таблицы. Типы сегментов и дескрипторов

- •Страничная и сегментная организация памяти. Преобразование адресов в защищенном режиме

- •Средства поддержки мультизадачности и защиты. Механизмы защиты

- •Тема 4.9. Виртуальный режим работы мп

- •Виртуальная память. Средства поддержки виртуальной памяти

- •Пространство виртуальных адресов. Механизм преобразования адресов

- •Виртуальная память. Средства поддержки виртуальной памяти

- •Пространство виртуальных адресов. Механизм преобразования адресов

- •Сегментно - страничное распределение

Тема 4.8. Защищенный режим работы мп

-

Работа МП в защищенном режиме. Управление памятью в защищенном режиме

-

Дескрипторы сегментов и их таблицы. Типы сегментов и дескрипторов

-

Страничная и сегментная организация памяти. Преобразование адресов в защищенном режиме

-

Средства поддержки мультизадачности и защиты. Механизмы защиты

-

Работа МП в защищенном режиме. Управление памятью в защищенном режиме

Основным режимом работы 32-разрядных микропроцессоров является защищенный режим. Отличительные особенности защищенного режима:

-

виртуальное адресное пространство,

-

защита,

-

многозадачность.

Защищенный режим обеспечивает защиту аппаратных и программных ресурсов одной задачи от возможного влияния другой. Основным защищаемым ресурсом является память, в которой хранятся команды, данные и системные таблицы. Защита памяти основана на сегментации. Сегментация – это механизм, с помощью которого память разделяется на отдельные области адресного пространства определенного назначения.

В защищенном режиме программа оперирует с адресами, которые могут относиться к физически отсутствующим ячейкам памяти, поэтому такое адресное пространство называют виртуальным. Размер виртуального адресного пространства программы может превышать емкость физической памяти.

В защищенном режиме используется сегментная и страничная организация памяти. Сегментная организация используется на прикладном уровне, а страничная – на системном.

Формирование адреса ячейки памяти в защищенном режиме представлено на рисунке 4.8.1.

Блок вычисления

смещения

Линейный адрес

Физический адрес

Блок сегментации

Блок страничного

преобразования (необязательный

Селектор сегмента

Рисунок 4.8.1 - Формирование адреса ячейки памяти в защищенном режиме

Преобразование логического адреса в физический происходит в два этапа:

-

блок управления сегментами выполняет трансляцию адреса в соответствии с сегментированной моделью памяти, получая 32-разрядный линейный адрес,

-

блок страничного преобразования выполняет разбиение на страницы, преобразуя 32-разрядный линейный адрес в физический.

Селектор используется для определения базового адреса сегмента. Базовый адрес суммируется со смещением для формирования 32-разрядного линейного адреса. Полученный линейный адрес используется как 32-разрядный физический адрес, либо, если доступна страничная организация памяти, страничный механизм преобразует линейный адрес в физический.

-

Дескрипторы сегментов и их таблицы. Типы сегментов и дескрипторов

В рамках сегментированной модели адресации для программы память представляется группой независимых сегментов. С каждым сегментом связана особая структура, хранящая информацию о нем, называемая дескриптором. Дескриптор – это 8-байтная единица описательной информации, распознаваемая устройством управления памятью в защищенном режиме. Дескриптор обеспечивает микропроцессор данными, которые необходимы для преобразования логического адреса в линейный. Для каждого сегмента дескриптор указывает:

-

базовый адрес сегмента,

-

предел сегмента,

-

тип сегмента,

-

права доступа к сегменту.

В защищенном режиме сегменты могут начинаться с любого линейного адреса (который называется базовым адресом сегмента) и иметь любой предел до 4 Гбайт.

Обобщенный формат дескриптора сегмента:

-

63 56

55

54

53

52

51 48

47

права доступа

40

39 32

Базовый адрес 31-24

G

D

U

Предел 19-16

P

DPL

S

Тип

A

Базовый адрес 23-16

Байт 8

Байт 7

Байт 6

Байт 5

31

16

15

0

Базовый адрес 15-0

Предел 15-0

Байт 4 - 3

Байт 2 - 1

Рисунок 4.8.2 - Обобщенный формат дескриптора сегмента

В 32-разрядном микропроцессоре поле базового адреса занимает байты 3, 4, 5 и 8 формата дескриптора. В ходе выполнения команды эти байты объединяются в один 32-разрядный базовый адрес. Базовый адрес определяет местоположение сегмента в 4 Гбайтном линейном адресном пространстве.

Поле предела длиной 20 бит занимает байты 1, 2 и младшую тетраду байта 7. Предел определяет длину сегмента и задает максимальное смещение в сегменте.

В старшей тетраде седьмого байта дескриптора находятся следующие биты управления:

-

бит гранулярности (бит дробления) G. При G=0 единицей памяти в сегменте является байт (максимальный размер сегмента составляет 1 Мбайт), при G=1 – единицей памяти в сегменте является страница длиной 4 Кбайт (максимальный размер сегмента равен 4 Мбайт).

-

бит размера D. При D=0 операнды в памяти считаются 16-разрядными, D=1 – 32-разрядными.

-

бит пользователя U – поле, доступное для использования системным программистом, бит пользователя U может быть установлен или сброшен программно.

Байт с номером 6 дескриптора содержит права доступа, в частности, следующие биты управления:

-

бит присутствия P сегмента в оперативной памяти: P=1 – сегмент находится в оперативной памяти. В режиме виртуальной памяти операционная система может передавать содержимое некоторых сегментов на жесткий диск, при этом она сбрасывает бит P в ноль в дескрипторе этого сегмента. Если программа после этого снова обращается к сегменту, возникает исключение отсутствия сегмента. Операционная система ищет свободную область физической памяти (при этом, возможно, отправляет на диск некоторый другой сегмент), копирует содержимое запрошенного сегмента из диска в память, записывает в его дескриптор новый базовый адрес и осуществляет перезапуск команды, которая вызвала исключение отсутствия сегмента. Описанный процесс называется свопингом или подкачкой.

-

поле уровня привилегий сегмента DPL содержит два бита, высшему уровню привилегии соответствует значение 0, низшему – значение 3.

-

системный бит S определяет принадлежность сегмента: S=1 – сегмент кодов команд и данных, S=0 – системный сегмент.

-

поле типа сегмента занимает три разряда и определяет тип сегмента и операции, которые в нем могут выполняться в соответствии с таблицей:

-

Разряды поля Тип

Тип сегмента

Разрешенные операции

000

данных

только считывание

001

данных

считывание и запись

010

стека

только считывание

011

стека

считывание и запись

100

кодов

только выполнение

101

кодов

выполнение и считывание

110

подчиненный сегмент кодов

только выполнение

111

подчиненный сегмент кодов

выполнение и считывание

-

бит обращения А: А=0 – к сегменту не было обращений. Если в системе реализуется обмен сегментов между оперативной и внешней памятью, то, отслеживая состояние бита обращения, операционная система может определять частоту обращения к каждому сегменту и принимать решение о выборе сегмента для удаления из памяти.

Все дескрипторы располагаются в специальных дескрипторных таблицах. Существует три вида дескрипторных таблиц:

-

глобальная дескрипторная таблица GDT,

-

локальная дескрипторная таблица LDT,

-

таблица дескрипторов прерываний IDT.

Дескрипторные таблицы резидентно находятся в памяти. Эти таблицы создаются и заполняются до переключения в защищенный режим работы микропроцессора, они содержат описания используемых программой сегментов памяти. Дескрипторная таблица может иметь размер от 8 байт до 64 Кбайт.

Глобальная дескрипторная таблица единственная. Она содержит дескрипторы для всех задач, выполняемых микропроцессором в многозадачном режиме. В глобальной дескрипторной таблице перечисляются сегменты, к которым могут обращаться все системные задачи с учетом ограничений только по уровням привилегий.

В локальной дескрипторной таблице указаны сегменты, которые предоставляются только одной конкретной задаче. Для однозадачных систем локальная дескрипторная таблица может отсутствовать (вся информация содержится в глобальной дескрипторной таблице). При необходимости локальные дескрипторные таблицы создаются по одной для каждой задачи.

Независимо от уровня привилегии программа не может обращаться к сегменту до тех пор, пока он не описан в дескрипторной таблице. Для доступности какого-либо сегмента задаче его дескриптор должен присутствовать либо в текущей локальной дескрипторной таблице, либо в глобальной дескрипторной таблице. Такой механизм защищает сегменты конкретной задачи и в тоже время позволяет иметь глобальные данные, которые разделяются между всеми задачами.

Таблица дескрипторов прерываний применяется только при генерации прерываний и исключений. Дескрипторная таблица прерываний содержит вектора прерываний, которые указывают адреса программ обработки прерываний.

Для работы с дескрипторными таблицами операционная система использует системные регистры защищенного режима:

GDTR – регистр глобальной дескрипторной таблицы, задает базовый адрес таблицы и ее предел,

LDTR – регистр локальной дескрипторной таблицы, являющийся селектором, содержимое которого определяет местонахождение информации о локальной дескрипторной таблице (начальный адрес, предел, права доступа) в глобальной дескрипторной таблице,

IDTR – регистр таблицы дескрипторов прерываний, задает базовый адрес таблицы и ее предел.

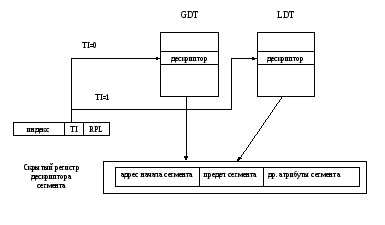

В защищенном режиме работы микропроцессора содержимое сегментных регистров называется селекторами сегментов. Микропроцессор использует селектор сегмента для нахождения дескриптора сегмента. Формат селектора:

|

15 |

|

|

|

3 |

2 |

1 |

0 |

|

Индекс |

TI |

RPL |

|||||

Рисунок 4.8.3 - Формат селектора

Поле RPL определяет уровень привилегий, который требует задача. На самом высоком уровне привилегий (0 уровень) работает ядро операционной системы. Уровень 1 присваивается системным сервисам, управляющим ресурсами ввода-вывода, распределением памяти, планированием заданий. Уровень 2 присваивается расширениям операционной системы, уровень 3 – прикладным программам пользователя. Привилегии – это свойство, которое определяет, какие компьютерные операции разрешаются в любой момент времени и какие доступы к памяти возможны. Система защиты микропроцессора позволяет ограничить доступ к отдельным сегментам в зависимости от уровня привилегий задачи.

Разряд TI определяет в какой таблице необходимо искать дескриптор. При TI=0 поиск ведется в глобальной дескрипторной таблице, при TI=1 – в локальной дескрипторной таблице.

Селектор позволяет выбрать из таблицы дескрипторов необходимый дескриптор, номер которого указывает 13-разрядное поле «индекс». Поле «индекс» определяет смещение относительно начального адреса дескрипторной таблицы. Процессор умножает значение поля «индекс» на 8 (размер дескриптора) и добавляет полученный результат к базовому адресу таблицы дескрипторов. Полученное значение и является адресом дескриптора.

Все команды, размещающие селектор в сегментном регистре, вынуждают микропроцессор автоматически делать обращение к дескриптору, читать его и заносить информацию в скрытые регистры соответствующего сегментного регистра. Каждый сегментный регистр имеет «видимую» и «скрытую» часть. К 16-разрядным сегментным регистрам микропроцессора добавлены 64-разрядные дескрипторы сегментов. «Скрытые» части регистров контролируются микропроцессором. Считанный дескриптор автоматически записывается в соответствующий «теневой» регистр быстродействующей кэш-памяти (рисунок 4.8.4).

-

сегментные регистры

регистры дескрипторов

15 0

63 0

CS

SS

DS

ES

FS

GS

16-р-ный «видимый» «скрытый» дескриптор

селектор

Рисунок 4.8.4 – Теневые регистры дескрипторов сегментов

Во время загрузки нового значения селектора дескрипторы считываются из оперативной памяти и запоминаются во внутренних программно-недоступных или «теневых» регистрах кэш-памяти микропроцессора. Основные характеристики сегментов в процессе работы будут считываться из быстродействующей кэш-памяти, а не из оперативной памяти. Это позволяет повысить быстродействие микропроцессора, так как значения базовых адресов сегментов изменяются сравнительно редко.

После того, как операционная система сформировала в памяти таблицы дескрипторов (GDT, LDT, IDT), выполняется их инициализация. В процессе инициализации заносится информация в регистры GDTR, LDTR, IDTR. Далее селектор загружается в один из сегментных регистров и в зависимости от разряда TI происходит обращение к глобальной или локальной дескрипторной таблице. По индексу выбирается дескриптор нужного сегмента и заносится в скрытый регистр соответствующего сегментного регистра.

Рисунок 4.8.5 – Выбор дескриптора из таблиц GDT или LDT