- •1.1 Сравнительный анализ 8-разрядных микропроцессоров

- •2.2 Архитектура и режимы работы мп к580вм80

- •2.3 Генератор тактовых импульсов кр580гф24

- •2.4 Буферный регистр кр580ир82

- •2.5 Шинный формирователь кр580ва86

- •3 Разработка подсистемы памяти

- •3.1 Модуль озу кр565ру6

- •3.2 Модуль пзу к556рт5

- •4 Разработка подсистемы прерываний, ввода/вывода. Выбор таймера.

- •4.1 Программируемого контроллера прерываний кр580вн59

- •4.4 Аналого – цифровой преобразователь к572пв3

- •4.5 Архитектура контроллера прямого доступа к памяти кр580вт57

- •4.6 Архитектура программируемого таймера кр580ви53

- •5 Разработка алгоритма работы мпс

- •6 Реализация системы для мониторирования физиологических параметров человека на базе к580вм80

4.4 Аналого – цифровой преобразователь к572пв3

В схему разрабатываемой системы входит 8-разрядный аналогово-цифровой преобразователь (АЦП) КР572ПВ3. Цоколевка АЦП приведена на рисунке 21.

Рисунок 21 – Цоколевка АЦП БИС КР572ПВ3

Описание выводов КР572ПВ3 приведено в таблице 12

Таблица 12 – Назначение выводов КР572ПВ3

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сост-ние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

1-4, 15-18 |

D(7-0) |

Д(7-0) |

Канал данных |

вход/ выход |

0,1,z |

|

5 |

BU |

ЗН |

АЦП занят |

выход |

0,1,z |

|

6 |

RD |

ЧТ |

Сигнал «чтение» |

вход |

0,1 |

|

7 |

CS |

ВБ |

Выбор микросхемы |

вход |

0,1 |

|

9 |

Ucc |

Ucc |

Напряжение питания (+5 В) |

вход |

|

|

10 |

GND |

ОБЩ |

Напряжение питания (0 В) |

вход |

1 |

4.5 Архитектура контроллера прямого доступа к памяти кр580вт57

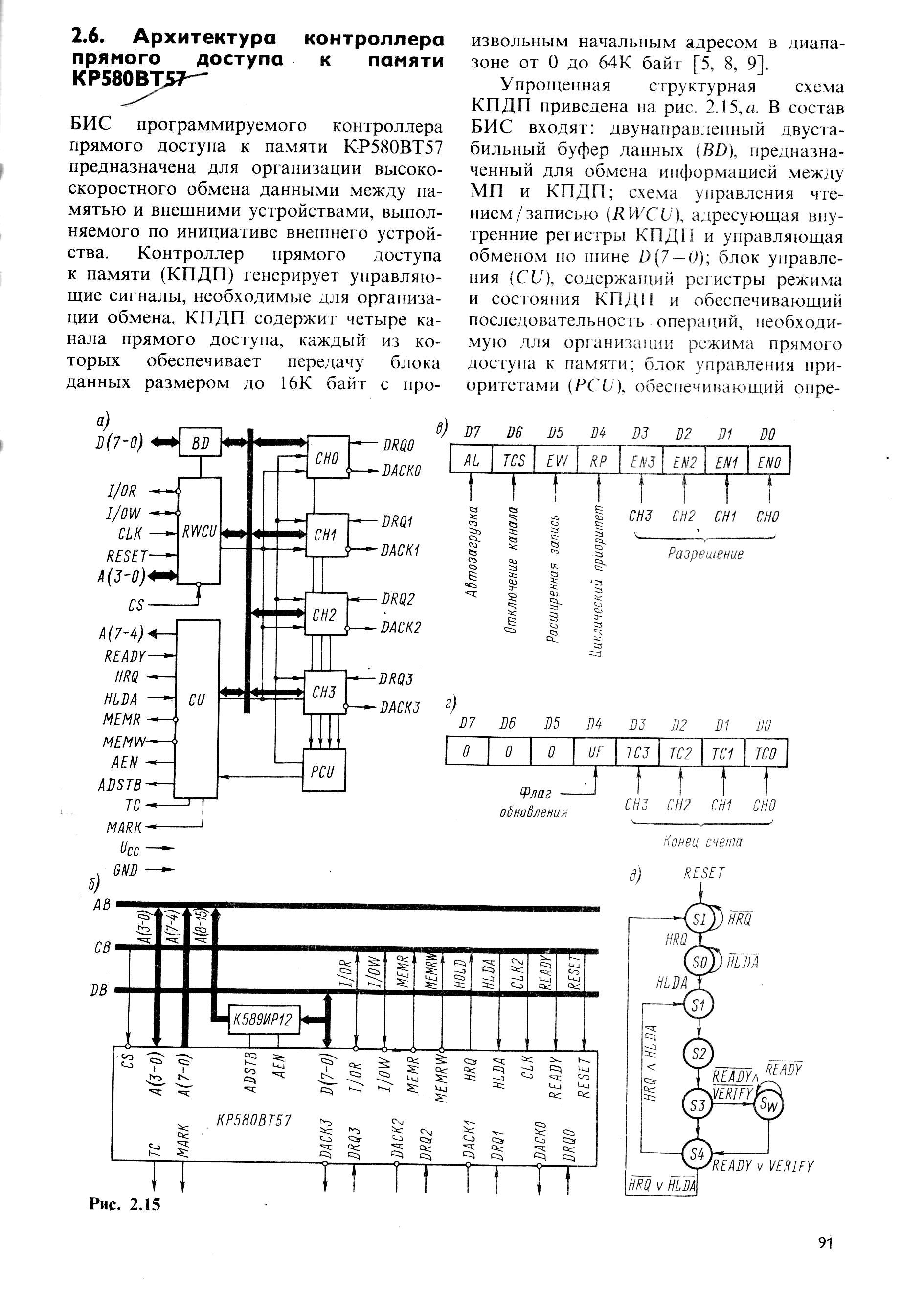

БИС программируемого контроллера прямого доступа к памяти КР580ВТ57 предназначена для организации высокоскоростного обмена данными между памятью и внешними устройствами, выполняемого по инициативе внешнего устройства. Контроллер прямого доступа к памяти (КПДП) генерирует управляющие сигналы, необходимые для организации обмена.

Упрощенная структурная схема КПДП приведена на рисунке 6. В состав БИС всходят: двунаправленный двустабильный буфер данных (BD), предназначенный для обмена информацией между МП и КПДП; схема управления чтением/записью (RWCU), адресующая внутренние регистры КПДП и управляющая обменом по шине D(7-0); блок управления (CU), содержащий регистры режима и состояния КПДП и обеспечивающий последовательность операций, необходимую для организации режима ПДП; блок управления приоритетами (PCU), обеспечивающий определенный порядок обслуживания запросов внешних устройств; четыре канала прямого доступа (CH0-CH3), каждый из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

.

Рисунок 22 – а) упрощенная структурная схема КПДП; б) схема подключения КПДП к системной шине с использованием буферного регистра К580ИР82

Цоколевка КПДП КР580ВТ57 представлена на рисунке 23. Назначение входных, выходных и управляющих сигналов КПДП приведено в таблице 13.

Рисунок 23 – Цоколевка КПДП КР580ВТ57

Таблица 13 – Описание выводов КПДП

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сост-ние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

21; 22; 23; 26; 27; 28; 29; 30 |

D(7-0) |

Д(7-0) |

Канал данных для обмена С МП |

вход/ выход |

1 |

|

1 |

RDIO |

ЧТ |

Чтение: L-уровень сигнала разрешает считывание информации из регистра, адресуемого по входам A0, A1 на шину D(7-0) |

вход/ выход |

1 |

|

2 |

WRIO |

ЗП |

Запись ввода/вывода - двунаправленный тристабильный вход/выход; выходной сигнал L-уровня разрешает программирование КПДП; выходной сигнал L-уровня разрешает запись в ВУ |

вход/ выход |

1 |

|

12 |

C |

Ц |

Вход тактовых импульсов |

вход |

1 |

|

13 |

SR |

УСТ |

Вход установки 0 |

вход |

1 |

|

35; 34; 33; 32 |

A(3-0) |

A(3-0) |

Двунаправленные тристабильные адресные выводы |

вход/ выход |

1 |

|

11 |

CS |

ВМ |

Выбор микросхемы |

вход |

0 |

|

40; 39; 38; 37 |

A(7-4) |

A(7-4) |

Тристабильные адресные выходы |

выход |

1 |

|

6 |

RDY |

ГОТ |

Готовность – входной сигнал Н-уровня указывает на готовность к обмену |

вход |

1 |

Продолжение таблицы13

|

1 |

2 |

3 |

4 |

5 |

6 |

|

10 |

HRQ |

ЗЗ |

Запрос захвата – выходной сигнал Н-уровня указывает на запрос о доступе КПДП к системным шинам |

выход |

1 |

|

7 |

HLDA |

ПОД ЗП |

Подтверждение захвата – входной сигнал Н-уровня указывает на возможность доступа к системным шинам |

вход |

1 |

|

3 |

RD |

ЧТ |

Чтение из памяти - тристабильный выход; выходной сигнал L-уровня разрешает чтение из ячейки памяти, адресуемой КПДП |

выход |

0 |

|

4 |

WR |

ЗП |

Запись в память - тристабильный выход; выходной сигнал L-уровня разрешает запись в ячейку, адресуемую КПДП |

выход |

0 |

|

9 |

AE |

РАЗ АД |

Разрешение адреса – сигнал Н-уровня используется для блокировки некоторых шин адреса и данных |

выход |

1 |

|

8 |

STBA |

СТРОБ |

Строб адреса – сигнал Н-уровня указывает на нахождение на шине D(7-0) старшего байта адреса ЗУ |

выход |

1 |

|

36 |

TC |

КС |

Конец счета – сигнал Н-уровня определяет выполнение последнего цикла передачи блока данных |

выход |

1 |

|

5 |

M128 |

М128 |

Маркер – сигнал Н-уровня указывает, что до конца передаваемого блока необходимо выполнить число циклов обмена, кратное 128 |

выход |

1 |

|

16; 17; 18; 19 |

DRQ3-DRQ0 |

ЗП ПДП |

Запросы ПДП каналов СН3-СН0; сигнал Н-уровня указывает на запрос от ВУ |

вход |

1 |

|

15; 14; 24; 25 |

DACK3-DACK0 |

ПОД ЗП |

Подтверждение запросов ПДП каналов СН3-СН0; сигнал L-уровня указывает на разрешение обмена |

выход |

0 |

|

31 |

UCC |

UПИТ |

Напряжение питания (+5 В) |

вход |

1 |

|

20 |

GND |

ОБЩ |

Напряжение питания (0 В) |

вход |

1 |