- •1.1 Сравнительный анализ 8-разрядных микропроцессоров

- •2.2 Архитектура и режимы работы мп к580вм80

- •2.3 Генератор тактовых импульсов кр580гф24

- •2.4 Буферный регистр кр580ир82

- •2.5 Шинный формирователь кр580ва86

- •3 Разработка подсистемы памяти

- •3.1 Модуль озу кр565ру6

- •3.2 Модуль пзу к556рт5

- •4 Разработка подсистемы прерываний, ввода/вывода. Выбор таймера.

- •4.1 Программируемого контроллера прерываний кр580вн59

- •4.4 Аналого – цифровой преобразователь к572пв3

- •4.5 Архитектура контроллера прямого доступа к памяти кр580вт57

- •4.6 Архитектура программируемого таймера кр580ви53

- •5 Разработка алгоритма работы мпс

- •6 Реализация системы для мониторирования физиологических параметров человека на базе к580вм80

2.4 Буферный регистр кр580ир82

Буферный регистр КР580ИР82 представляет собой 8-разрядный параллельный регистр с тристабильными выходами. Он используюется для реализации схем фиксации, буферизации и мультиплексирования в МПС на базе МП К580ИК80А и К1810ВМ86. На выходах микросхемы КР580ИР82 генерируются неинвертированные входные данные.

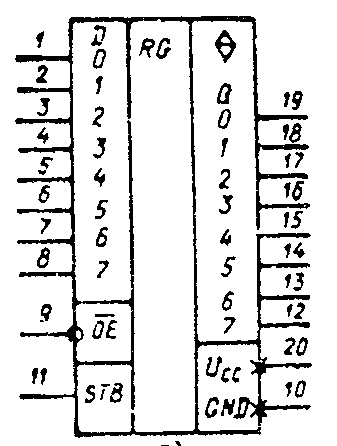

Структурная схема буферного регистра модели 82 представлена на рисунке 6, а назначение входных и выходных сигналов указано при описании выводов микросхемы в таблице 5.

Запись входных данных в буферные регистры производится при переходе сигнала STB с Н – уровня в L – уровень. При Н – уровне сигнала ОЕ выходы буферных регистров находятся в высокоимпедансном состоянии.

а) б)

Рисунок 6 – а) структурная схема буферного регистра КР580ИР82; б) цоколевка буферного регистра

Таблица 5 – Описание выводов буферного регистра КР580ИР82

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сос-тояние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

8; 7; 6; 5; 4; 3; 2; 1 |

D(7-0) |

Д(7-0) |

Входы данных |

вход |

1 |

|

11 |

STB |

СТРОБ |

Вход сигнала стробирования |

вход |

1 |

|

9 |

OE |

РАЗ. В |

Вход сигнала разрешения ввода |

вход |

1 |

|

12; 13; 14; 15; 16; 17; 18; 19 |

QO(7-0) |

ДО(7-0) |

Выходы данных |

вход |

0 |

|

20 |

UCC |

UCC |

Напряжение питания (+5 В) |

вход |

1 |

|

10 |

GND |

ОБЩ |

Напряжение питания (0 В) |

вход/ выход |

1 |

2.5 Шинный формирователь кр580ва86

Шинный формирователь КР580ВА86 представляет 8- разрядный параллельный приемопередатчик с тристабильными выходами. Он используется для реализации различных буферных схем МПС на базе МП К580ИК80А, Z - 80 и К1810ВМ86. На выходах микросхемы КР580ВА86 генерируются неинвертированные выходные данные.

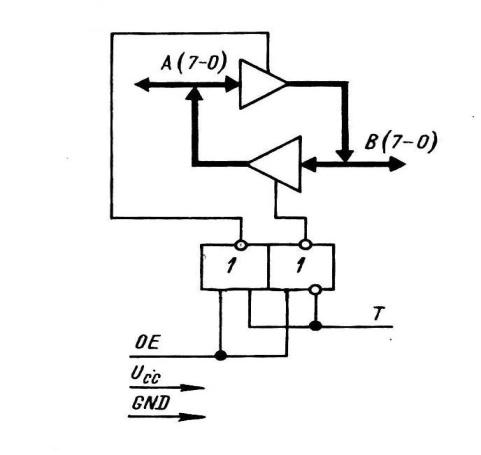

Структурная схема шинного формирователя модели 86 представлена на рисунке 8, а назначение входных и выходных сигналов указано при описании выводов микросхемы в таблице 6.

Рисунок 8 – Структурная схема шинного формирователя модели КР580ВА86

Цоколевка шинного формирователя модели КР580ВА86 представлена на рисунке 9

Рисунок 9 – Цоколевка шинного формирователя КР580ВА86

Таблица 6 – Описание выводов шинного формирователя КР580ВА86

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сос-тояние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

8; 7; 6; 5; 4; 3; 2; 1 |

А(7-0) |

А(7-0) |

Выводы данных для локальной шины МП |

вход/ выход |

1 |

|

12; 13; 14; 15; 16; 17; 18; 19 |

В(7-0) |

Б(7-0) |

Выводы данных для системной шины |

вход/ выход |

1 |

|

11 |

Т |

Т |

Вход управления направлением передачи |

вход |

1 |

|

9 |

ОЕ |

ОЕ |

Вход разрешения передачи |

вход |

1 |

|

20 |

UCC |

UCC |

Напряжение питания (+5 В) |

вход |

1 |

|

10 |

GND |

ОБЩ |

Напряжение питания (0 В) |

вход |

1 |

При Н – уровне сигнала на входе Т и L – уровне сигнала на входе ОЕ информации с выводов А (7 - 0) передается на вывод В (7 - 0). При L – уровне сигнала на вход и L – уровне сигнала на входе ОЕ информация с выводов В (7 - 0) передается на выводы А (7 - 0). При Н – уровне сигнала на входе ОЕ шинные формирователи переходят в высокоимпедансное состояние.

2.6 Упрощенная структурная схема микро-ЭВМ

На рисунке 10 представлена упрощенная структурная схема управляющей микро-ЭВМ. В состав микро-ЭВМ входят: микропроцессор, память, включающая ОЗУ и ПЗУ, которая служит для хранения данных и программ, устройств ввода/вывода, служащих для связи микроЭВМ с внешними устройствами, система прерываний, таймер.

Системная шина – канал, предназначенный для объединения всех блоков микро-ЭВМ и обеспечения обмена данными в виде двоичных чисел.

Устройства ввода/вывода (клавиатура и дисплей) подключаются к системной шине через интерфейсы ввода/вывода (программируемый контроллер клавиатуры и индикации).

ПЗУ и ОЗУ образуют систему памяти, предназначенную для хранения программ управления, констант. Для подключения памяти к системной шине используются буферные регистры. ОЗУ используется для хранения данных, поступивших из внешнего устройства или подготовленных для выдачи во внешнее устройство, а также для хранения промежуточных результатов вычислений и адресной информации.

Микропроцессор осуществляет обработку данных и управляет всеми модулями системы. Для синхронизации микропроцессора с системной шиной используются системный контроллер и шинные формирователи. Блок генератора тактовых импульсов предназначен для выработки серии тактовых импульсов и некоторых вспомогательных сигналов, а также для синхронизации других блоков микро-ЭВМ.

Программируемый контроллер прерываний предназначен для обслуживания прерываний: упрощения работы процессора с внешними запросами прерываний.

системная шина

Сигналы с датчиков

Рисунок 10 - Упрощенная структурная схема микро-ЭВМ