- •1.1 Сравнительный анализ 8-разрядных микропроцессоров

- •2.2 Архитектура и режимы работы мп к580вм80

- •2.3 Генератор тактовых импульсов кр580гф24

- •2.4 Буферный регистр кр580ир82

- •2.5 Шинный формирователь кр580ва86

- •3 Разработка подсистемы памяти

- •3.1 Модуль озу кр565ру6

- •3.2 Модуль пзу к556рт5

- •4 Разработка подсистемы прерываний, ввода/вывода. Выбор таймера.

- •4.1 Программируемого контроллера прерываний кр580вн59

- •4.4 Аналого – цифровой преобразователь к572пв3

- •4.5 Архитектура контроллера прямого доступа к памяти кр580вт57

- •4.6 Архитектура программируемого таймера кр580ви53

- •5 Разработка алгоритма работы мпс

- •6 Реализация системы для мониторирования физиологических параметров человека на базе к580вм80

СОДЕРЖАНИЕ

Введение 4

1.Расшифровка и анализ технического задания 5

-

Сравнительный анализ 8-разрядных микропроцессоров 8

2.Разработка процессорного модуля, интерфейса и упрощенной

структурной схемы 9

2.1 Основные параметры ЦП К580ВМ80 9

2.2 Архитектура и режимы работы МП К580ВМ80 9

2.3 Генератор тактовых импульсов КР580ГФ24 14

2.4 Буферный регистр КР580ИР82 16

2.5 Шинный формирователь КР580ВА86 18

2.6 Упрощенная структурная схема микро ЭВМ 19

3. Разработка подсистемы памяти 21

3.1 Модуль ОЗУ КР565РУ6 21

3.2 Модуль ПЗУ К556РТ6 22

3.3 Подключение ПЗУ и ОЗУ к системной шине 24

4. Разработка подсистемы прерываний, ввода/вывода. выбор таймера 25

4.1 Программируемого контроллера прерываний КР580ВН59 25

4.2 Архитектура БИС параллельного интерфейса КР250ВВ55 27

4.3 Архитектура БИС программируемого контроллера прерывания КР580ВН59 30

4.4 Аналого – цифровой преобразователь К572ПВ3 34

4.5 Архитектура контроллера прямого доступа к памяти КР580ВТ57 35

4.6 Архитектура программируемого таймера КР580ВИ53 39

4.7 Уточненная схема МПС на основе МП К580ВМ80 40

5. Разработка алгоритма работы МПС 42

6. Реализация системы для мониторирования физиологических параметров человека на базе К580ВМ80 44

Заключение 47

Список использованных источников 48

Приложение А 49

ВВЕДЕНИЕ

С развитием технологии цифровых интегральных схем появилась возможность создавать сложные устройства обработки цифровой информации в виде компактных микросхем. Однако увеличение сложности реализуемого алгоритма обработки, как правило, сужает область его применения. Устранить противоречие между сложностью БИС и ее универсальностью удалось за счет программирования выполняемых микросхемой функций.

Широкую популярность микропроцессоры получили благодаря своим высоким функциональным возможностям и эксплуатационным характеристикам, придавшим средствам вычислительной техники и автоматики качественно новые свойства: появились и получили широкое распространение микрокалькуляторы, микроЭВМ, персональные ЭВМ, интеллектуальные роботы. Такие характеристики микропроцессоров как малые габариты, масса, потребляемая мощность позволили применять их в областях, в которых использование традиционных средств вычислительной техники было принципиально невозможным.

В настоящее время промышленностью освоено и серийно выпускается более пятнадцати микропроцессорных комплектов БИС различной, архитектуры. Развитие элементной базы микропроцессоров при этом идет по нескольким, взаимодополняющим направлениям, что обеспечивает возможность гибкой адаптации архитектуры систем управления требованиям конкретных применений и специфике условий их эксплуатации.

Целью данного курсового проекта является разработка микропроцессорной управляющей микроЭВМ, реализующей заданные взаимодействия с объектом управления и разработка программных средств системы, обеспечивающих выполнение заданного алгоритма управления.

1 РАСШИФРОВКА И АНАЛИЗ ЗАДАНИЯ

Задание на курсовой проект включает в себя набор исходных данных и ограничений для проектирования управляющей микроЭВМ.

Задание определяет:

- базовый микропроцессор К580ВМ80, на основе которого требуется построить управляющую микроЭВМ.

- алгоритм управления определяется в задании видом функций f1 и f2, длительностями управляющих сигналов t1, t2, t3; необходимо при срабатывании аварийного датчика (INT1) сформировать на пульте аварийную сигнализацию светодиодом (2Гц).

- типы БИС, на которых должны быть реализованы блоки ПЗУ и ОЗУ: К565РУ6, К541РЕ1.

Управляющая микроЭВМ проектируется на базе однокристального МП и включает в себя следующие основные устройства:

- процессорный модуль;

- память, состоящую из ОЗУ и ПЗУ;

- устройства параллельного ввода/вывода для связи с ОУ;

- блок последовательного канала для связи с ЭВМ верхнего уровня;

- программируемый системный таймер;

- контроллер прерываний;

- контроллер прямого доступа к памяти;

- пульт управления.

Алгоритм управления состоит из следующих этапов:

- обработка информации от цифровых датчиков и выдача управляющего воздействия производится путем ввода значений х1, х2, х3 и вычисления значения булевой функции f1(х1, х2, х3) (при единичном значении f1 вырабатывается управляющий сигнал =1 длительностью t1);

- при обработке информации с аналоговых датчиков процессорный модуль принимает 8-разрядные двоичные коды NU1, NU2 с выводов АЦП и код константы К с регистра пульта управления; далее вычисляется значение функции NU=f2(NU1,NU2,K) и сравнивается с константой Q; в зависимости от результатов сравнения вырабатывается один из двух двоичных управляющих сигналов y2 или y3 длительностью t2 или t3 соответственно (если NU<Q, то выдается y2, иначе выдается y3);

- формируется управляющее воздействие Y4, для чего с АЦП вводится значение NU3, производится вычисление по формуле:

- значение Y4 в виде 8-разрядного кода выдается на вход ЦАП.

В системе необходимо предусмотреть следующие линии запроса на внешние прерывания:

INT0 – отказ источника питания;

INT1 – сигнал ха аварийного датчика ОУ;

INT2 – запрос от пульта управления;

INT3 – запрос от микроЭВМ верхнего уровня.

Программное обеспечение системы разрабатывается на языке Ассемблер соответствующего микропроцессора и включает следующие основные модули:

- модуль начальной инициализации системы;

- модуль управления;

- программы обслуживания прерываний, в том числе драйвер последовательного канала.

Модуль начальной инициализации должен включать в себя тест системы процедуры загрузки управляющих слов в программируемые контроллеры и установку индикаторов пульта в исходное состояние.

Модуль управления реализует цикл управления.

Подпрограммы обслуживания прерываний обеспечивают реакцию системы на внешние события согласно алгоритмам.

Таблица 1 – Таблица истинности

|

X1 |

X2 |

X3 |

X4 |

|

|

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

Управляющий сигнал y1=1 формируется в большинстве случаев единичного сигнала на входах датчиков. Управляющий сигнал не формируется при единичном сигнале на входе датчика X2; при подаче единовременного единичного сигнала на входы X2,Х3,Х4; при единовременном единичном сигнале на X2 и X4.

1.1 Сравнительный анализ 8-разрядных микропроцессоров

При построении управляющей микро ЭВМ в качестве ЦП по техническому заданию используется К580ВМ80. Проведем сравнительный анализ среди 8-ми разрядных МП Z-80, К580ВМ80, Intel 8080. Сравнительные характеристики данных МП приведены в таблице 2.

Таблица 2 – Характеристики МП Z-80, К580ВМ80, Intel 8080

|

Параметр |

Z-80 |

К580ВМ80 |

Intel 8080 |

|

Тактовая частота, МГц |

2,5 |

2 |

2 |

|

Разрядность регистров, бит |

8 |

8 |

8 |

|

Разрядность ШД, бит |

8 |

8 |

8 |

|

Разрядность ША, бит |

16 |

16 |

16 |

|

Объём адресуемой памяти, Кбайт |

64 |

64 |

64 |

Данные 8 – ми разрядные МП различаются лишь по тактовой частоте, а по всем остальным параметрам идентичны. В данной работе нет необходимости использовать МП большей тактовой частоты, поэтому К580ВМ80 удовлетворяет требованиям курсового проекта.

2 РАЗРАБОТКА ПРОЦЕССОРНОГО МОДУЛЯ, ИНТЕРФЕЙСА И

УПРОЩЕННОЙ СТРУКТУРНОЙ СХЕМЫ

2.1 Основные параметры микроЭВМ К580ВМ80

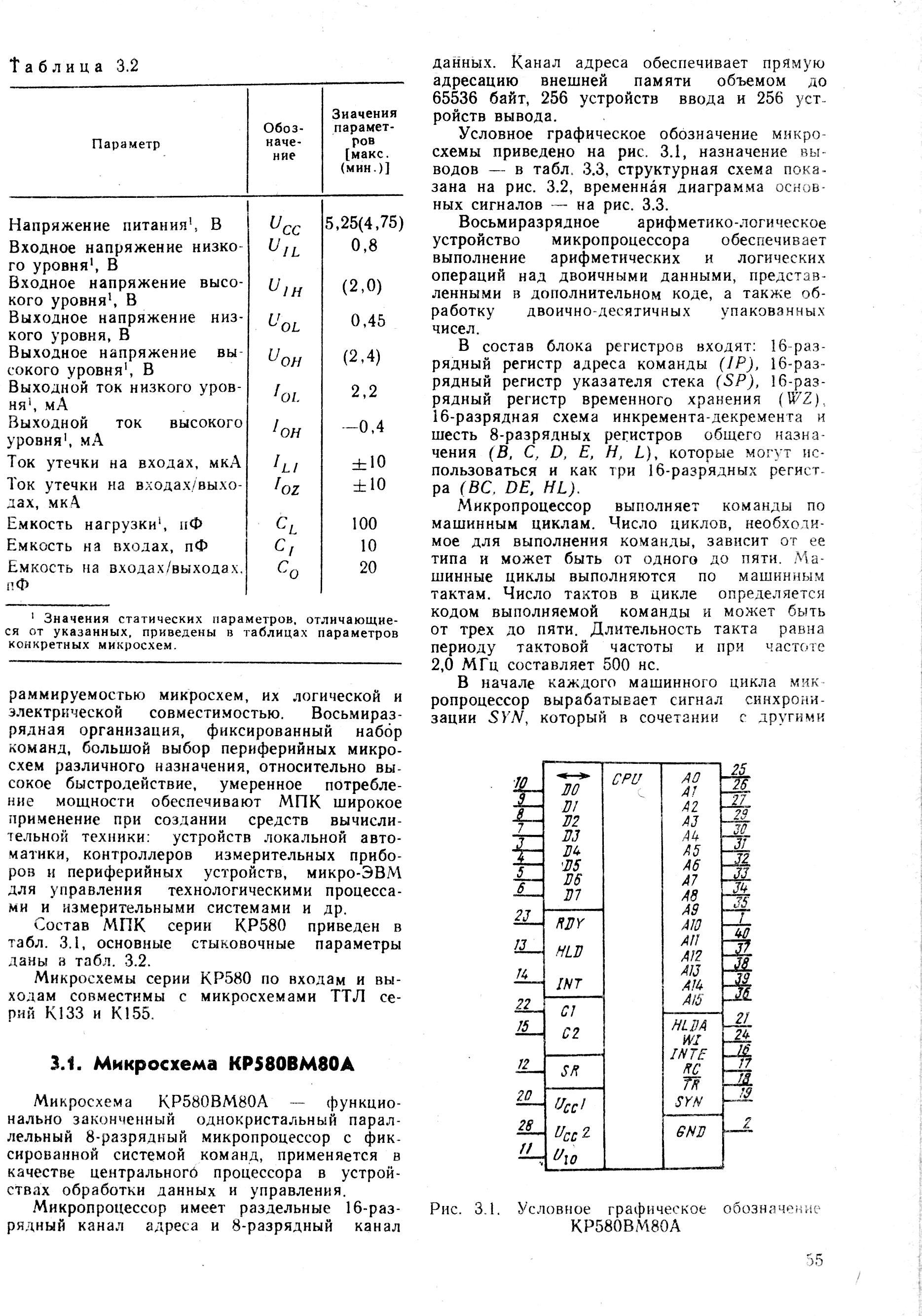

Микросхема К580ВМ80 – функционально законченный однокристальный параллельный 8-разрядный микропроцессор с фиксированной системой команд, - применяется в качестве центрального процессора в устройствах обработки данных и управления. Микропроцессор имеет раздельные 16-разрядный канал адреса и 8-разрядный канал данных.

Канал адреса обеспечивает прямую адресацию внешней памяти объемом до 65536 байт, 256 устройств ввода и 256 устройств вывода. Рассматриваемая БИС является однокристальным МП, выполненным на основе n-МОП-технологии. Предназначена для построения вычислительных устройств, контроллеров, микроЭВМ. Разрядность МП – 8 бит, тактовая частота 2 МГц, время выполнения команды 2-9 мкс, напряжения питания +12,+5 и – 5 В, потребляемая мощность 0,75 Вт.

Базовая архитектура содержит 8-разряднцй центральный процессор, программируемое ПЗУ, статическое ОЗУ.

2.2 Архитектура и режимы работы мп к580вм80

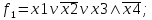

Структурная схема МП представлена на рисунке 1. В состав БИС входят арифметико-логическое устройство (ALU); регистр признаков (RS),фиксирующий признаки, вырабатываемые ALU в процессе выполнения команд; аккумулятор (А); регистр аккумулятора (RGa); регистр временного хранения операндов (RGb); десятичный корректор (DAA), выполняющий перевод информации из двоичной в двоично-десятичную форму; регистр команд (IR), предназначенный для хранения первого байта команды, содержащего код операции; дешифратор команд (DCU); блок регистров для приема, выдачи и хранения информации в процессе выполнения программ, содержащий программный счетчик (PC), указатель стека (SP), регистр адреса (RGA), шесть регистров общего назначения (B, C, D, E, H, L) и вспомогательные регистры (W и Z); схема управления и синхронизации (CU), формирующая последовательности управляющих сигналов для работы ALU и блока регистров; 16-разрядный буферный регистр адреса (BA); 8-разрядный буферный регистр данных (BD), двунаправленный мультиплексор (MUX) для обмена операндами и результатами операций между ALU и блоком регистров по внутренней шине данных.

Рисунок 1 – Структура МП К580ВМ80

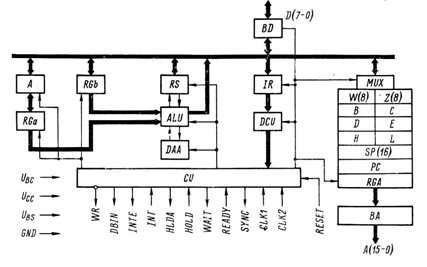

Цоколевка данного МП приведена на рисунке 2.

Рисунок 2 – Цоколевка МП К580ВМ80

В таблице 3 приведем описание выводов микросхемы.

Таблица 3 – Описание выводов микросхемы

|

Номера выводов |

Обозначение |

Наименование |

Назначение выводов |

Тип сигн. |

Сост-ние |

|

|

Англ. |

Рус. |

|||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

25; 26; 27; 29; 30; 31; 32; 33; 34; 35; 1; 40; 37; 38; 39; 36 |

A(15-0) |

А(15-0) |

Шина адреса |

Трехстабильная 16-разрядная шина адреса |

выход |

1 |

|

10; 9; 8; 7; 3; 4; 5; 6 |

D(7-0) |

Д(7-0) |

Шина данных |

Двунаправленная трехстабильная 8-разрядная шина данных |

вход |

1 |

|

18 |

WR (TR) |

|

Выдача информации |

Выход сигнала «выдача» - напряжение L-уровня указывает на выдачу байта информации на шину D(7-0) для записи в ЗУ или УВВ |

выход |

0 |

Продолжение таблицы 2

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

17 |

DBIN (RC) |

П |

Прием информации |

Выход сигнала «прием» - напряжение H-уровня указывает на прием с шины D(7-0) байта информации, выданного ЗУ или УВВ |

выход |

1 |

|

16 |

INTE |

Р. ПР |

Разрешение прерывания |

Выход сигнала «разрешение прерывания» |

выход |

1 |

|

14 |

INT |

З. ПР |

Запрос на прерывание |

Вход сигнала «запрос на прерывание» |

вход |

1 |

|

21 |

HLDA |

П. ЗХ |

Под-тверждение захвата |

Выход сигнала «подтверждение захвата» - напряжение H-уровня указывает на перевод шин адреса и данных МП в высокоимпедансное состояние |

выход |

|

|

13 |

HOLD (HLD) |

ЗХ |

Захват |

Вход сигнала «захват» - напряжение H-уровня указывает на запрос другими устройствами системы на управления шинами системы |

вход |

1 |

|

24 |

WAIT (WI) |

ОЖД |

Ожидание |

Выход сигнала «ожидание» - напряжение H-уровня указывает на состояние ожидания МП |

выход |

1 |

|

23 |

REA-DY (RDY) |

Г |

Готовность |

Вход сигнала «готовность» - |

вход |

1 |

Продолжение таблицы 2

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

|

напряжение Н-уровня указывает на готовность данных на шине D(7-0) к вводу в МП или на готовность внешних устройств к приему информации, служит для синхронизации МП с ЗУ или УВВ |

|

|

|

19 |

SYNC (SYN) |

СИНХР |

Сигнал синхронизации |

Выход сигнала «синхро» - напряжение Н-уровня идентифицирует начало каждого машинного цикла |

выход |

1 |

|

22 |

CLK1 (C1) |

Ф1 |

Тактовый сигнал |

Вход фазы 1 |

вход |

1 |

|

15 |

CLK2 (C2) |

Ф2 |

Тактовый сигнал |

Вход фазы 2 |

вход |

1 |

|

12 |

RESET (SR) |

СБР |

Сброс |

Вход установки 0 – установка счетчика команд в нуль, сброс триггеров разрешения прерывания и захвата шин |

вход |

1 |

|

28 |

UCC2 |

UCC2 |

Напряжение питания +12 В |

Напряжение питания (+12 В) |

вход |

1 |

|

20 |

UCC1 |

UCC1 |

Напряжение питания +5 В |

Напряжение питания (+5 В) |

вход |

1 |

Окончание таблицы 2

|

11 |

UI0 |

UI0 |

Напряжение питания -5 В |

Напряжение питания (-5 В) |

вход |

1 |

|

2 |

GND |

ОБЩ |

Общий |

Напряжение питания (0 В) |

выход |

1 |