Шинные формирователи.

И

нфа,

выдаваемая CPU

на

ША иШД предн. для множества Ус, подкл. к

этим шинам. Однако их число сильно

ограничивается max

вых. током CPU:

I1вых≤0.1mA,

I0вых≤1.6mA.

При

такой нагр.способн. возможно подключение

к выходу CPU

только 1 входа ИМС ТТЛ. Это объясняется

соблюдением теплового режима CPU.

Проблему решают БШД и БША. Для их

построения предусмотрены шинные

формирователи КР580ВА86, КР580ВА87.

нфа,

выдаваемая CPU

на

ША иШД предн. для множества Ус, подкл. к

этим шинам. Однако их число сильно

ограничивается max

вых. током CPU:

I1вых≤0.1mA,

I0вых≤1.6mA.

При

такой нагр.способн. возможно подключение

к выходу CPU

только 1 входа ИМС ТТЛ. Это объясняется

соблюдением теплового режима CPU.

Проблему решают БШД и БША. Для их

построения предусмотрены шинные

формирователи КР580ВА86, КР580ВА87.

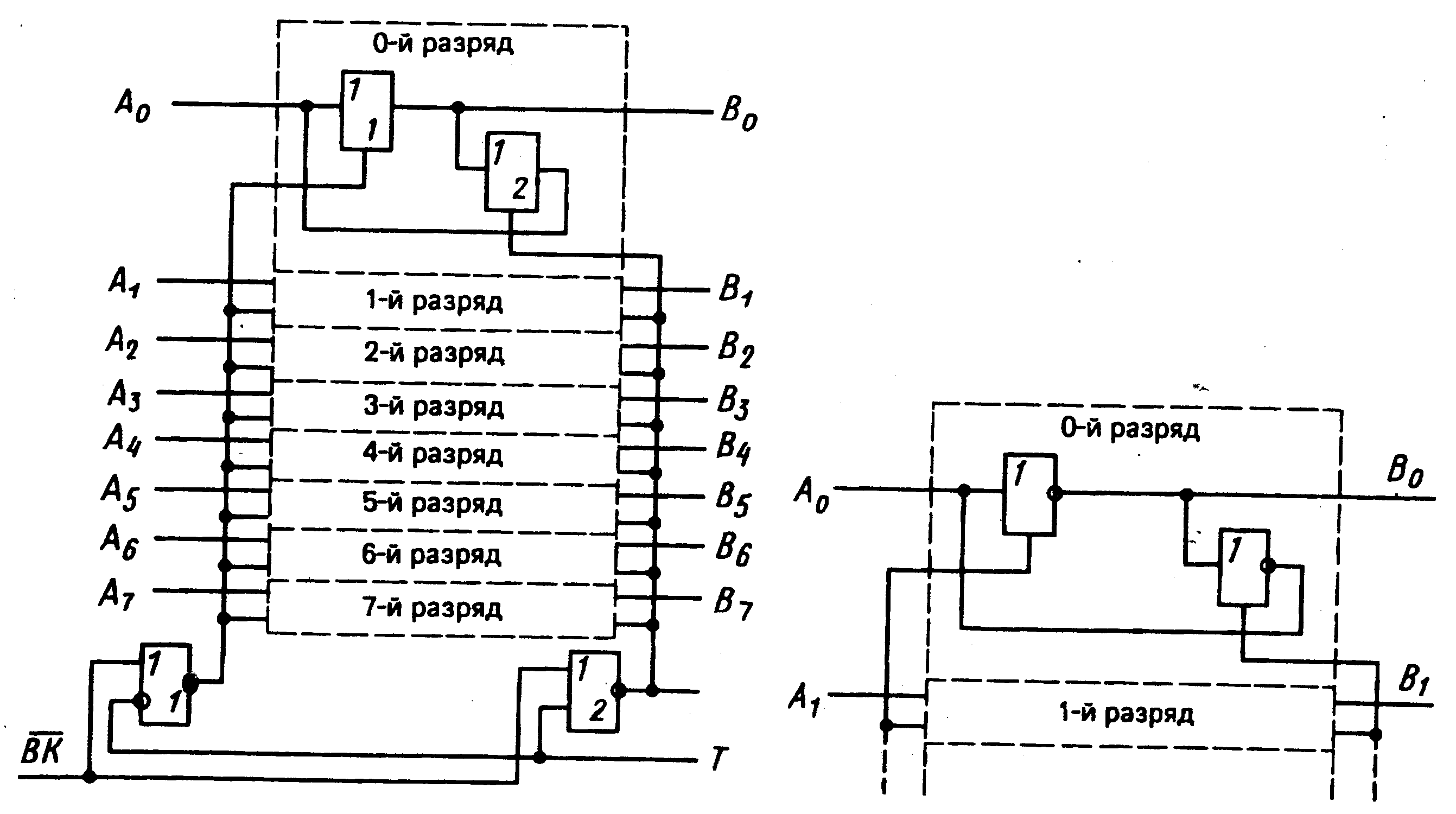

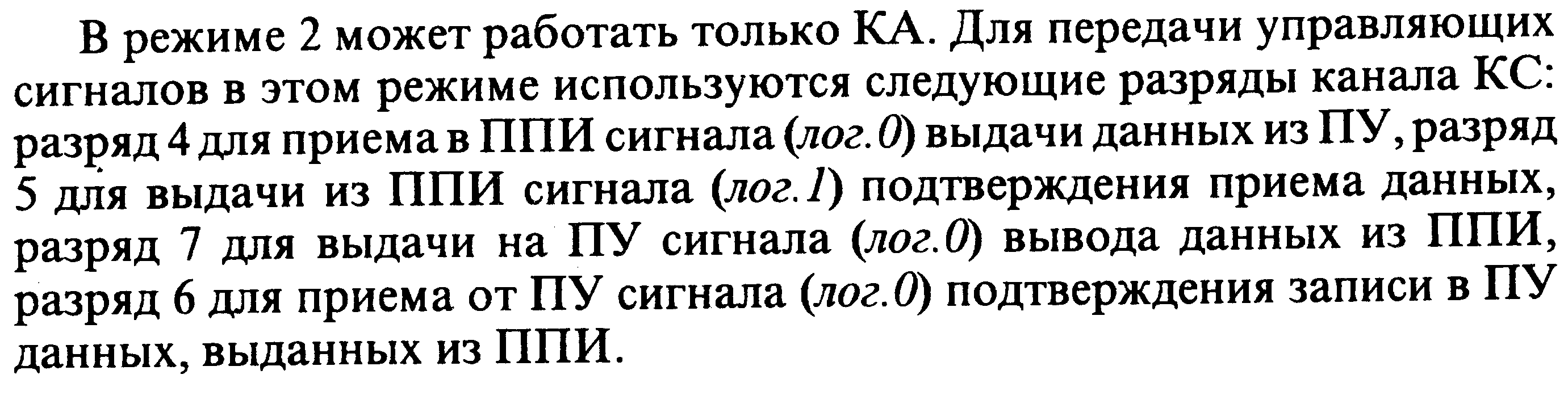

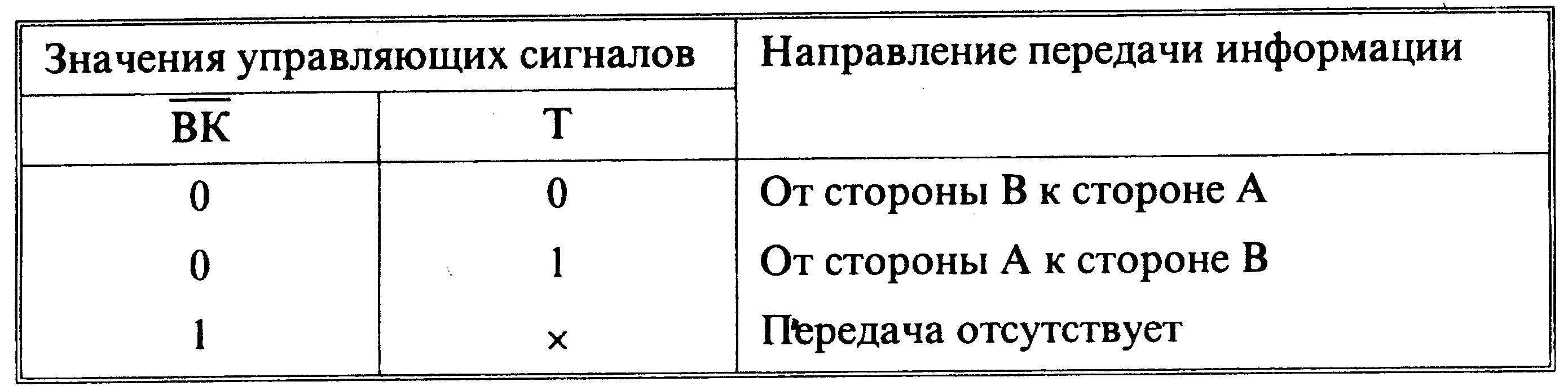

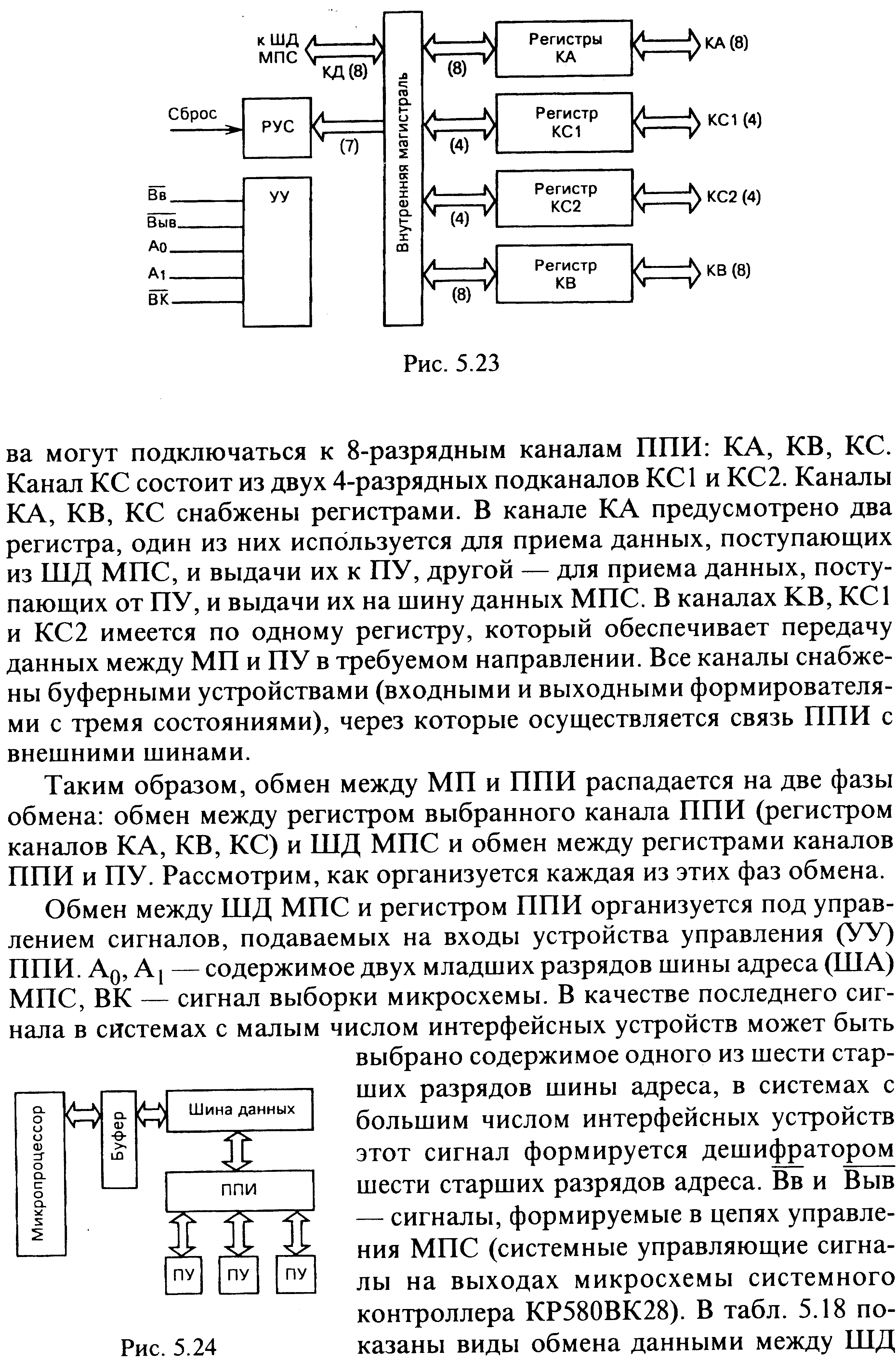

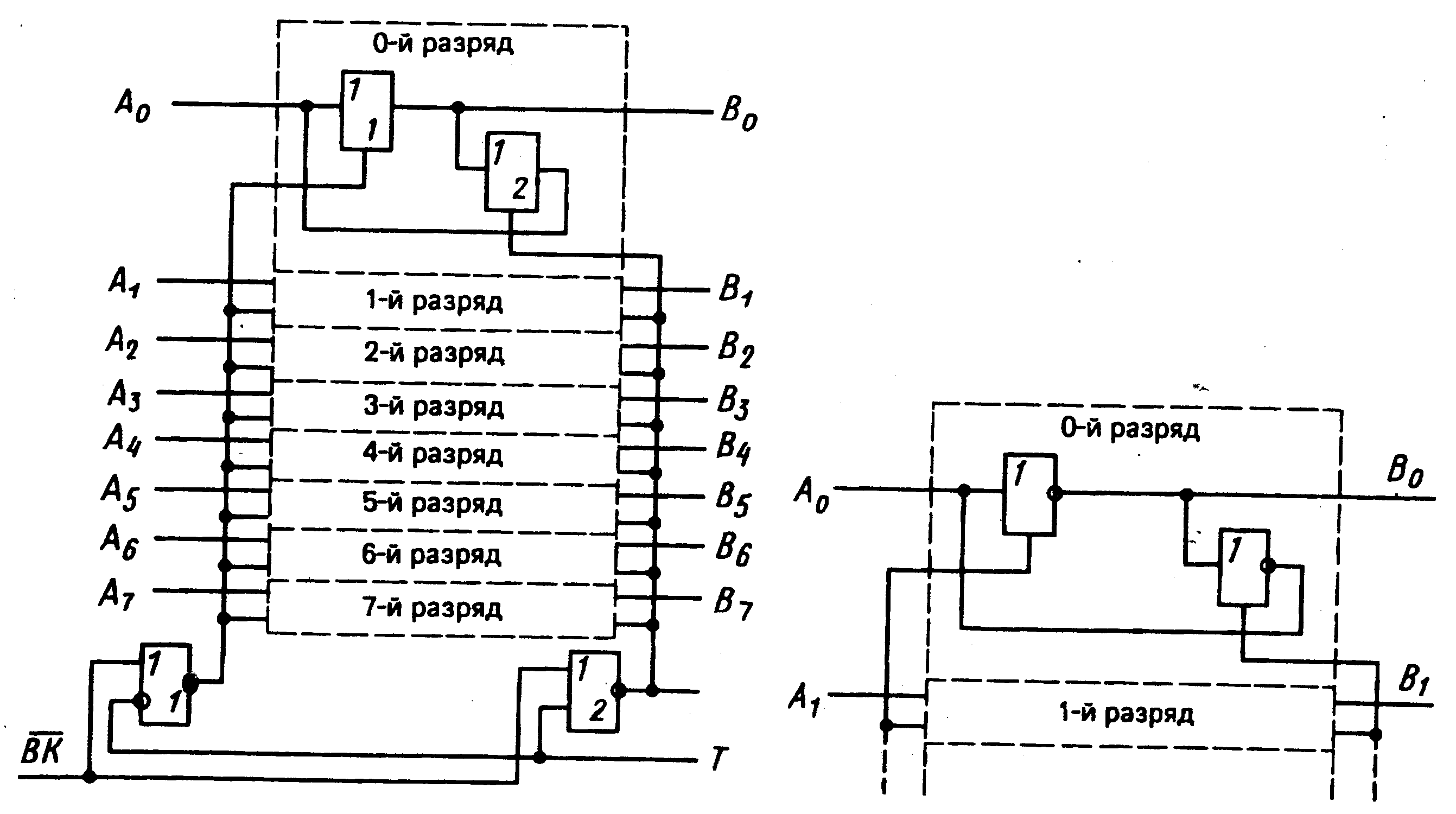

По

данной схеме осущ. пд 8-разр. данных,

причём подробно изображён лишь 0-й

разряд. В этом разряде имеются 2

повторителя, причём если один из них

включён, то другой д.б. обязательно

выключен. Управление состояниями

повторителей

осущ.

элементами ИЛИ-НЕ при помощи упр.сигналов

ВК и Т:

Выходы

В (при пд от А к В) имеют большую

нагр.способн., чем А:

I0вых≤32mA,

I1вых≤5mA;

для

выходов А:

I0вых≤10mA,

I1вых≤1mA;

Очевидно,

что к вых.А шин.формирователя подключаются

к выводам CPU,

а B

– к

системным ША и ШД.

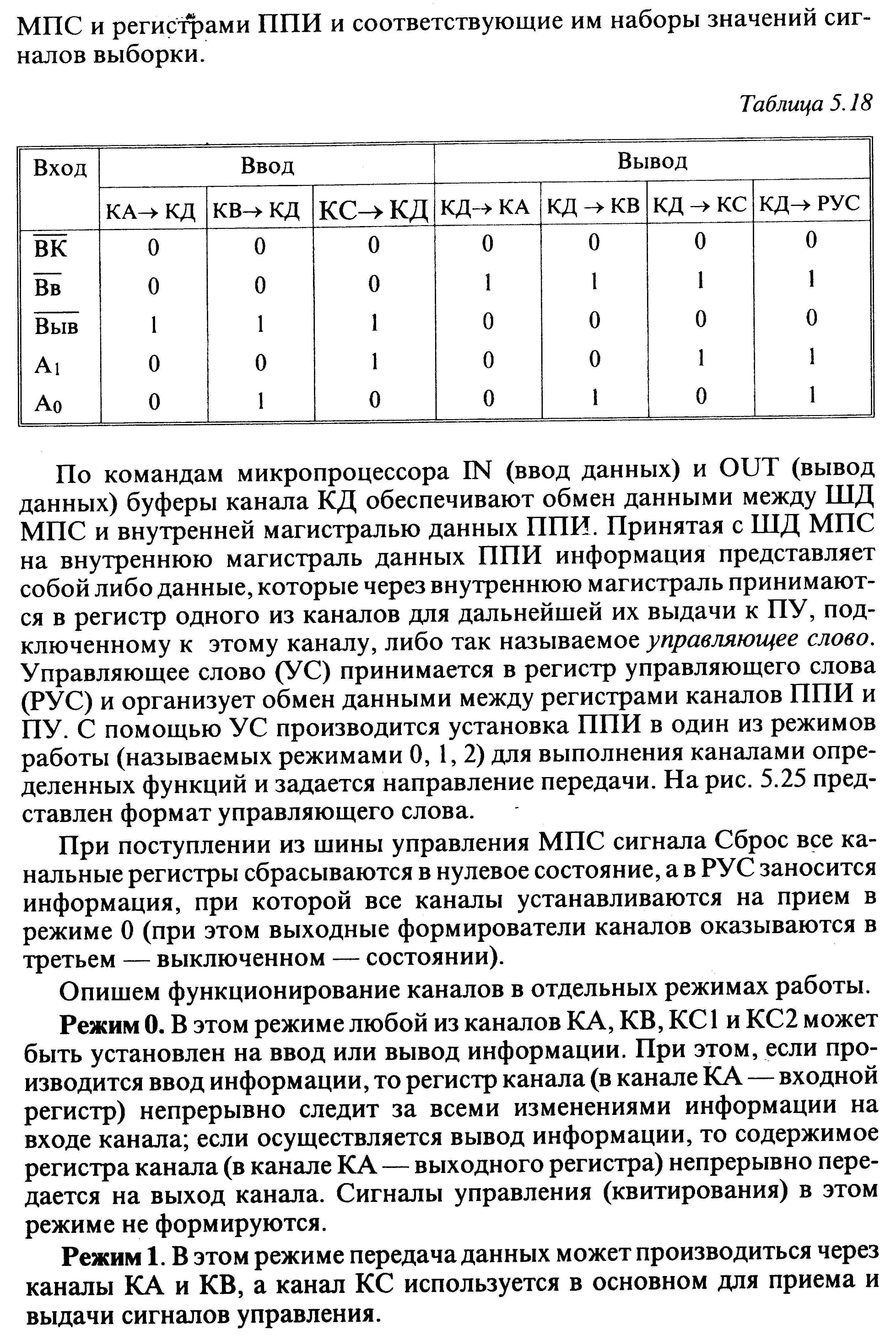

БУФЕРЫ

Шины Адреса.

Т .к.

данный буфер имеет 16 разрядов, то

потребуется 2 8-разр. шинных формирователя,

причём ША–однонаправл., т.е. пд осущ. от

CPU

к

внеш.Ус.

.к.

данный буфер имеет 16 разрядов, то

потребуется 2 8-разр. шинных формирователя,

причём ША–однонаправл., т.е. пд осущ. от

CPU

к

внеш.Ус.

Если

на выходе 'подтв.захв.'

CPU лог.1,

то все повторители находятся в Z-сост.

независимо от T.

Если лог.0, то на вых. И тоже 0 и осущ. пд

инфы от А к В по ША, т.к. на Т – лог. 1 от

ИП.

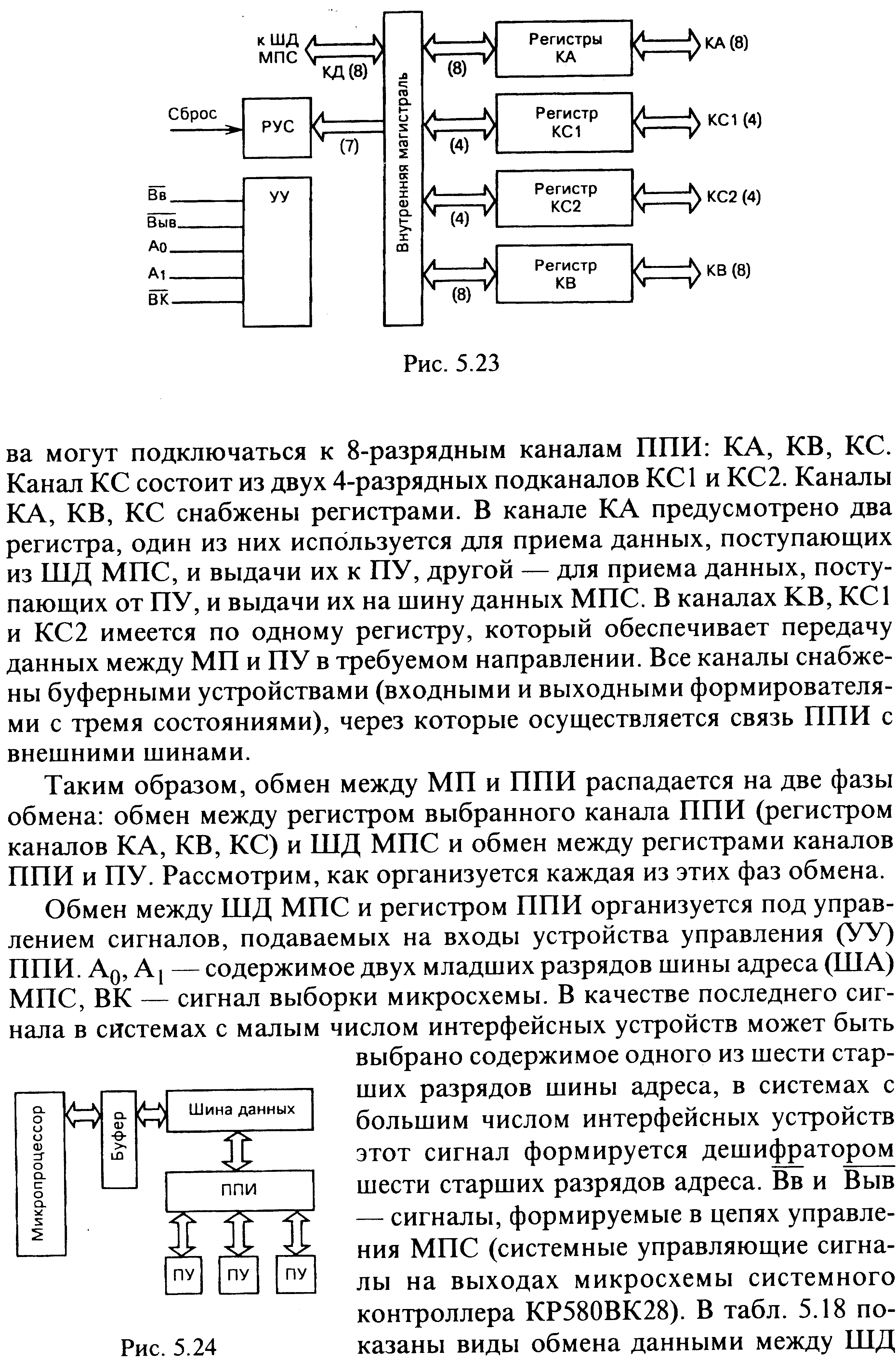

БУФЕРЫ

Шины Данных.

Имеет

8 разрядов и является двунаправленной,

т.е пд инфы и от CPU

к

внеш.Ус(АВ);

от внеш.Ус к CPU

(ВА).

Пд данных организуется под управлением

сигналов неВК и Т.

.к.

данный буфер имеет 16 разрядов, то

потребуется 2 8-разр. шинных формирователя,

причём ША–однонаправл., т.е. пд осущ. от

CPU

к

внеш.Ус.

.к.

данный буфер имеет 16 разрядов, то

потребуется 2 8-разр. шинных формирователя,

причём ША–однонаправл., т.е. пд осущ. от

CPU

к

внеш.Ус.