- •Прикладна теорія цифрових автоматів

- •Загальні методичні вказівки

- •Тема: Проектування спеціалізованих арифметико-логічних пристроїв

- •Методичні вказівки до виконання курсової роботи

- •Загальні відомості

- •1. Вибір схеми операційного автомату та опис його роботи.

- •2. Принципіальна схема модуля операційного блока (моб).

- •3. Приведення змістовного алгоритму виконання операції.

- •Граф-схеми мікропрограми ка.

- •5. Проектування модуля ка.

- •Структурний синтез автомата Мілі

- •Побудова схеми керуючого автомата

- •Структурний синтез автомата Мура

- •Зауваження

- •Література

- •Проектування спеціалізованих арифметико-логічних пристроїв

- •1. Реалізація операції додавання і віднімання

- •1.1. Алгоритм додавання і віднімання двійкових чисел

- •1.2. Функціональна схема алп для виконання операцій додавання і віднімання

- •1.3. Мікропрограма додавання та віднімання двійкових чисел

- •2. Реалізація операції множення

- •2.1. Алгоритм множення двійкових чисел із зсувом суми часткових добутків вправо

- •2.2. Функціональна схема алп для операції множення

- •2.3. Мікропрограма множення цілих чисел

- •2.4. Перший алгоритм множення у прямому коді.

- •2.5. Другий алгоритм множення у прямому коді.

- •2.6. Третій алгоритм множення у прямому коді.

- •2.7. Четвертий алгоритм множення у прямому коді.

- •3. Реалізація операції ділення

- •3.1. Алгоритм ділення цілих чисел

- •3.2. Функціональна схема алп для мікропрограми ділення

- •3.3. Мікропрограма ділення цілих чисел без відновлення залишку

Література

-

Е. Угрюмов. Цифрова схемотехника. – Санкт-Петербург, БХВ – Петербург 2002.

-

Самофалов К.Г., А.М. Романкевич та ін. Прикладна теорія цифрових автоматів. – К.: Вища шк. 1987.

-

Г.Н. Пухальський. Т.Я. Новосєльцев, Довідник. Проектування дискретних пристроїв на інтегральних схемах. М.: Радіо і зв’язок, 1990.

-

М.П. Бабич, І.А. Жуков. Комп’ютерна схемотехніка: Навчальний посібник. – К.: «МК - Прес», 2004

-

В.І. Бойко, А.М. Гурій, В.Я. Жуйков та інші. Цифрова схемотехніка; кн. 2. Київ,: Вища школа, 2004.

-

Бойко В.И. и др. Схемотехника электронных систем. Цифровые устройства. – СПб.: БХВ – Петербург, 2004.

-

Савельев П.В., Коняхин В.В. Функционально-логическое проектирование БИС. – М.: «Высшая школа». 1990.

-

Кузин А.В., Жаворонков М.А. Микропроцесорная техника: Учебное пособие. – М.: Издательский центр «Академия», 2004.

-

Основи цифрових систем/У.П. Барбаш, М.П. Благодарний та ін. – Підручник. – Харків. Нац. Аерокосмічний ун-т. «харк. авіац. ін-т», 2002.

-

Дж. Ф. Уэйкерли. Проектирование цифровых устройств. Учебник. – М.: Постмаркет, 2002.

Додаток

Проектування спеціалізованих арифметико-логічних пристроїв

1. Реалізація операції додавання і віднімання

1.1. Алгоритм додавання і віднімання двійкових чисел

Алгоритм додавання та віднімання двійкових чисел можна виконувати в обернених або доповняльних кодах. У сучасних комп'ютерах часто операнди зберігаються у пам'яті і оброблюються в доповняльних кодах, перевагу яких описано в розділі 1.

Алгоритм додавання (код команди К[Ц] або віднімання (код команди К[2] виконується у такій послідовності:

-

у регістри RGA 1 RGB із вхідної шини один за одним паралельним кодом записуються відповідні їм операнди А і В;

-

під час операції віднімання (код команди К[2] = 1) операнд В безумовно інвертується;

-

мікрооперації додавання або віднімання виконуються в доповняльних кодах протягом одного машинного такту;

-

аналізується результат операції. За відсутності переповнення розрядної сітки (знаки операндів А і В та результату збігаються) результат записується у регістр RGD і потім пересилається в оперативну пам'ять, за наявності переповнення (знаки операндів А і В та результату на виході суматора не збігаються) результат не фіксується і в ЦПК подається сигнал переповнення ІШ.

1.2. Функціональна схема алп для виконання операцій додавання і віднімання

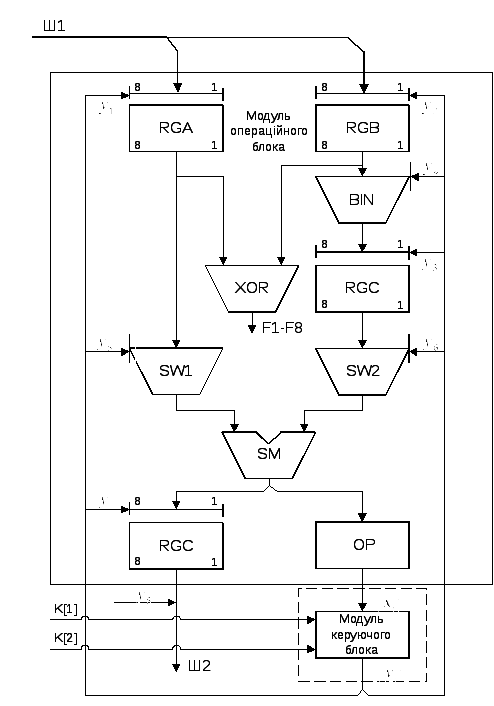

Функціональну схему восьмирозрядного АЛП для виконання мікропрограми додавання та віднімання подано композицією модуля операційного блока МОБ і моду-щ керуючого блока МКБ (рис. 3).

Схема містить:

-

регістри RGA і RGB для приймання із вхідної шини ІШ операндів А і В та їх зберігання протягом часу виконання мікропрограми;

-

схему інвертування BIN змісту регістра RGB;

-

схему XOR для порозрядного логічного "виключне АБО" кодів операндів А і В;

-

схеми електронних ключів SWI і SW2 для комутації операндів;

-

комбінаційний суматор SM. На вхід перенесення суматора подається лог. 1 при операції віднімання;

-

регістр результату RGD;

-

схему ознаки переповнення ОР;

-

модуль керуючого блока МКБ на основі автомата Mini з пам'яттю на D-тригерах.

Продовження додатку

Рис.1. Функціональна схема АЛП для додавання і віднімання чисел