- •Прикладна теорія цифрових автоматів

- •Загальні методичні вказівки

- •Тема: Проектування спеціалізованих арифметико-логічних пристроїв

- •Методичні вказівки до виконання курсової роботи

- •Загальні відомості

- •1. Вибір схеми операційного автомату та опис його роботи.

- •2. Принципіальна схема модуля операційного блока (моб).

- •3. Приведення змістовного алгоритму виконання операції.

- •Граф-схеми мікропрограми ка.

- •5. Проектування модуля ка.

- •Структурний синтез автомата Мілі

- •Побудова схеми керуючого автомата

- •Структурний синтез автомата Мура

- •Зауваження

- •Література

- •Проектування спеціалізованих арифметико-логічних пристроїв

- •1. Реалізація операції додавання і віднімання

- •1.1. Алгоритм додавання і віднімання двійкових чисел

- •1.2. Функціональна схема алп для виконання операцій додавання і віднімання

- •1.3. Мікропрограма додавання та віднімання двійкових чисел

- •2. Реалізація операції множення

- •2.1. Алгоритм множення двійкових чисел із зсувом суми часткових добутків вправо

- •2.2. Функціональна схема алп для операції множення

- •2.3. Мікропрограма множення цілих чисел

- •2.4. Перший алгоритм множення у прямому коді.

- •2.5. Другий алгоритм множення у прямому коді.

- •2.6. Третій алгоритм множення у прямому коді.

- •2.7. Четвертий алгоритм множення у прямому коді.

- •3. Реалізація операції ділення

- •3.1. Алгоритм ділення цілих чисел

- •3.2. Функціональна схема алп для мікропрограми ділення

- •3.3. Мікропрограма ділення цілих чисел без відновлення залишку

3. Реалізація операції ділення

3.1. Алгоритм ділення цілих чисел

Операція ділення цілих чисел Z=XIY зводиться до послідовності віднімання дільника Y спочатку від діленого X, а потім від створюваних в процесі ділення залишків R,.

Залежно від способу віднімання дільника У розрізняють два основні алгоритми ділення: без відновлення залишку R1 та з відновленням залишку. Обидва способи реалізуються приблизно однаковими апаратними затратами, але для ділення без відновлення залишку потрібно більше мікрооперацій додавання і віднімання. В універсальних комп'ютерах зазвичай використовують ділення без відновлення залишку.

У разі ділення цілих чисел часто ділене Х подається в 2n-розрядному форматі, а дільник Y - у n-розрядному.

Алгоритм ділення цілих чисел у прямому коді без відновлення залишку реалізується в такій послідовності.

-

У регістри А, В і С послідовно записуються із вхідної шини n-розрядний дільник Y та 2n-розрядне ділене X. У лічильник циклів СТ заноситься число циклів n-1.

-

Ділене X та дільник Y аналізуються на рівність нулю. Якщо ділене X = 0, то частці Z присвоюється нульове значення і ділення закінчується. Якщо дільник Y - 0, то ділення переривається.

-

Установлюється можливість ділення без переповнення розрядної сітки. Для цього значення діленого подвоюється зсувом вліво на один розряд. Із зсунутого діленого віднімається дільник. Операція віднімання дільника замінюється на його додавання у доповняльному коді і визначається перший залишок R0 за формулою:

![]()

Якщо R0< 0 , то ділення можливе; якщо RQ ≥ 0, виникає переповнення розрядної сітки і ділення припиняється.

-

Якщо ділення можливе, виконуються такі основні дії:

-

частковий залишок в регістрі В і зміст регістра С зсуваються вліво на один розряд (тобто подвоюються);

-

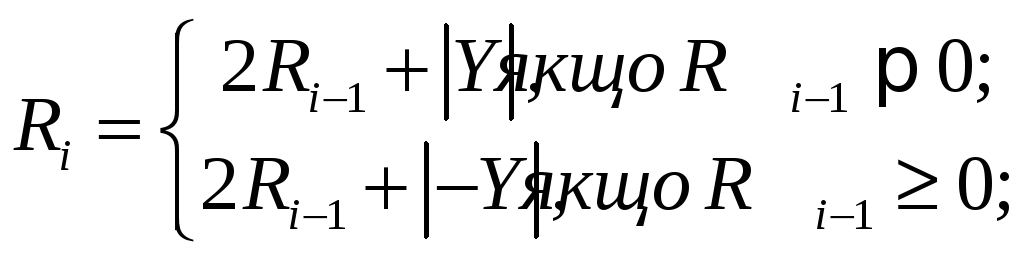

із зсунутого залишку віднімається дільник, якщо попередній залишок Ri-1≥0, або додається, якщо Ri-1<0, Дм <0. Це визначається рекурентним співвідношенням:

де i = 1, 2, ... , n-1.

-

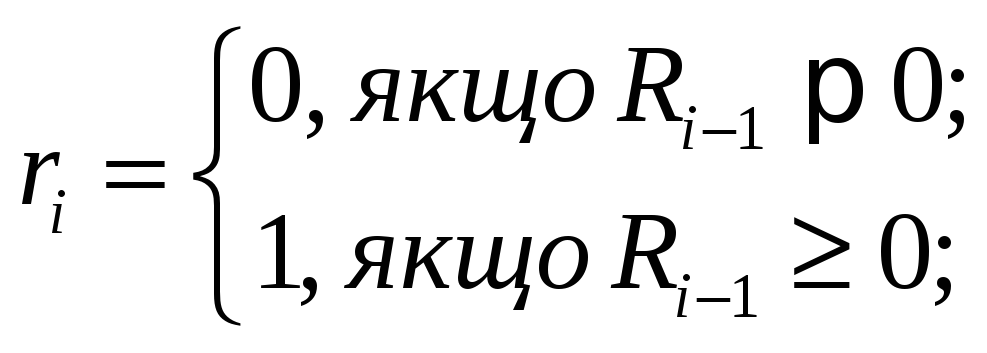

якщо відбувається зсув вліво, в молодший розряд регістра С записується цифра частки rі, згідно із співвідношенням

Продовження додатку

Це означає, що поточна цифра частки є інверсією знака залишку;

-

зміст лічильника циклів СТ зменшується на одиницю;

-

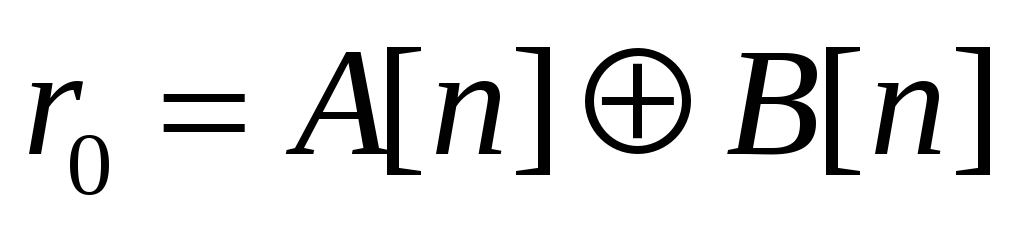

п. 4 повторюється до обнулення лічильника циклів СТ. Значення першого (старшого) розряду частки відводиться для записування знака результату на підставі виразу

.

.

5. Залишок ділення розміщується у регістрі В на місці старших розрядів діленого, а частка — в регістрі С. Дільник, залишок і частка мають формат n-розрядного числа із знаком. Залишок має мати той же знак, що і ділене, нульові залишки і частки завжди додатні. Якщо знак останнього залишку від'ємний, то він коректується додаванням до нього модуля дільника, після цього залишку присвоюється знак діленого,

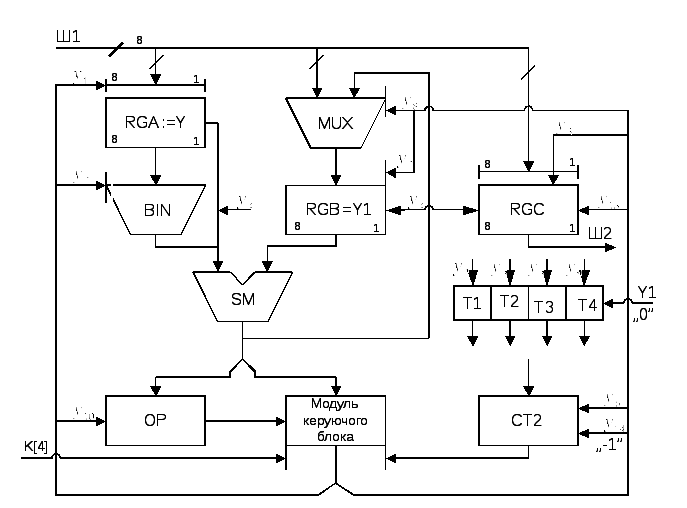

3.2. Функціональна схема алп для мікропрограми ділення

Функціональну схему АЛП для виконання мікропрограми ділення показано на рис. 5.

Рис. 3. Функціональна схема АЛП для операції ділення

Показана схема АЛП містить:

-

регістр RGA для приймання восьмирозрядного дільника У;

-

регістри RGB і RGC дня приймання 16-розрядного діленого X;

-

комбінаційний восьмирозрядний суматор SM;

Продовження додатку

-

мультиплексор MUX; який забезпечує записування інформації RGB із вхідної шини ШІ або з виходів суматора SM;

-

схему BIN для подання прямого або оберненого коду дільника на входи суматора SM;

-

лічильник кількості циклів СТ;

-

схему вироблення ознак результату ОР;

-

тригери Г1-Г4 для створення другого рівня керування модулем операційного блока МОБ5;

-

місцевий керуючий блок МКБ5 на основі автомата Мілі з пам'яттю на JK-тригерах.