- •1. Інформаційні технології схемотехнічного проектування в радіоапаратобудуванні

- •1.1. Мета, завдання, основи автоматизації проектування ез

- •1.1.1. Загальні положення

- •1.1.2. Зміст дисципліни.

- •1.1.3. Основи інформаційних технологій схемотехнічного проектування ез

- •1.2 Загальнi положення I класифікація моделей ез

- •1.2.1 Загальні положення

- •1.2.2. Класифікація моделей

- •1. 3. Параметри моделей і їх iдентифікація

- •2. Інформаційні технології моделювання компонентів ез

- •2. 1. Моделі пасивних компонентів ез

- •2. 1. 1. Загальні положення

- •2. 1. 2. Моделі пасивних елементів

- •2. 2. Моделі активних компонентів

- •2. 2. 1. Моделі активних елементів

- •2. 2. 2. Моделі активних компонентів

- •2. 3. Гiпермоделi активних компонентів

- •2. 3. 3. Гiпермодель біполярного та уніполярного транзисторів

- •3.1.2. Типові каскади оп та їх моделі

- •3. 1. 3. Три типи макромоделей оп

- •4.2. Гiпермоделi оп

- •3. 3. Макромоделi аналогових пристроїв на базі оп і перемножувачів

- •3. 3. 1. Макромоделi лiнійних безінерційних пристроїв на оп

- •3. 3. 2. Нелiнійні безінерційні пристрої на основі оп

- •3. 3. 3. Моделі лiнійних динамічних пристроїв на оп

- •3. 3. 4. Макромоделi аналогових пристроїв на основі перемножувачів

- •3. 4. 2. Моделювання аналогових пристроїв в частотній області

- •I1потр, i0потр, u1, u0.

- •4. 3. Макромоделi цифрових пристроїв ез

- •4. 3. 1. Моделі вхідних каскадів цифрових пристроїв ез

- •4. 4. 2. Моделі порогових функцій і логічніх елементів, що управляються

- •4. 4. 3. Моделювання цап і ацп

- •5.1.2. Топологічні матриці схеми ез

- •5.1.3. Вибір компонентного базиса і топологічних матриць

- •5.2. Методи подання стану схеми ез

- •5.2.1. Табличний метод

- •5.3.2. Метод опису статики лiнійних пристроїв ез

- •5.3.3. Методи опису статики нелiнійних пристроїв ез

- •5.4. Методи опису динамічних функціональних властивостей ез

- •5.4.1. Загальні положення

- •5.4.2. Явні методи

- •5.4.3. Неявні методи

- •6.1.4 Декомпозиція логічних функцій

- •6.1.5. Реалізація функціонально-логічних властивостей цифрових ез

- •6.2. Методи моделювання функціонально-логічних схем

- •6.2.1. Синхронне моделювання

- •6.2.2. Асинхронне моделювання

- •6.2.3. Моделювання функціонально-логічних схем на основі трьохзначної логіки

- •6.2.4. Моделювання функціонально-логичних схем на основі п’ятизначної логіки

6.1.4 Декомпозиція логічних функцій

f( x1, x2, ..., xk, ..., xn) = xk f0 (x1, x2, ..., xk-1, xk+1..., xn) +

+ xk f1 (x1, x2, ..., xk-1, xk+1..., xn),

f0 (x1, x2, ..., xk-1, xk+1..., xn) = f Xk = 0

f1 (x1, x2, ..., xk-1, xk+1..., xn) = f Xk = 1

6.1.5. Реалізація функціонально-логічних властивостей цифрових ез

Функціонально повні набори

Логичний елемент звичайно виконує одну логічну функцію.

Будь-яку функцію можна реалізувати на елементах І, ІЛІ, НЕ. Цей набір є iзбиточним. Повними є І-НЕ, ІЛІ-НЕ, стрілка Пiрса, штриіт Шефера. Для простоти реалізації використають iзбиточний набір.

Два напряму реалізації: комбiнаційні схеми; послідовністi.

Комбiнаційні описуються:

W (k) = F [X(k)]

Послідовні описуються:

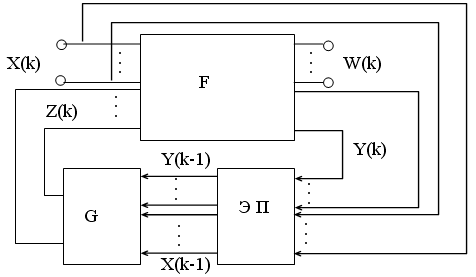

W (k) = F [X(k), Z(k)], Z (k) = G [X(k-1), Y(k-1)]

При функціонально-логичном моделюваннi цифрових ЕЗ використовуються слідуючі особливості:

-

стан елементів характеризується перемінними одного типу (не конкретизуються I, U т. і.);

2) перемінна приймає дискретні значення (0, 1 або декілька рівней);

3) аналіз схем діється в дiскретні моменти часу по тактам, при цьому зміна хоч би однієї перемінной називається подією.

6.2. Методи моделювання функціонально-логічних схем

Моделювання функціонально-логичних схем ЕЗ здійснюється на основі синхронного, асинхронного моделювання і моделювання на основі богатозначної логіки. Синхронне - описує роботу схеми без обліку затримок, асинхронне - враховує фіксовані затримкi, а богатозначна логіка - дозволяє

враховувати ризик статичного і динамічного сбоя.

6.2.1. Синхронне моделювання

Усі сигнали Про {0, 1}, усі затримки дорівнюють нулю. Стан елементів пам'яті за такт змінюється один раз. Стан системи описується:

yi(k) = fi[x1(k), ...xn(k), y1(k), ... ym(k)], i = 1, m

Вирішує, використовуючи засіб простій iтерацiї:

yi(p+1)(k) = fi[x(k), y1(p)(k), ... ym(p)(k)], i = 1, m

Iтерація діється до виконання умови:

yi(p+1)(k) = yi(p)(k) , i = 1, m

Цей засіб вимагає великих ресурсів, тому на практиці часто використовують засіб Зейделя:

При цьому, необхідно застосовувати ранжiровання. R=0- для вхідних сигналів. Але цей приклад для нагоди відсутності зворотних зв'язків.

Якщо при цьому: процес закінчений, якщо немає- знов перевіряємо умову. Одержуємо діаграму.

6.2.2. Асинхронне моделювання

- элемент затримки;

Zk - сигнал збудження, {Zk(k)} R;

Yk - сигнал реакції, {Yk(k)} P.

Асинхронне моделювання сводиться до обчислення функцій, що виконуються окремими елементами схеми. При цьому аргументи беруться з безлічі Р, а обчислені значення записуваються в масив R (збудження). Кожний розрахунковий такт відповідає одному такту роботи.

За цей такт сигнал минає на один елемент схеми наперед. Порядок обчислення Yk проiзволен, вихідні надані беруться з одного масиву і передаються в інший. Після кожного розрахунку діється пеЕАапис з масиву R в масив P, що і є iмiтація затримкі. Для обчислення скорочування застосовують собитійне моделювання. Для цього вводять масив А:

A(k) = 0 - якщо стан не змінюється

1 - якщо змінюється

6.2.3. Моделювання функціонально-логічних схем на основі трьохзначної логіки

З метою вияву можливості ризика сбою і критичних состязаній, в схемах з затримкою застосовується трьохзначна логіка.

Критични состязання - це наявність в схемах ряду елементів, що переключають пам'ять з ризиком сбою. Наприклад, розглянемо таблицю iстиностi:

x1 x2 x1 x2

|

x1\ x2 |

0 |

1/2 |

1 |

|

|

|

x1\ x2 |

0 |

1/2 |

1 |

|

0 |

0 |

0 |

0 |

|

|

|

0 |

0 |

1/2 |

1 |

|

1/2 |

0 |

1/2 |

1/2 |

|

|

|

1/2 |

1/2 |

1/2 |

1 |

|

1 |

0 |

1/2 |

1 |

|

|

|

1 |

1 |

1 |

1 |

= min (xi ), i = 1, m = max (xi), i = 1, m

X = 1–X

Моделювання трьохзначної логіки виробляється не тільки для вихідних Х, але і для перехідних сигналів.

A = {a1, ..., an} и

B = {b1, ... ,bm}, то будують:

C = {C1, ..., Cm}

Якщо f(A)=f(B) і f(C)=1/2, оте кажуть, що є ризик сбою. На основі трьохзначної логіки можна аналізувати критичні состязання, але при цьому зворотні зв'язки розривають і вводять ранжiровання як в асинхронному випадку. Якщо внаслідок аналізу визначимо, що сигнал дорівнює 1/2, то це означає, що є ризик сбоя.