Вопрос 24

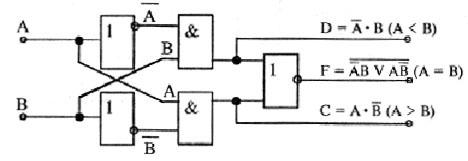

Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел А и В с одинаковым количеством разрядов либо вид неравенства А>В или А<В. Цифровые компараторы имеют три выхода.

Схема одноразрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ–НЕ»

|

Входы |

Выход |

|||||

|

ai |

bi |

A < B |

A = B |

A > B |

||

|

0 |

0 |

0 |

1 |

0 |

||

|

0 |

1 |

1 |

0 |

0 |

||

|

1 |

0 |

0 |

0 |

1 |

||

|

1 |

1 |

0 |

1 |

0 |

||

|

|

|

|

|

|

|

|

Вопрос 25

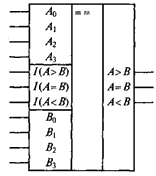

Многоразрядные компараторы

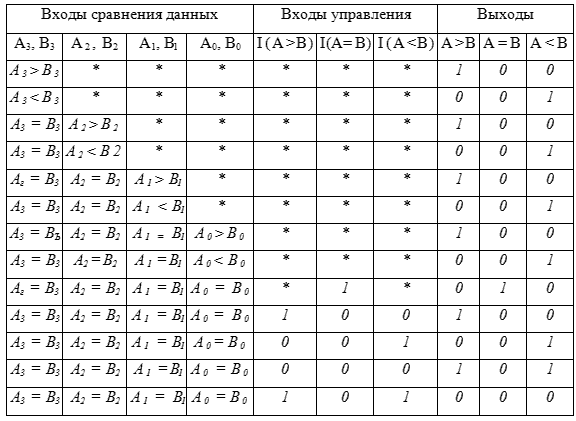

Рассмотрим в качестве примера четырехразрядный цифровой компаратор серии К555СП1, восемь входов которого служат для подключения двух четырехразрядных слов: А0 ... А3, В0 ... B3, подлежащих сравнению (рис. 11.2). Управляющие входы I(А> В), I(А = В) и I(А < В) могут быть использованы для наращивания разрядности компаратора. Предусмотрены три выхода результата сравнения: А> В, А = В и А<В.

Таблица истинности такого компаратора (табл. 11.2) разбита по строкам на три раздела.

Первый раздел (восемь верхних строк таблицы) определяет тот случай работы компаратора, когда подлежащие сравнению четырехразрядные слова не равны друг другу. При этом сигналы на входах наращивания разрядности как реакция на сигналы более младших разрядов сравниваемых слов никакого влияния на результат сравнения не оказывают. Три строки второго раздела этой таблицы характеризуют работу компаратора с последовательным способом наращивания разрядности, т.е. когда выходы компаратора младших разрядов подключены к управляющим входам компаратора старших разрядов

Вопрос 27

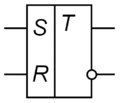

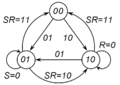

RS - триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, в некоторых случаях является запрещённым, при такой комбинации RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний).

|

S |

R |

Q(t) |

Q(t) |

Q(t+1) |

Q(t+1) |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |