- •Характеристики

- •Аппаратные средства

- •Схема Тестера

- •Улучшения и расширения к прибору

- •Защита портов ATmega

- •Измерение стабилитронов с напряжением более 4 V

- •Генератор частоты

- •Измерение частоты

- •Использование поворотного энкодера

- •Подключение графического дисплея

- •Подключение графического цветного дисплея

- •Указания по сборке Тестера

- •Доработки для версий Тестера Markus F.

- •Китайские клоны с символьным дисплеем

- •Китайские клоны с графическим дисплеем

- •Расширенная схема с ATmega644 или ATmega1284

- •Схема с использованием ATmega1280 или Arduino Mega

- •Программирование микроконтроллера

- •Использование Makefile в ОС Linux

- •Использование программы WinAVR в ОС Windows

- •Поиск неисправностей

- •Инструкция пользователя

- •Проведение измерений

- •Меню дополнительных функций для ATmega328

- •Самопроверка и калибровка

- •Специальные возможности использования

- •Проблемы при определении элементов

- •Измерение ёмкости конденсаторов

- •Измерение индуктивности

- •Конфигурирование Тестера

- •Описание процедур измерения

- •Измерение полупроводниковых элементов

- •Измерение диодов

- •Результаты различных измерений

- •Измерение резисторов

- •Измерение резистора с резисторами 680 Ом

- •Измерение резистора с резисторами 470 кОм

- •Результаты измерений резистора

- •Измерение конденсаторов

- •Разрядка конденсатора

- •Измерение конденсаторов большой ёмкости

- •Измерение конденсаторов малой ёмкости

- •Измерение эквивалентного сопротивления ESR

- •Измерение ESR, первый метод

- •Измерение ESR, второй метод

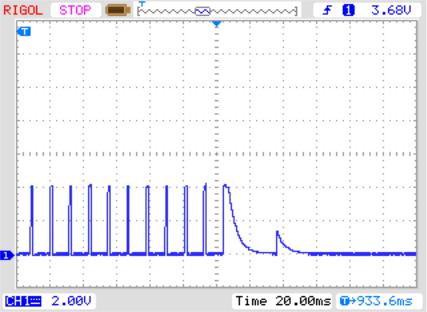

- •Потеря напряжения после импульса зарядки, Vloss

- •Отдельное измерение ёмкости и ESR

- •Результаты измерения ёмкости конденсаторов

- •Автоматическая калибровка при измерении конденсаторов

- •Измерение индуктивностей

- •Результаты измерений индуктивности

- •Функция самопроверки

- •Некоторые результаты функции самопроверки

- •Измерение частоты

- •Генератор сигналов

- •Генератор частоты

- •Известные ошибки и проблемы

- •Специальные модули программного обеспечения

- •Список текущих дел и новые идеи

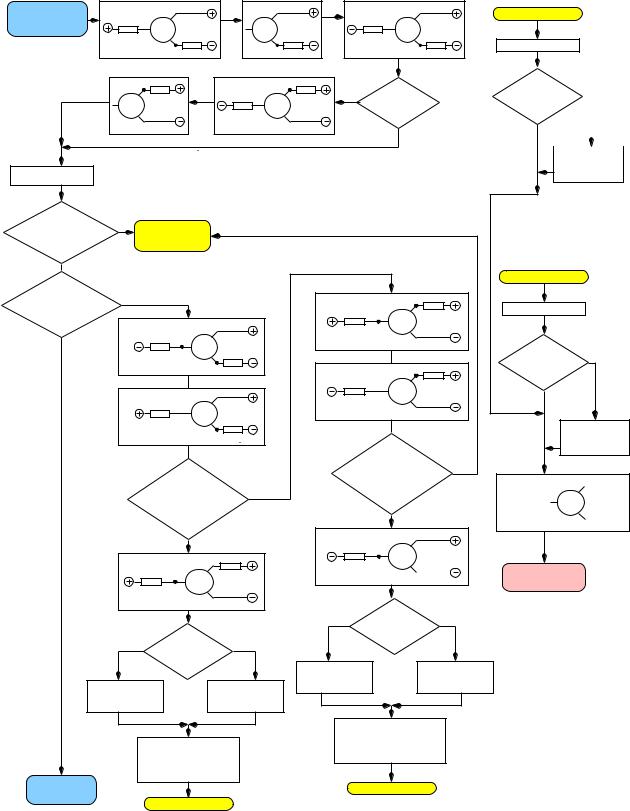

5.1Измерение полупроводниковых элементов

Исследование элемента необходимо начинать с обесточенным управляющим выводом (третий вывод, назван TriStatePin). TriStatePin исследуемого элемента во время испытания является базовым или отправным. Один испытательный вывод выбран положительной стороной элемента и подключен непосредственно к VCC. Другой испытательный вывод выбран отрицательной стороной элемента. Отрицательная сторона подсоединена через резистор 680 к GND. Состояние полевых транзисторов зависит от напряжения на затворе. Сначала, TriStatePin на 5 подключается через резистор 680 Ом к GND и измеряется напряжение на отрицательной стороне. Далее TriStatePin переключается на Ввод (высокое полное входное сопротивление) и снова измеряется напряжение отрицательного испытательного вывода. Затем предполагаемый затвор соединяется через резистор 680 на 5 к VCC и снова измеряется напряжение на отрицательной стороне. Если измеренное напряжение ниже первого результата измерения, то эта схема будет предполагаться, как правильная. Затем напряжение снова измеряется с обесточенным TriStatePin.

Если напряжение отрицательного испытательного вывода с фиксированным напряжением TriStatePin выше чем 115 , а с обесточенным TriStatePin не ниже 100 , предполагается, что это обеднённый транзистор.

У биполярных транзисторов, имеющих повышенный обратный ток коллектора, он значительно повышается в режиме с обесточенной базой.

При проверке с обоими напряжениями можно избежать неправильного обнаружения некоторых германиевых транзисторов с более высоким обратным током коллектора, как обедненных транзисторов (JFET).

Далее проводятся дополнительные тесты по определению N-канального JFET или N D- MOSFET и P-канального JFET или P-D MOSFET. Версии MOSFET могут быть определены по отсутствующему току затвора при любом состоянии TriStatePin.

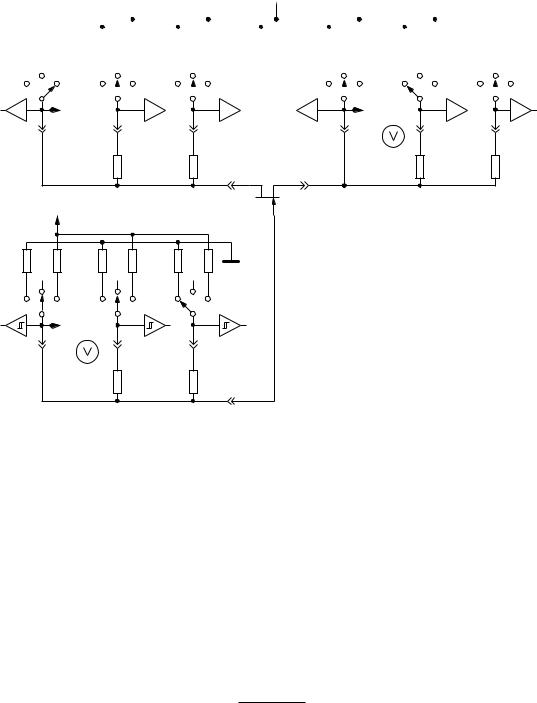

Чтобы получить параметры FET обеднённого типа, их измеряют с резистором 680 в истоке, как показано на рисунке 5.3 . Это измерение делается вместо обычного измерения тока удерживания затвора на уровне истока, потому, что DSS FET транзистора часто не может быть достигнуто из-за относительно высокого сопротивления резистора 680 .

62

VCC

VCC

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

|

22 |

|

|

19 |

|

|

22 |

|

|

19 |

|

|

|

22 |

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

22 |

|

|

19 |

|

|

22 |

|

|

19 |

|

|

22 |

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADCMUX |

|

|

|

|

|

PC0 |

PB0 |

|

PB1 |

|

|

|

|

680 |

R1 |

470K |

R2 |

TP1 D S TP3 |

|

|

VCC |

|

|

|

G |

19 |

22 |

19 |

22 |

19 |

22 |

|

|

|

|

|

|

|

GND |

ADCMUX |

|

|

|

PC2 |

PB4 |

|

PB5 |

680 |

R5 |

470K |

R6 |

ADCMUX |

|

|

|

PC1 |

PB2 |

|

PB3 |

680 |

R3 |

470K |

R4 |

TP2

Рис. 5.3. Измерение напряжения затвор-исток и тока истока N-JFET транзистора

Если у элемента нет тока между положительным и отрицательным испытательными выводами без сигнала на TristatePin, то переходим к тестам определения, описанным в разделе 5.1.1. Если ток был обнаружен, то следующий тест описан в 5.1.4 о диодах.

5.1.1Измерение P-N-P транзистора или P-Channel-MOSFET

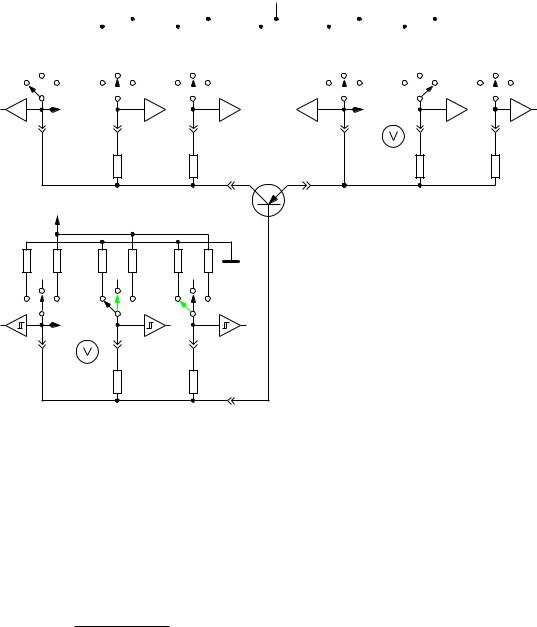

Сначала измеряют коэффициент усиления предполагаемого P-N-P транзистора в схеме с общим коллектором (эмиттерный повторитель). Схема измерения показана на рисунке 5.4. Если напряжение базы ( ) измеренное с резистором 680 , выше 9 , то коэффициент усиления

вычисляется по формуле = − . Напряжение это разность между напряжением на

эмиттере и VCC. Различие между резисторами 22 и 19 не учитывается. Если напряжениениже 10 , измерение делают с резистором 470 в базе. В этом случае коэффициент

усиления вычисляется по формуле = ·470000 .

·(680+22)

63

VCC

VCC

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

|

22 |

|

|

19 |

|

|

22 |

|

|

19 |

|

|

|

22 |

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

22 |

|

|

19 |

|

|

22 |

|

|

19 |

|

|

22 |

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADCMUX |

|

|

|

|

|

PC0 |

PB0 |

|

PB1 |

|

|

|

|

680 |

R1 |

470k |

R2 |

TP1 |

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

|

19 |

22 |

19 |

22 |

19 |

22 |

GND |

|

|

|

|

|

|

|

|

|

ADCMUX |

|

|

|

|

|

PC1 |

PB2 |

|

PB3 |

|

|

|

|

680 |

R3 |

470k |

R4 |

TP2 |

|

|

|

|

|

|

|

|

ADCMUX |

|

|

|

|

PC2 |

PB4 |

|

PB5 |

TP3 |

680 |

R5 |

470k |

R6 |

|

|

|

|

The green switch state is used if Voltage at PC1 is < 10mV !

Рис. 5.4. Измерение hFE P-N-P транзистора в схеме с общим коллектором

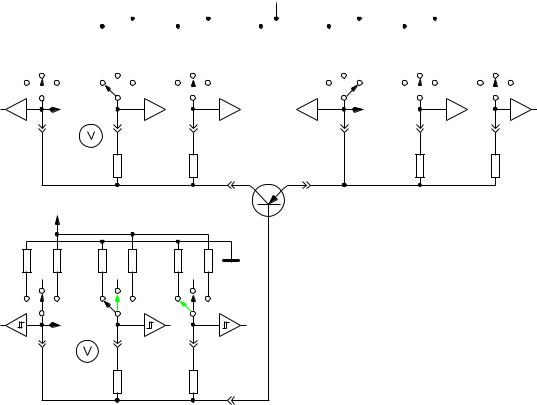

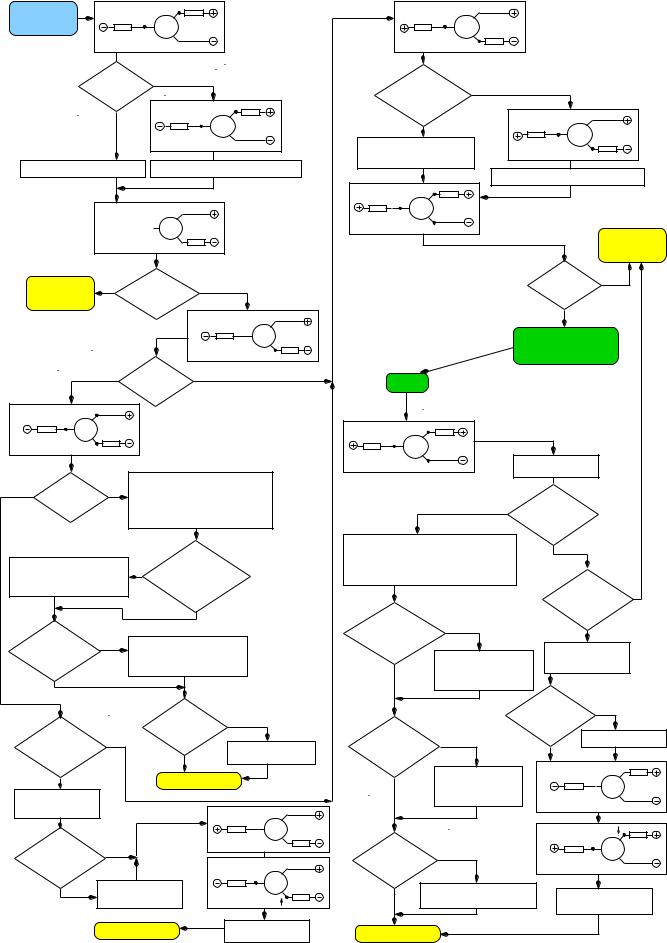

Затем делают тесты для предполагаемого P-N-P транзистора в схеме с общим эмиттером. Положительная сторона элемента теперь подключена прямо с VCC, отрицательная сторона через резистор 680 подключена к GND, как показано на рисунке 5.5. Если на отрицательной стороне элемента есть напряжение выше 3, 4 , когда базовый резистор 680 подключен к GND, значит этот элемент или P-N-P транзистор или P канальный FET. Какой из них - может быть легко установлено по напряжению базы. Если напряжение базы больше 0, 97 , это должен быть P-N-P транзистор. Для того, чтобы измерить коэффициент усиления, в цепь базы вместо резистора 680 включается резистор 470 . Коэффициент усиления вычисляется

по формуле = ( − 0)·470000 . Напряжение UC0 является напряжением на коллекторном

·(680+19)

резисторе без базового тока. Как предполагается, правильным является более высокий коэффициент усиления, определенный первым или вторым способом. В версии 1.08k коэффициент усиления в схеме с общим эмиттером определяется только для микроконтроллеров ATmega328. Для других микроконтроллеров используется только схема с общим коллектором.

Значения, найденные для P-N-P транзистора, действительны только, если сделаны дополнительные измерения. Чтобы предотвратить обнаружение P-N-P транзистора в инверсном включении (коллектор с эмиттером поменяны местами), измерение с более высоким коэффициентом усиления считается правильным. Если напряжение базы ниже, чем 0, 97 , то это должен быть P-E-MOS. В этом случае пороговое напряжение затвора измеряется при плавном переключении затвора с резистором 470 от VCC до GND, ожидая на цифровом входе изменения сигнала стока, и затем, считывается напряжение затвора.

64

VCC

VCC

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

|

22 |

|

|

19 |

|

|

22 |

|

|

19 |

|

|

|

22 |

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

22 |

|

|

19 |

|

|

22 |

|

|

19 |

|

|

22 |

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADCMUX |

|

|

PC0 |

PB0 |

PB1 |

|

|

680 |

R1 |

470k |

R2 |

TP1 |

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

|

19 |

22 |

19 |

22 |

19 |

22 |

GND |

|

|

|

|

|

|

|

|

|

ADCMUX |

|

|

|

|

|

PC1 |

PB2 |

|

PB3 |

|

|

|

|

680 |

R3 |

470k |

R4 |

TP2 |

|

ADCMUX |

|

|

|

|

PC2 |

PB4 |

|

PB5 |

TP3 |

680 |

R5 |

470k |

R6 |

|

|

|

|

The black state of switches is used for test!

The green state is used for current amplification factor hFE.

Рис. 5.5. Испытание и измерение hFE P-N-P транзистора в схеме с общим эмиттером

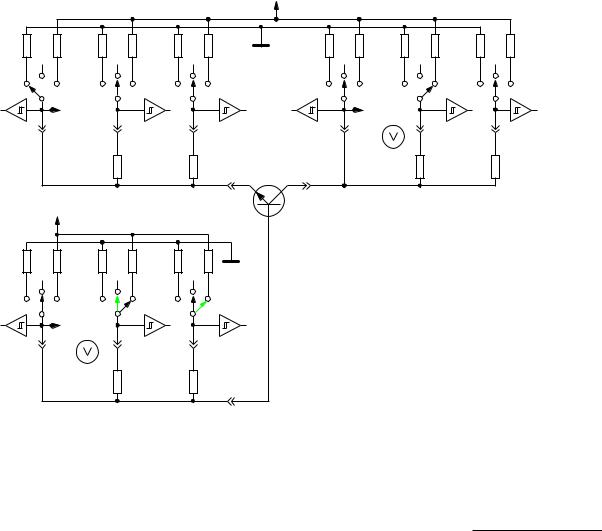

5.1.2Измерение N-P-N транзистора или N-Channel-MOSFET

Измерение N-P-N транзистора начинается таким же образом, как и P-N-P транзистора, с измерения коэффициента усиления в схеме с общим коллектором. Первое измерение сделано с резистором в цепи базы 680 подключенным к VCC. Если напряжение на резисторе в цепи базы слишком низко, вместо 680 берётся резистор 470 . Тогда измерение продолжается

всхеме с общим эмиттером, как показано на рисунке 5.6. Если напряжение коллектора ниже 1, 6 и резистор в цепи базы 680 соединён с VCC, то это может быть N-P-N транзистор, N-канальный MOSFET или тиристор/симистор. Тиристор или симистор могут быть идентифицированы двумя простыми тестами. Если резистор на управляющем выводе, соединённый

втечение 10 с GND обесточить, ток в аноде должен остаться. Если резистор анода кратковременно подключить к GND и, затем, повторно подключить к VCC, тиристор не должен снова включиться (нет тока). Имейте в виду, что Тестер может проверять только маломощные тиристоры, потому что ток удержания может достигать только 6 . Если оба теста свидетельствуют о тиристоре, то необходимо сделать тесты с обратной полярностью, чтобы исключить или подтвердить симистор.

65

|

|

|

|

|

|

|

VCC |

19 |

22 |

19 |

22 |

19 |

22 |

|

19 |

|

|

|

|

|

|

|

GND |

|

|

|

|

|

|

|

22 |

|

|

ADCMUX |

|

|

|

|

|

|

PC0 |

PB0 |

|

PB1 |

|

|

|

|

|

680 |

R1 |

470k |

R2 |

TP1 |

TP3 |

|

|

|

|

|

|

||

19 |

22 |

19 |

22 |

ADCMUX |

|

|

|

PC2 |

PB4 |

|

PB5 |

680 |

R5 |

470k |

R6 |

|

|

VCC |

|

|

|

19 |

22 |

19 |

22 |

19 |

22 |

|

|

ADCMUX |

|

|

|

|

PC1 |

PB2 |

|

PB3 |

|

|

|

680 |

R3 |

470k |

R4 |

GND

The black state of switches is used for test!

The green state is used for current amplification factor hFE.

TP2

Рис. 5.6. Испытание и измерение hFE N-P-N транзистора в схеме с общим эмиттером

Если ни тиристор, ни симистор не были подтверждены, то это может быть N-P-N транзистор или N канальный E-MOSFET. Базовое напряжение N-P-N транзистора будет близко к напряжению эмиттера, таким образом, этот тип может быть идентифицирован определенно. Коэффици-

ент усиления в схеме с общим эмиттером вычисляется по формуле = ( − − 0)·470000 .

( − )·(680+22)

Если напряжение базы или затвора повышенные, то в этой цепи тока нет или он мал, значит, элемент будет N-канальным E-MOS (MOSFET обогащённый). В этом случае пороговое напряжение измеряется при плавном переключении затвора с резистором 470 от VCC до GND, ожидая на цифровом входе изменения сигнала стока, и затем считывается напряжение затвора. Это измерение делается 11 раз с накоплением результатов АЦП, как показано на рисунке 5.7. Результат умножается на 4 и делится на 9, чтобы получить напряжение в .

66

Рис. 5.7. Измерение порогового напряжения N-канального MOSFET

67

5.1.3Упрощенная блок-схема тестирования транзисторов

CheckPins |

|

|

|

|

|

|

|

Start |

H |

|

|

H |

|

|

H |

680 |

T |

|

T |

|

|

680 |

T |

|

L |

|

|

L |

|

|

L |

|

|

680 |

|

680 |

|

|

680 |

|

vCEs |

|

lp_otr |

|

|

lp2 |

|

lp_otr |

|

|

vCEs |

|

|

|

|

|

680 |

|

|

|

680 |

Y |

|

H |

|

|

|

H |

|

|

|

|

|

|

|

lp2 < vCEs ? |

|||

T |

|

|

680 |

T |

|

||

L |

|

|

|

L |

|

|

|

|

|

|

|

|

|

|

N |

update_pins = 1 |

|

|

|

|

|

|

|

n.cnt+p.cnt>1? |

|

|

|

|

|

|

|

(n.cnt!=1)||(n.b==p.b)? |

checkDiode |

|

|

|

|

|

|

Y |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P−channel |

Y |

|

|

|

|

|

|

hp1 |

vCEs*2+20 > lp_otr ? |

|

|

N−channel |

|

|

|

|

|

|

|

|

|

680 |

||

vCEs > 115 ? |

|

|

|

|

tp1 |

H |

|

|

|

|

|

|

|||

|

|

|

|

|

470k |

T |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

L |

N |

tp1 |

H |

|

|

|

|

|

470k |

T |

|

|

|

|

||

|

|

|

|

|

|

||

|

|

|

L |

|

|

|

|

|

|

|

680 |

|

|

|

hp2 |

|

|

|

lp1 |

|

|

|

|

|

|

|

|

|

|

|

680 |

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

470k |

T |

|

|

|

|

|

|

|

L |

|

|

|

H |

|

|

|

|

|

470k |

T |

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

680 |

|

|

|

|

|

|

|

lp2 |

|

|

|

|

|

|

|

|

|

|

hp1 > (hp2+599) ? |

|

|

|

|

|

|

|

|

N |

|

lp2 > (lp1+599) ? |

|

|

|

|

||

|

|

|

N |

|

|

|

|

|

|

|

|

|

|

Y |

|

|

Y |

|

|

|

|

tp2 |

H |

|

|

|

|

|

|

470k |

T |

|

|

|

680 |

|

|

|

L |

|

lp2 |

|

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

470k |

T |

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

|

|

|

tp2 < 977 ? |

|

|

|

|

|

|

|

Y |

N |

|

|

|

|

|

|

|

|

|

lp2 > 3911 ? |

|

|

|

|

||

|

Y |

|

N |

|

|

|

|

Part = FET |

Part = FET |

Typ = P−D−MOS |

Typ = P−JFET |

Part = FET |

Part = FET |

Typ = N−D−MOS |

Typ = N−JFET |

p.cnt = p.cnt+1 |

n.cnt = n.cnt+1 |

p.gthvoltage = tp1−hp1 |

n.uBE = lp1 |

p.current = (VCC−hp1)/680 |

n.gthvoltage = lp1−tp1 |

|

n.current = lp1/680 |

|

Part 2 |

savePresult |

saveNresult |

|

saveNresult

n.cnt = n.cnt+1

update_pins |

Y |

|

|

= 1 ? |

|

|

|

|

|

|

|

n.b = TristatePin |

|

n.e = LowPin |

|

n.c = HighPin |

|

savePresult |

|

p.cnt = p.cnt+1 |

|

update_pins |

Y |

|

|

= 1 ? |

|

p.b = TristatePin |

|

|

p.e = HighPin |

|

p.c = LowPin |

H

T

L

CheckPins

Exit

Рис. 5.8. Блок-схема тестирования транзисторов. Часть 1: JFET и D-MOS

68

|

|

|

|

hp1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tp1 |

680 |

|

|

|

|

tp1 |

|

|

|

|

|

|

Part2 |

|

|

H |

|

|

|

|

|

H |

|

|

|

|

||

|

|

680 |

|

T |

|

|

|

680 |

|

T |

|

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

680 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

lp1 |

|

|

|

|

|

|

|

|

|

P−Channel |

|

|

|

|

|

N−Channel |

|

|||

|

|

tp1 < 10 ? |

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

|

|

|

|

||

|

|

|

|

|

|

|

(VCC−tp1) < 10 ? |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

hp1 |

680 |

|

|

|

|

|

|

|

|

|

|

|

N |

|

tp1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

|

tp1 |

|

|

||

|

|

|

|

470k |

T |

|

|

N |

|

|

|

|

H |

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

470k |

T |

|

|

|

|

|

|

|

|

tpx = VCC − tp1 |

|

|

|

|

L |

|

|||

|

|

|

|

|

|

|

|

|

|

680 |

|

||||

|

|

|

|

|

|

c_hfe = (lp1 − tpx) / tpx |

|

|

|

lp1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

c_hfe=(VCC−hp1−tp1)/tp1 |

|

c_hfe=(VCC−hp1)*470k/680/tp1 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

c_hfe=lp1*470k/680/(VCC−tp1) |

|

||

|

|

|

|

|

|

|

|

hp1 |

680 |

|

|

|

|

|

|

|

|

|

|

|

|

|

tp2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

680 |

|

T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

lp2 |

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

680 |

|

|

|

|

|

|

|

|

|

checkDiode |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

hp1 < 1600 ? |

|

|

checkDiode |

lp_otr < 1977 ? |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

N |

|

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

|

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

680 |

T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

ThyristorCheck |

|

|

|

|

|

|

|

|

680 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

lp1 |

|

|

|

|

|

|

|

|

|

|

|

Y |

lp1 > 3422 ? |

|

|

Ntype |

|

|

|

|

|

|

|

||

|

|

|

N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

hp2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tp2 |

H |

|

|

|

|

|

hp2 |

|

|

|

|

|

|

|

470k |

T |

|

|

|

|

|

|

680 |

|

|

|

|

|

|

|

|

|

L |

|

|

|

|

tp2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

|

||

|

|

680 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

470k |

T |

|

|

|

|

|

|

|

|

|

|

|

lp1 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

lpx |

|

|

|

|

rtp = VCC − tp2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rhp = VCC − hp2 |

|

||

|

|

|

|

Part = TRANS |

|

|

|

|

|

|

|

|

|

|

|

tp2 > 2000 ? |

|

Typ = PNP |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

N |

|

Y |

e_hfe = (lp1−lp_otr)*470k/680/tp2 |

|

|

|

|

|

Y |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

update_pins = 0 |

|

|

|

|

|

|

|

rtp > 2557 ? |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Part = TRANS |

|

|

|

N |

|

|

|||

|

|

|

|

|

|

|

Typ = NPN |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

p.hfe = e_hfe |

|

p.cnt > 0 or |

e_hfe = (rhp−lp_otr)*470k/680/rtp |

|

|

|

|

||||||||

p.uBE = hp2 − tp2 |

|

|

update_pins = 0 |

|

|

|

|

|

|

||||||

|

e_hfe > p.hfe ? |

|

|

|

|

|

|

|

|||||||

update_pins = 1 |

Y |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

lp_otr < 97 ? |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rhp > 3400 ? |

N |

|

|

|

|

N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n.cnt = 0 ? or |

Y |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Y |

|

|||

|

|

|

|

|

|

e_hfe > n.hfe ? |

|

|

|

|

|

|

|||

|

|

|

|

p.hfe = c_hfe |

|

|

|

|

|

|

|

|

|||

c_hfe > p.hfe ? |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

p.uBE = hp1 − tp1 |

|

|

|

|

|

|

|

|

Part = FET |

|

|||

|

|

|

|

|

|

|

n.hfe = e_hfe |

|

|

|

|||||

|

|

Y |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

Typ = N_E_MOS |

|

|||||

|

|

|

update_pins = 1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

N |

|

|

|

n.uBE = tp2 − lpx |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

N |

|

|

|

|

|

|

|

|

update_pins = 1 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

|

|

|

|

|

|

hp2 >lp2+250 ? |

|

||

|

|

|

|

update_pins = 1 ? |

|

|

|

|

|

|

|

|

|

|

|

lp_otr < 97 ? |

|

|

|

|

|

Y |

|

Typ = N_E_IGBT |

|

|

|

p.ice0 = lp_otr/680 |

c_hfe > n.hfe ? |

|

|

|

|

||

lp1 > 2000 ? |

N |

|

|

|

|

|

|||

|

p.ices = vCEs / 680 |

|

|

|

|

|

|||

|

N |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n.hfe = e_hfe |

|

|

680 |

Y |

|

|

savePresult |

|

|

|

|

H |

|

|

|

|

N |

n.uBE = tp2 − lpx |

|

|

|||

|

|

|

|

|

470k |

|

T |

||

Part = FET |

|

|

|

|

|

update_pins = 1 |

|

|

L |

|

|

|

|

|

|

|

|

||

Typ = P_E_MOS |

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

|

|

680 |

T |

|

|

|

|

DInp |

|

|

|

|

L |

|

|

|

tpx |

680 |

|

|

|

|

680 |

|

|

|

H |

|

|

|

|

|

|

|

|

|

||

|

N |

|

|

|

|

Y |

470k |

|

T |

|

|

|

|

|

|

|

L |

||

hp2 > lp1+250 ? |

|

|

|

|

update_pins = 1 ? |

|

|

||

|

|

|

|

|

|

|

|

||

|

|

|

tpx |

H |

|

|

|

|

|

|

|

|

470k |

T |

|

p.ice0 = lp_otr / 680 |

|

|

|

Y |

|

|

|

L |

|

|

|

|

|

Typ = P_E_IGBT |

|

680 |

N |

p.ices = (VCC−vCEs) / 680 |

n.gthvoltage = tpx |

||||

|

|

|

|

DInp |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

savePresult |

gthvoltage = VCC − tpx |

saveNresult |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 5.9. Блок-схема тестирования транзисторов. Часть 2: BJT и E-MOS

69