- •Достижения в микроэлектроники – От Микроразмерных к Наноразмерным Устройствам

- •9.1. Введение

- •9.2. Краткая история микроэлектронных устройств и технологий

- •9.3.2. Носители заряда в полупроводниках

- •9.3.3. Собственные и примесные полупроводники

- •9.5. Масштабирование размеров транзисторов

- •9.6. Малоразмерные эффекты

- •9.6.1. Масштабирование подзатворного тока

- •9.6.2. Горячие электроны

- •9.6.3 Короткоканальные эффекты и индуцированное стоком понижение барьера.

- •9.6.4. Эффекты узкой ширины

- •9.6.5 Насыщение скорости

- •9.6.6. Сопротивление сток-исток

- •9.6.7. Примесные флуктуации

- •9.7. Наноразмерные mosfet транзисторы: удлинение классических cmos-тразисторов

- •9.7.1. Кремний на изоляторе (soi)

- •9.7.3. High-k диэлектрик затвора

- •9.7.4. Металлический электрод затвора

- •9.7.5 Охлаждённый cmos

- •9.7.6. Двухзатворный mosfet

- •9.8. За рамками традиционных cmos

- •9.9. Резюме

9.9. Резюме

-

Микроэлектроника является одним из самых сложных производственных методов, разработанных человечеством.

-

CMOS является доминирующей технологией.

-

Количество транзисторов и функциональность чипа возрастает вдвое каждые 18 месяцев в течение последних 40 лет (закон Мура).

-

Масштабирование размеров устройства позволяет микроэлектронной промышленности продолжать развитие в темпе, заданном законом Мура.

-

Характерные размеры уменьшаются на 30% каждые 2-3 года.

-

Обобщённые законы масштабирования наиболее популярны в производстве.

-

Улучшение производительности: скорость увеличивается на 30% в год.

-

Уменьшение стоимости функции: 25-32% в год.

-

Устройства переходят на наноуровень. Масштабирование, как ожидается, продлится до достижения физической длины затвора около 8-10 нм.

-

Ограничения масштабирования:

-

Подпороговый ток (ток отключения) не масштабируется.

-

В малоразмерных транзисторах горячие электроны и туннелирование могут стать излишними.

-

Флуктуации концентрации примесей вызывают большие изменения порогового напряжения.

-

Плотность мощности в результате увеличения тока утечки растёт быстрее, чем активная мощность и является одним из главных ограничений масштабирования.

-

Улучшенные конструкции устройств и материалы необходимы для продолжения масштабирования в следующе десятилетии. Перспективными подходами являются:

-

Кремний на изоляторе

-

Растянутый кремний

-

Двухзатворный FET

-

High-k материалы затвора вместо традиционного

-

Металлический затвор заменит традиционный поликремниевый затвор.

-

Подходы следующие после обычных CMOS-транзисторов

-

CMOS будет формировать основу и интегрироваться с нетрадиционными устройствами

-

Кремниевая технология ляжет в основу новых наноразмерных структур

-

Будут появляться мощные системы на чипе (SoC) состоящие из различных технологий, таких как наноразмерная микроэлектроника, микрогидродинамика, биосенсоры, новые нано-устройства и системы комплексной обработки информации.

ВОПРОСЫ

-

Рассмотрим пластину кремния p-типа с удельным сопротивлением 25 Ωсм. Предположим, что подвижность электронов и дырок в объёмном кремнии при 400 см2/В∙с и 1,300 см2/В∙с, соответственно.

-

Какова концентрация NA атомов легирующей примеси объёмном кремнии?

-

Какова концентрация неосновных зарядов в объёме?

-

Рассчитать напряжение Ферми

объёмного

кремния при комнатной температуре.

объёмного

кремния при комнатной температуре. -

При какой температуре собственная концентрация носителей

будет равна уровню легирования?

будет равна уровню легирования?

-

Рассмотрим MOS-конденсатор, подзатворный диэлектрик которого состоит из

толщиной 0.8 и 0.5 нм, соответственно.

Уровень легирования подложки

толщиной 0.8 и 0.5 нм, соответственно.

Уровень легирования подложки  .

Затвор является слоем

.

Затвор является слоем  -поликремния.

Эффективный заряд оксида

-поликремния.

Эффективный заряд оксида  .

.

-

Рассчитать эквивалентную толщину оксида EOT и диэлектрическую ёмкость

на единицу площади.

на единицу площади. -

Какова максимальная толщина обеднённого слоя, при которой инвертируется поверхность?

-

Рассчитать напряжение плоских зон, предполагая, что не ионная имплантация выполнялась для регулировки порогового напряжения.

-

Рассчитать величину порогового напряжения

.

. -

Предположим, что необходимо получить пороговое напряжение 0,65 В. Какая доза легирования необходима для регуляции порогового напряжения? Что вы будете имплантировать: доноры или акцепторы?

-

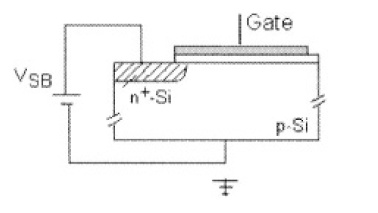

Рассмотрим следующий модифицированный MOS-конденсатор (запертый диод). Конденсатор имеет те же самые параметры, что и в вопросе 2. Объяснить качественно, как будут задействованы следующие параметры:

.

.

-

NMOS-транзистор изготовлен на кремниевой подложке с уровнем легирования

.

Толщина оксида составляет 6 нм и пороговое

напряжение при комнатной температуре

равно 0.45 В.

.

Толщина оксида составляет 6 нм и пороговое

напряжение при комнатной температуре

равно 0.45 В.

-

Рассчитайте коэффициент m эффекта тела и подпороговые наклоны NMOS и PMOS транзисторов при 300 К, 375 К и 77 К. Предположить, что вклад интерфейсных состояний в коэффициент эффекта тела составляет 0.15.

-

Рассчитайте ток утечки в NMOS при 300 К, 375 К и 77К, когда

,

для транзистора с

,

для транзистора с  .

Предположим что подвижность электронов

при соответствующих температурах равна

500, 300, 1800

.

Предположим что подвижность электронов

при соответствующих температурах равна

500, 300, 1800  ,

соответственно. Температурный коэффициент

порогового напряжения равен

,

соответственно. Температурный коэффициент

порогового напряжения равен  .

. -

Кроме того рассчитайте ток насыщения для

при этих трёх температурах.

при этих трёх температурах. -

Насколько можно уменьшить пороговое напряжение для того, чтобы сохранять величину тока утечки при 77 К равной току утечки при 300 К? Дайте значение порогового напряжения при 77 К и 300 К.

-

Насколько можно уменьшить питание

для того, чтобы при 77 К поддерживать

значение тока насыщения таким же, как

при комнатной температуре? Предположить,

что

для того, чтобы при 77 К поддерживать

значение тока насыщения таким же, как

при комнатной температуре? Предположить,

что  при комнатной температуре равен 2 В.

при комнатной температуре равен 2 В.

-

Предположить, что толщина оксида

,

и толщина инверсного слоя в поликремниевом

затворе

,

и толщина инверсного слоя в поликремниевом

затворе

-

Какова общая ёмкость инверсного слоя оксида и поликремния?

-

Предположим, что вам нужно сохранять вклад барьерной ёмкости поликремния в эффективную ёмкость оксида меньше 10% от ёмкости оксида. Какова максимально возможная толщина истощения

поликристаллического слоя?

поликристаллического слоя?

-

Используя правило масштабирования с постоянным полем, докажите, что масштабирование тока транзистора I, задержки и рассеиваемая мощность ведёт себя так, как указано в Таблице 9.1.

-

Используя правило масштабирования с постоянным напряжением, докажите, что масштабирование тока транзистора I, задержки и рассеиваемая мощность ведёт себя так, как указано в Таблице 9.1.

-

Используя правило масштабирования с постоянным полем, найдите правило масштабирования подпорогового тока утечки.

-

Правила масштабирования, изложенные в Таблице 9.1. предполагают, что транзистор не страдает от насыщения скорости. Какими должны быть правила масштабирования тока, задержки и рассеяния скорости в случае насыщения скорости и обобщённого масштабирования?

-

Время переноса

в транзисторе определяется как отношение

в транзисторе определяется как отношение

,

в котором

,

в котором  это заряд в инверсной области.

это заряд в инверсной области.

-

Найти выражение для времени переноса при условии, что транзистор работает в линейной области. Каким образом масштабируется время переноса в случае масштабирования с постоянным напряжением?

-

Найти выражение для времени переноса при условии, что транзистор работает в области насыщение. Можно считать транзистор длинноканальным. Выражение для заряда

в канале составляет две третьих заряда

транзистора в линейной области

в канале составляет две третьих заряда

транзистора в линейной области

-

Рассмотрим следующий подзатворный диэлектрик:

-

Диэлектрический слой имеет величину K равную 16. Какая толщина слоя необходима для получения EOT толщиной 1 нм? Предположить, что величина К для

составляет 16.

составляет 16.

ПРИЛОЖЕНИЕ А. Используемые константы и свойства материалов:

Заряд

электрона, ![]()

Диэлектрическая

проницаемость, ![]() (вакуума)

(вакуума) ![]()

![]()

![]()

![]()

Постоянная

Больцмана: ![]()

Постоянная

Планка: ![]()

![]() при

комнатной температуре:

при

комнатной температуре: ![]()

![]() при комнатной температуре:

при комнатной температуре: ![]()

Собственная концентрация носителей в Si при комнатной температуре

![]()

Подвижность носителей в объёмном кремнии при комнатной температуре:

![]()

![]()

Плотность

атомов Si:

![]()

Ширина запрещённой зоны при комнатной температуре:

Si:

![]()

Ge:

![]()

GaAs:

![]()

SiO2:

![]()

Поле

пробоя в Si,

![]()

Электрическая

плотность SiO2,

![]()

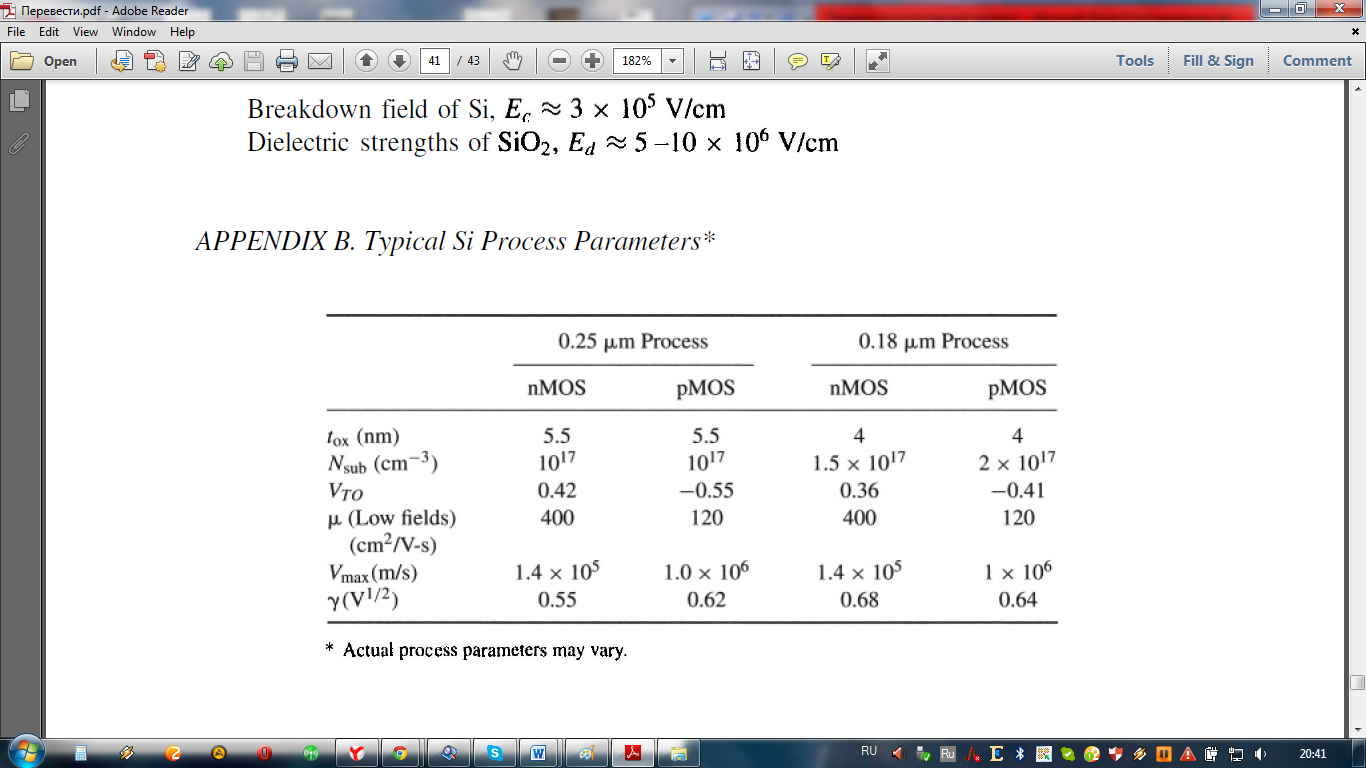

ПРИЛОЖЕНИЕ В. Характерные параметры Si-процесса *

* реальные параметры процесса могут отличаться

СПИСОК ЛИТЕРАТУРЫ

-

P. Gargini‚ The global route to future semiconductor technology‚ IEEE Circuits and Devices Magazine‚ 13 (March 2002).

-

International Technology Roadmap for Semiconductors (ITRS)‚ Semiconductor Industry Association (ISA)‚ 2003 Update (San Jose‚ 2003); http://public.itrs.net/.

-

F. Boeuf‚ T. Skotnicki‚ S. Monfray‚ C. Julien et al.‚ Technical Digest‚ IEEE International Electron Devices Meeting‚ 637(2001).

-

B. Yu‚ H. Wang‚ A. Joshi‚ Q. Xiang et al.‚ Technical Digest‚ IEEE International Electron Devices Meeting‚ 937(2001).

-

R. Goodall‚ D. Fandel‚ A. Allan‚ P. Landler‚ and H. R. Huff‚ Proceedings Electrochemical Society 2‚ 125 (2002).

-

D. Kahng and M. M. Atalla‚ Silicon-silicon dioxide field induced surface devices‚ IRE-AIEE Solid-State Device Research Conference (Pittsburgh‚ 1960).

-

G. Moore‚ Electronics Magazine 39‚ 114 (1965).

-

R. Schaller‚ IEEE Spectrum‚ 53 (June 1997).

-

M. Pinto‚ Proceedings IEEE International Conference‚ Solid State Circuits‚ 26 (2000).

-

R. Turton‚ The Quantum Dot‚ A Journey into the Future of Microelectronics‚ (Oxford University Press‚ New York‚ 1995).

-

J. Plummer‚ M. D. Deal‚ and P. B. Griffin‚ Silicon VLSI Technology‚ (Prentice Hall‚ Upper Saddle River‚ NJ‚ 2000).

-

R. Pierret‚ Semiconductor Fundamentals: Volume I‚ 2/E‚ (Prentice Hall‚ Upper Saddle River‚ 1988).

-

B. G. Streetman and S. Banerjee‚ Solid State Electronic Devices‚ ed.‚ (Prentice Hall‚ Upper Saddle River‚ 2000).

-

R. W. Keyes‚ IEEE T. Electron Dev. 33‚ 863 (1986).

-

K. Rim et al.‚ Symposium‚ VLSI Technology‚ 98 (2002).

-

Y. Taur and T. Ning‚ Fundamentals of Modern VLSI Devices‚ (Cambridge University Press‚ New York‚ 1998).

-

D. Buss‚ Digest of the 2002 IEEE International Solid-State Circuit Conference‚ 3 (2002).

-

E. J. Novak‚ IBM J. Res. Dev. 46‚ 169 (2002).

-

P. Gelsinger‚ Digest of the 2001 IEEE International Solid-State Circuit Conference‚ 3 (2001).

-

D. Frank‚ R. Dennard‚ E. Nowak‚ P. Solomon‚ Y. Taur‚ and H. S. Wong‚ P. IEEE 89‚ 259 (2001).

-

S. Krishnan and J. G. Fossum‚ IEEE Circuits Device‚ 32 (July 1998).

-

M. Palella and J. Fossum‚ IEEE T. Electron Dev. 49‚ 96 (2002).

-

H. S. Wong et al.‚ IEEE IEDM Technical Digest‚ 407 (1998).

-

M. Jurczak et al.‚ IEEE T. Electron Dev. 47‚ 2179 (2000).

-

L. Geppert‚ IEEE Spectrum‚ 28 (October 2002).

-

R. M. Wallace and G. Wilk‚ MRS Bulletin‚ 192 (March 2002).

-

P. H. Wong‚ IBM J. Res. Dev. 46‚ 133 (2002).

-

J. M. Hergenrother et al.‚ IEDM‚ 3.11 (December 2001).

-

Y. Taur‚ IBM J. Res. Dev. 46‚ 213 (2002).

-

F. G. Pikus and K. K. Likharev‚ Appl. Phys. Lett. 71‚ 3661 (1997).

-

C. Svensson‚ Technical Digest IEEE International Solid-State Circuits Conference‚ S28 (February 2003).

-

E. J. Nowak‚ IBM J. Res. Dev. 46‚ 169 (2002).

-

P. H. Wong et al‚ P. IEEE‚ 87‚ 537 (1999).

-

X. Huang et al‚ Technical Digest IEDM‚ 67 (1999).

-

D. Hisamoto et al‚ IEEE T. Electron Dev. 47‚2320 (2000).

-

Y. K. Choi et al.‚ Technical Digest IEDM‚ 421 (2001).

-

J. Huchby‚ G. Bourianoff‚ V. Zhirnov‚ and J. Brewer‚ Extending the Road beyond CMOS‚ IEEE Circuits & Device Magazine‚ 28 (March 2002).

-

R. Compano‚ Ed.‚ Technology Roadmap for Nanoelectronics‚ 2nd ed.‚ European Commission Information Society Programme‚ (2000). (ftp://ftp.cordis.lu/pub/ist/docs/fetnidrm.zip).

-

A. Steane and E. Rieffel‚ IEEE Computer‚ 38 (January 2000).

-

D. DiVincenzo‚ Technical Digest IEDM‚ 12 (2000).

-

S. Forrest et al‚ IEEE Spectrum‚ 29 (August 2000).