- •Достижения в микроэлектроники – От Микроразмерных к Наноразмерным Устройствам

- •9.1. Введение

- •9.2. Краткая история микроэлектронных устройств и технологий

- •9.3.2. Носители заряда в полупроводниках

- •9.3.3. Собственные и примесные полупроводники

- •9.5. Масштабирование размеров транзисторов

- •9.6. Малоразмерные эффекты

- •9.6.1. Масштабирование подзатворного тока

- •9.6.2. Горячие электроны

- •9.6.3 Короткоканальные эффекты и индуцированное стоком понижение барьера.

- •9.6.4. Эффекты узкой ширины

- •9.6.5 Насыщение скорости

- •9.6.6. Сопротивление сток-исток

- •9.6.7. Примесные флуктуации

- •9.7. Наноразмерные mosfet транзисторы: удлинение классических cmos-тразисторов

- •9.7.1. Кремний на изоляторе (soi)

- •9.7.3. High-k диэлектрик затвора

- •9.7.4. Металлический электрод затвора

- •9.7.5 Охлаждённый cmos

- •9.7.6. Двухзатворный mosfet

- •9.8. За рамками традиционных cmos

- •9.9. Резюме

9.7.5 Охлаждённый cmos

Масштабирование является главным движущим фактором производительности устройств. Однако, отсутствие масштабирования общего напряжения и увеличение туннелирования через подзатворный оксид будет ограничивать масштабирование обычных объёмных CMOS транзисторов длиной затвора около 20 нм.29 Один из способов расширить диапазон устройств за пределы длины затвора 20 нм, заключается в их охлаждении. При низких температурах рассеяние носителей уменьшается, приводя к более высокой подвижности. Кроме того, подпороговый наклон S пропорционален кТ/Q. Понижение температуры даст более крутой наклон, который значительно уменьшает ток отключения. Это позволяет работать с более низким пороговым напряжением и питанием. В результате, может стать возможным расширить масштабирование CMOS до режима 10 нм.

9.7.6. Двухзатворный mosfet

Масштабирование устройства продолжает создавать всё более строгие ограничения на конструкцию устройства, что делает оптимизацию всё труднее и труднее. Как обсуждалось выше, одним из ограничений масштабирования устройства является понижение сток-индуцированного барьера, что приводит к снижению порогового напряжения и увеличению токов утечки. Путём экранирования электрического поля стока от истока через затвор, эффект понижения барьера, индуцированного стоком может быть значительно снижен. Это может быть получено с меньшим инверсным слоем подложки, и, таким образом, более высокими уровнями легирования подложки. С другой стороны, малый инверсный слой подложки уменьшает связь напряжения на затворе с потенциалом канала и, следовательно, даёт меньший управляющий ток, больший коэфициент тела m и худшие подпороговые наклоны. Эти противоречивые требования к легированию подложки, как результат необходимости сокращения короткоканальных эффектов и получения хороших управляющих токов, накладывают серьёзные ограничения на эффективность дальнейшего масштабирования обычных CMOS-транзисторов.

Двухзатворный полевой транзистор (DG FET) по существу разделяет эти два требования к легированию подложки.30,20 Было спрогнозировано, что DG FET может быть уменьшен до размера, на 50 % меньшего минимального размера объёмного FET, позволяя устройствам с затвором длиной около 8-10 нм работать при комнатной температуре.31 Эти прогнозы и недавние успехи в изготовлении таких устройств делают DG FET серьёзным претендентом на то, чтобы стать доминирующей структурой устройств в последнюю эпоху CMOS-масштабирования, до того как будет достигнут атомный уровень.32

![]()

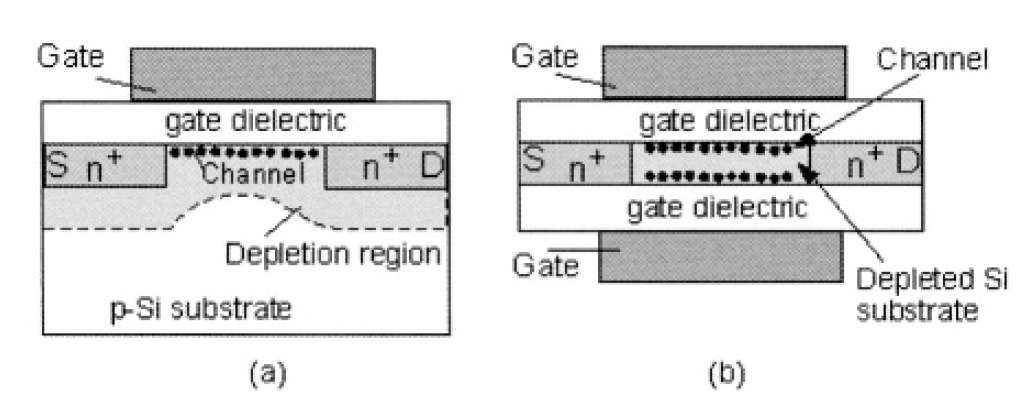

Схематичное поперечное сечение DG FET показано на Рис. 9.25. вместе с объёмным MOSFET. DG FET это непланарный транзистор с верхним и нижним затвором с двух сторон тонкого кремниевого канала. Это позволяет контролировать потенциал канала намного более жестко, чем в случае стандартного планарного транзистора, в котором большую роль играет эффект подложки. Короткоканальные эффекты теперь в основном зависят от геометрии устройства а не от легирования подложки. В результате, подложка может быть слаболегирована или даже нелегирована. Незначительная ёмкость обеднения подложки рассматривает эффективную связь напряжения на затворе с потенциалом канала, что даёт крутой подпороговый наклон около 60 мВ/декаду и хороший управляющий ток. Это является важным преимуществом DG FET, так как оно рассматривает перегрузку напряжения затвора и делает DG FET особенно привликательным для маломощных применений.

Также, низкое легирование канала выгодно для подвижности носителей. Однако, было обнаружено, что при толщине кремниевого канала меньше 20 нм подвижность носителей снижается когда плотность инверсного заряда становится низкой. Для больших плотностей инверсного заряда (около 1013/см2), что обычно бывает в случае наноразмерных CMOS, деградация гораздо менее выражена. Кроме того, в нелегированных подложках перенос носителей значительно лучше, чем в обычных устройствах. Это, главным образом, благодаря снижению рассеяния в электрическом поле канала и нижнего затвора. Оба эти эффекта увеличивают подвижность в DG FET с коэффициентом около двух по сравнению с коэффициентом в стандартном объёмном FET.27

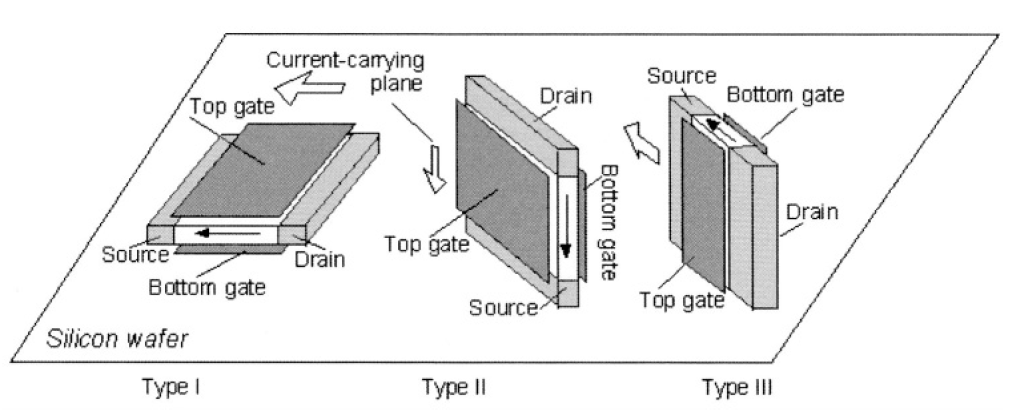

Как можно видеть из Рис. 9.26, DG FET могут быть изготовлены с любой из трёх указанных топологий.33 Структура I типа больше всего напоминает обычный плоский объёмный FET. Она удобна для равномерного контроля толщины канала, но создаёт трудности в изготовлении нижнего затвора и высококачественного подзатворного диэлектрика. Кроме того, изготовление контакта нижнего затвора затруднительно и требует специального оборудования которое уменьшает общую плотность устройства.

Каналы в DG FET II и III типа перпендикулярны подложке. Доступ к верхнему и нижнему затворам легче, чем в планарной структуре. С другой стороны, толщина подложки определяется техникой литографии, что придаёт решающее значение контролю равномерности. Для правильной работы, толщина подложки (канала) должна быть значительно меньше (3-4 x) чем длина затвора, что ещё больше усложняет контроль размеров подложки для устройств с затвором небольшой длины.

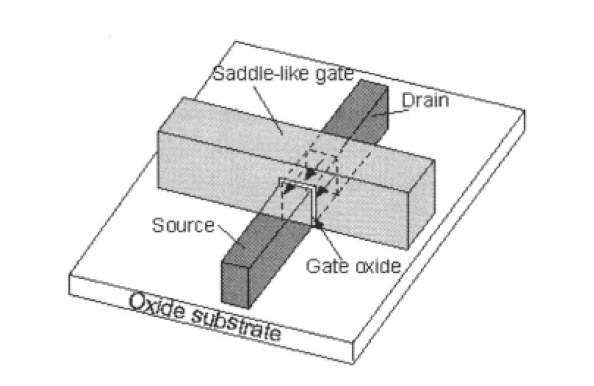

III тип структуры является на сегодняшний день самой успешной и её часто называют FinFET.34, 35, 36 Вид FinFET схематично показан на Рис. 9.27. Канал помещается поверх подложки кремний-на-изоляторе (SOI) в виде плавника. Толщина плавника соответствует толщине кремниевого канала, котрый должен тщательно контролироваться, с использованием передовых методов паттерна и травления.

Диэлектрик затвора выращивается или осаждается поверх плавника до поликремниевого зтвора, осаждаемого поверх него, с образованием седловидной структуры. Области истока и стока примыкают к плавнику. Расстояние между областями истока и стока определяет длину затвора, а высота плавника - его ширину. Для того, чтобы воспользоваться приемуществами двухзатворной структуры, надо убедиться, что паразитическое перекрытие ёмкостей между областями затвора и истока/стока сведено к минимуму. Инновации в технологии будут необходимы для уменьшения этих и других паразитных эффектов и полноценного использования уменьшенных короткоканальных эффектов и увеличенных управляющих токов в этих нанразмерных устройствах.

Конструкции и материалы, описанные в этом разделе будут необходимы для продления технологии CMOS до конца срока действия ITRS. Не смотря на то, что нет технологичных решений, известных для некоторых материалов и конструкций, которые были обсуждены, можно полагать, что эти материальные и производственные проблемы будут решены для того, чтобы сохранять актуальность прогнозов ITRS. Возникает вопрос, что произойдёт, когда дорожная карта прекратит своё действие? Будет ли CMOS заменён более продвинутыми технологиями или будет сосуществовать с другими, нестандартными тахнологиями? Следующий раздел даёт некоторое представление о том, что лежит за пределами традиционных CMOS-устройств.

![]()