- •Аналоговые и цифровые устройства автоматики

- •Глава 1. Архитектура и устройство

- •1.1. Внутренняя организация мк

- •1.2. Назначение выводов микросхемы мк

- •1.3. Организация памяти в мк

- •1.4. Регистр состояния программы psw

- •1.5. Таймеры/счетчики, регистры tmod и tcon

- •1. 6. Режимы работы таймеров/счетчиков

- •Структура прерываний мк

- •1.8. Блок последовательного интерфейса мк

- •1.8.1. Последовательная передача информации

- •1.8.2. Последовательный порт однокристального мк

- •1.8.3. Регистр управления последовательным портом scon

- •1.8.4. Режимы работы последовательного порта

- •1.8.5. Асинхронный обмен (режимы 1,2,3) данными

- •1.8.6. Скорость приёма/передачи

- •1.8.7. Работа мк в локальной сети

- •1.9. Системный сброс однокристального мк

- •1.10. Режим пониженного энергопотребления мк

- •1.11. Нагрузочная способность портов ввода/вывода

- •1. 12. Расширение портов ввода/вывода

- •Глава 2. Система команд однокристальных мк семейства mcs51

- •Способы адресации операндов

- •2.2. Команды мк

- •2.3. Правила написания программ на языке assembler

- •Метка операция операнд(ы) комментарии

- •2.3.1. Метка

- •2.3.2. Операция

- •2.3.3. Операнды

- •2.3.4. Комментарий

- •2.4. Директивы ассемблера

- •2.4.1. Директивы символических определений

- •Пример:

- •Ozu_org xdata 0800h; Адрес начала области внешнего озу.

- •2.4.2. Директивы резервирования и инициализации памяти

- •2.4.3. Директивы управления состоянием ассемблера

- •Глава 3. Обработка данных в однокристальных микроконтроллерах

- •3.1. Обращение к внутренней, внешней памяти данных и памяти программ

- •3.2. Арифметические операции

- •3.3. Логические операции

- •3.4. Операции с битами

- •Глава 4. Взаимодействие однокристального мк с объектом управления

- •4.1. Программный опрос и ожидание срабатывания позиционных датчиков

- •4.2. Ожидание импульсного сигнала

- •4.3. Программирование таймеров/счетчиков и формирование дискретных управляющих сигналов

- •4.4. Программирование прерываний в микропроцессорном устройстве

- •4.5. Программирование последовательного порта

- •Глава 5. Аппаратные средства

- •5.1. Ввод информации с клавиатуры

- •5.1.1. Прямое подключение клавиш к разрядам порта мк

- •В блоке основной программы происходит инициализация системы, разрешение прерываний, а затем выполняется основная программа.

- •Применение шифратора для организации клавиатуры

- •Шифратора

- •5.1.3. Матричный способ подключения клавиатуры

- •5.1.4. Комбинированный способ организации клавиатуры

- •5.2. Отображение информации в микропроцессорном устройстве

- •5.2.1. Контроллер клавиатуры и дисплея к580вв79 ( intel 8279 )

- •5.2.2. Матричные светодиодные индикаторы

- •5.2.3. Жидкокристаллический дисплей

- •Ввод аналоговых сигналов в микропроцессорный контроллер

- •Ацп с параллельными цифровыми выходами

- •5.3.2. Применение ацп с последовательным выходом

- •5.3.3. Применение таблиц для вычисления функций

- •5.4. Формирование управляющих аналоговых сигналов

- •5.5. Построение ацп с использованием цап

- •5.6. Микропроцессорный контроллер как управляющее устройство в системах автоматического регулирования

- •Согласование дискретных датчиков и исполнительных механизмов с однокристальным мк

- •5.8. Контроль напряжения питания в микропроцессорных системах

- •Глава 6. Отладка программного обеспечения и программирование однокристальных мк

- •6.1. Интегрированная система отладки программного обеспечения для мк ProView

- •6.1.1. Оптимизирующий кросс - компилятор c51

- •6.1.2. Макроассемблер a51

- •6.1.4. Отладчик/симулятор WinSim51

- •6.2. Запуск ProView и создание файла проекта

- •Если в системе задействованы таймеры-счетчики, то удобно промоделировать их работу при разворачивании соответствующих окон Timer (рис.76).

- •В окне указаны источники и адреса векторов прерываний, их состояние и приоритет. Разрешенные прерывания отмечены словом Enable, неразрешенные - Not Enable.

- •Рассмотрим основные пункты раздела debug (отладка), представлены на рис. 84. Эти функции предназначены для выполнения процесса отладки прикладной программы пользователя.

- •6.3. Программирование однокристальных мк

- •Контрольные вопросы для закрепления материала

- •Заключение

- •Библиографический список

- •Глава 1. Архитектура и устройство однокристальных мк семейства mcs51………………………..6

- •Глава 6. Отладка программного обеспечения и программирование однокристальных мк ……….203

- •162600, Г.Череповец , пр. Луначарского, 5

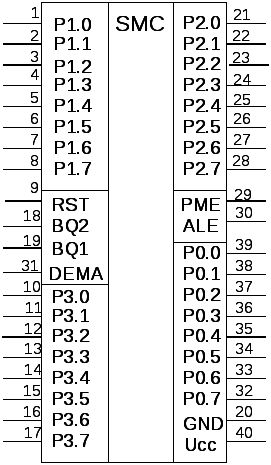

1.2. Назначение выводов микросхемы мк

Рассмотрим назначение выводов микросхемы МК, условное обозначение которой на принципиальных электрических схемах показано на рис. 2.

Р1.0 – Р1.7 – восьмиразрядный двунаправленный порт Р1, предназначен для ввода/вывода дискретной информации.

RST – вход системный микросхемы в исходное состояние, в счетчик команд записываются PC = 0000H, активный сигнал единичный.

BQ1, BQ2 - выводы для подключения кварцевого резонатора.

DEMA – вход блокировки работы с внутренней памятью, при DEMA = 0 устройство работает с внешней памятью программ, при DEMA = 1 с внутренней.

Р3.0 – Р3.7 – восьмиразрядный двунаправленный порт Р3, предназначенный для ввода вывода дискретной информации, разряды порта имеют альтернативные функции.

Р3.0 ( RxD ) – вход приемника последовательного порта.

Р3.1 ( TxD ) – выход передатчика последовательного порта.

Р3.2 ( INT0 ) – вход, внешний запрос на прерывание 0, активный сигнал нулевой.

Р3.3 ( INT1 ) – вход, внешний запрос на прерывание 1, активный сигнал нулевой.

Р3.4 ( Т0 ) – вход счетчика 0 внешних импульсов.

Р3.5 ( Т1 ) – вход счетчика 1 внешних импульсов.

Р3.6 ( WR ) –выход, стробирующий сигнал при записи данных во внешнюю память, активный сигнал 0.

Р3.7 ( RD ) – выход, стробирующий сигнал при чтении из внешней памяти данных, активный сигнал 0.

GND – вывод, подключаемый к общей шине (GROUND - GND).

UСС - вывод, подключаемый к источнику питания +5В.

Р2.0 – Р2.7 - восьмиразрядный порт Р2. При работе микросхемы с внешней памятью программ в порте Р2 выставляется старший байт адреса при обращении к внешним устройствам. Если МК имеет внутреннюю память программ, то Р2 является статическим портом и предназначен для ввода-вывода дискретной информации.

РМЕ – выход, при активном сигнале на котором происходит выборка кода команды из внешнего ПЗУ.

ALE - выход, активный сигнал которого разрешает фиксацию адреса в специальном внешнем регистре – защелке при работе МК с внешней памятью программ.

Р0.0 – Р0.7 – восьмиразрядный двунаправленный порт Р0. При работе МК с внешней памятью программ порт Р0 выступает в качестве шины адреса/данных. В Р0 выставляется младший байт адреса при обращении к внешним устройствам, в следующий момент через Р0 передаются данные, таким образом, порт Р0 является мультиплексным. При работе МК с внутренней памятью программ Р0 является статическим портом и предназначен для ввода-вывода дискретной информации.

Рис. 2. Условное обозначение МК на принципиальных электрических схемах

1.3. Организация памяти в мк

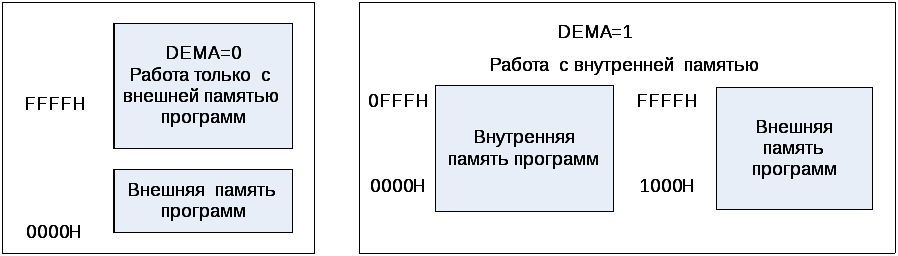

Рис. 3. Структура адресного пространства МК

Все МК семейства МК51 имеют несколько адресных пространств, функционально и логически разделенных за счет отличия в механизмах адресации и сигналах управления записью и чтением. Таким образом, для МК имеют место следующие виды памяти: внутренняя память программ; внешняя память программ; внутренняя память данных; внешняя память данных.

Рассмотрим структуру адресного пространства МК, показанную на рис. 3.

Память программ имеет 16 разрядную адресную шину, что позволяет адресовать максимально 64 кбайта ячеек. Такая память доступна только по чтению. Программа записывается в эту память посредством специального программатора. Рассматриваемая МК содержит внутреннюю память программ объемом в 4 кб, которая может быть расширена до 64 кб путем подключения внешних микросхем ПЗУ. Таким образом, внутренняя и внешняя память программ разделены в соотношении 4/60 кб. Для программиста такой раздел памяти неощутим, АЛУ автоматически выбирает байт из соответствующего адресного пространства. Сигналом, стробирующим чтение кода из внешней памяти программ, является сигнал РМЕ. Для МК, содержащих внутреннюю память программ, РМЕ формируется только в случае, если адрес в счетчике команд превышает 0FFFH. Для устройств, не имеющих внутреннего ПЗУ, РМЕ формируется при любом обращении к памяти программ.

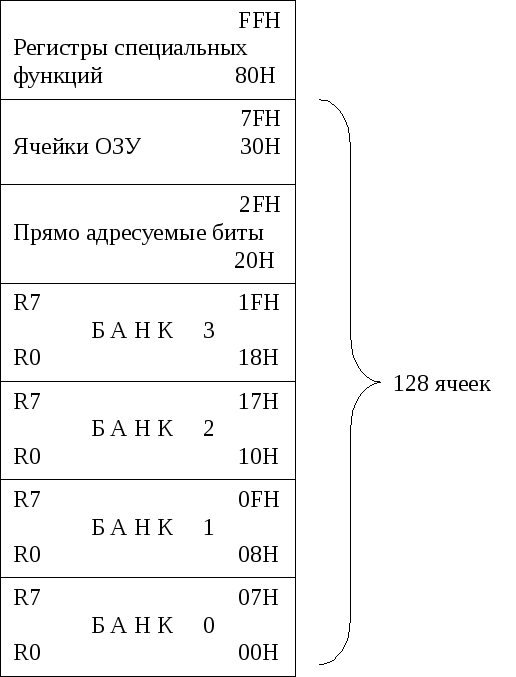

Рис. 4. Карта распределения адресов внутреннего ОЗУ МК

Внутренняя память данных МК КР1830ВЕ751 состоит из двух областей: 128 ячеек памяти (ОЗУ) с адресами 00Н - 7FH и области регистров специальных функций, занимающих адреса 80Н - 0FFH. Карта распределения адресов показана на рис. 4.

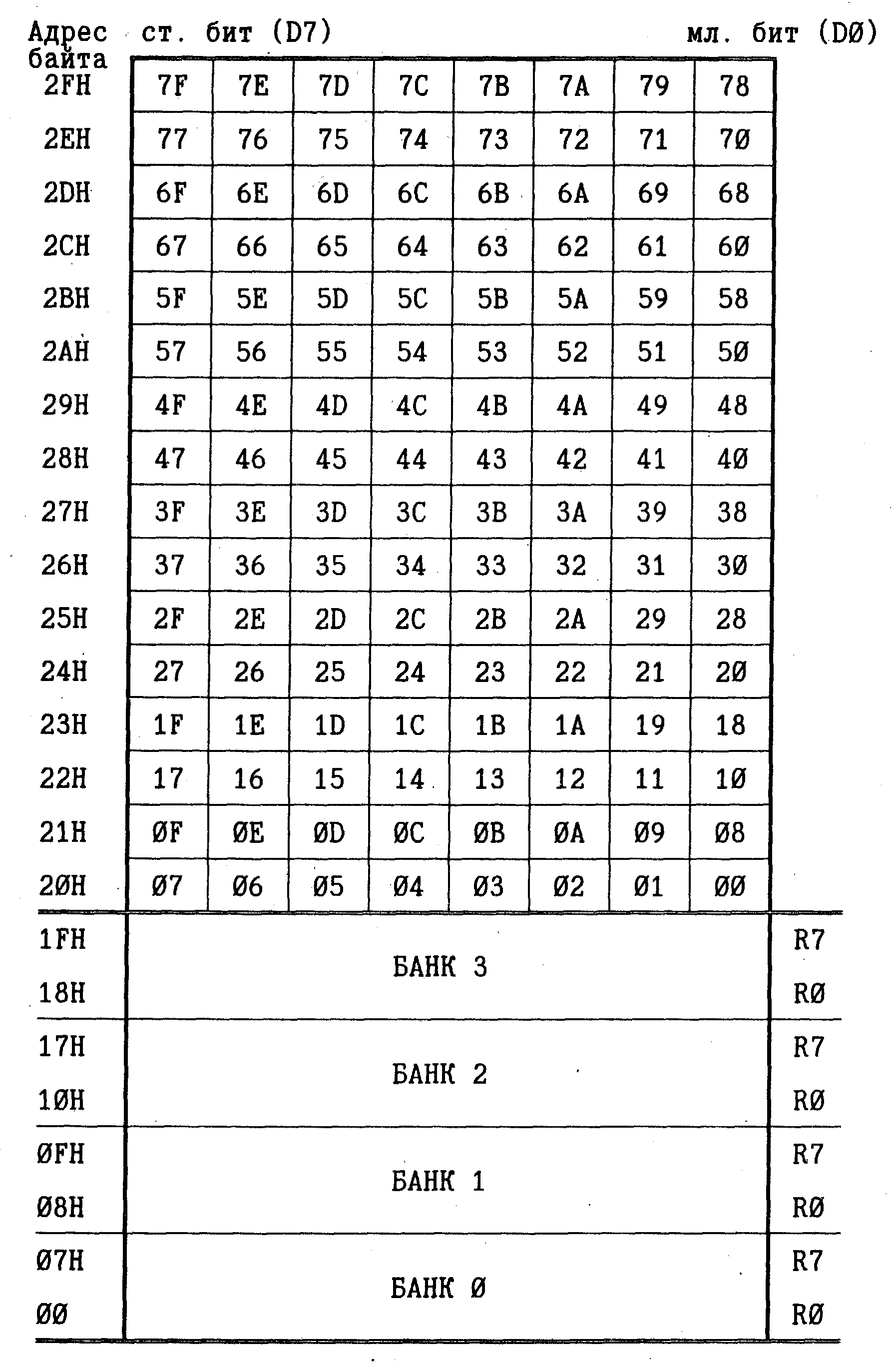

Младшие 32 байта внутреннего ОЗУ сгруппированы в 4 банка ( БАНК0 – БАНК3 ) по 8 регистров в каждом. Команды программы могут обращаться к регистрам, используя их имена R0 – R7. Следующие 16 ячеек памяти ( 20Н-2FH ) называются прямо адресуемыми битами. К ним возможна побитовая адресация, то есть программист может программным путем установить в “1”или сбросить в “0” каждый бит этих ячеек памяти. Всего 128 доступных битов. На рис.5 представлены адреса программно - доступных битов МК.

Рис.5. Адреса прямо адресуемых битов внутреннего ОЗУ МК

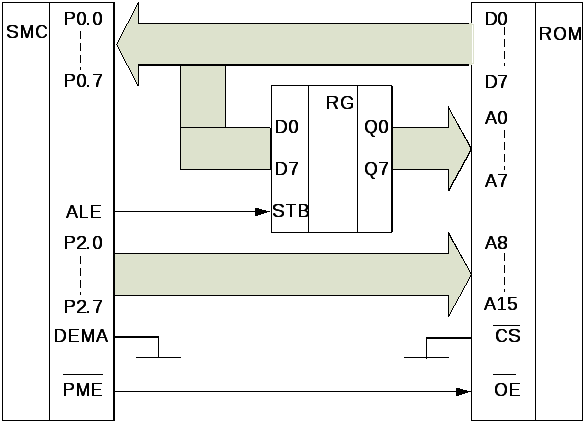

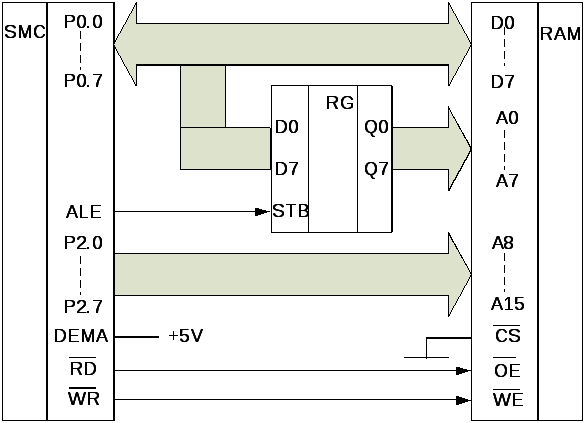

Следующие ячейки, с адреса 30Н по 7FH, представляют собой обычное ОЗУ и используются для временного хранения байтов данных. Рассмотрим функциональные схемы подключения внешней памяти программ и данных к МК, представленные на рис. 6 и 7.

Рис. 6. Функциональная схема подключения внешнего ПЗУ к МК

При обращении к внешней памяти программ всегда формируется 16- разрядный адрес (А0-А15), младший байт (А0-А7) которого выдается через порт Р0, а старший (А8-А15) через порт Р2. Особенностью работы с внешней памятью является то, что байт адреса Р0 должен быть зафиксирован во внешнем регистре-защелке RG по спаду сигнала ALE, поскольку в дальнейшем линии порта Р0 используются в качестве шины данных, по которой байт из внешней памяти программ передается в МК. Таким образом, Р0 работает как мультиплексированная шина адрес/данные. Старший байт адреса находится на выводах Р2 в течение всего времени обращения к ППЗУ. Если МК работает с внутренней памятью, сигнал РМЕ не вырабатывается и адрес в портах Р0 и Р2 не выдается. Р0 и Р2 работают как статические порты и могут быть использованы для обмена информацией с внешними устройствами.

Если для работы микропроцессорного устройства не хватает ячеек внутреннего ОЗУ, можно использовать внешнюю память данных, которая может иметь максимальный объем 64 кб, по схеме, представленной на рис. 7. Младший байт адреса аналогично вышерассмотренной схеме выдается портом Р0 и должен быть зафиксирован во внешнем регистре-защелке по спаду сигнала ALE, поскольку в дальнейшем Р0 используется как шина данных, через которую информационный байт принимается из ОЗУ при чтении или выдается в память при записи. При этом чтение данных стробируется сигналом RD, а запись – сигналом WR. При работе с внутренней памятью данных сигналы RD и WR не формируются.

Рассмотрев эти две функциональные схемы, можно сделать вывод о том, что при работе с внешней памятью у МК два порта Р0 и Р2 не могут быть использованы в качестве линий ввода-вывода общего назначения. Поэтому в полной мере все возможности МК по обмену информацией с периферийными устройствами могут быть реализованы только при работе с внутренней памятью программ.

Рис. 7. Функциональная схема подключения внешнего ОЗУ к МК с внутренней памятью программ