- •Глава 2 анализ и синтез логических схем

- •2.1. Потенциальные и импульсные сигналы

- •Если справедливо операторное тождество

- •2.2 Комбинационные схемы

- •2.3. Применение метода карт Карно для синтеза комбинационных схем

- •2.4. Двоичные дешифраторы.

- •2.5. Приоритетные и двоичные шифраторы.

- •2.6. Мультиплексоры и демультиплексоры.

- •2.7. Мультиплексор как универсальное логическое устройство

- •2.8. Компараторы.

- •2.9. Схемы контроля.

2.5. Приоритетные и двоичные шифраторы.

Двоичные шифраторы реализуют операцию, обратную по отношению к операции дешифратора: они преобразуют код «1 изN» в двоичный. При возбуждении одного из входов шифратора на его выходе формируется двоичный код номера возбужденной входной линии. Полный двоичный шифратор имеет 2n входов и n выходов.

Приоритетные шифраторы выполняют более сложную операцию. При работе устройств цифровой обработки информации часто возникает задача определения приоритетного претендента на использования какого-либо ресурса. Несколько конкурентов выставляют свои запросы на обслуживание, которые не могут быть удовлетворены одновременно. Нужно выбрать того, кому предоставляется право первоочередного обслуживания. Простейший вариант решения указанной задачи -–присвоение каждому источнику запросов фиксированного приоритета. Например, группа из восьми запросов R7…R0 (R от английского слова Request) формируется так, что высший приоритет имеет источник номер семь, далее приоритет уменьшается от номера к номеру. Самый младший приоритет имеет нулевой источник и он будет обслуживаться только при отсутствии других запросов. Если имеются несколько запросов, то обслуживаться будет запрос с наибольшим номером.

Приоритетный шифратор вырабатывает на выходе двоичный номер старшего запроса.

Указатели старшей единицы решают, по сути, ту же задачу, что и приоритетные шифраторы, но вырабатывают результат в иной форме – в виде кода «1 изN».

Таким образом, при наличии на входах нескольких возбужденных линий (запросов) на выходе будет возбуждена лишь одна, соответствующая старшему запросу.

В промышленных сериях элементов имеются шифраторы приоритета для восьмиразрядных и десятиразрядных слов. Функционирование их отображается в табл.2.2.

Таблица 2.2.

|

EI |

R7 |

R6 |

R5 |

R4 |

R3 |

R2 |

R1 |

R0 |

a2 |

a1 |

a0 |

G |

E0 |

|

1 |

1 |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

X |

X |

X |

X |

X |

X |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

X |

X |

X |

X |

X |

1 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

X |

X |

X |

X |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

X |

X |

X |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

X |

X |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

X |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

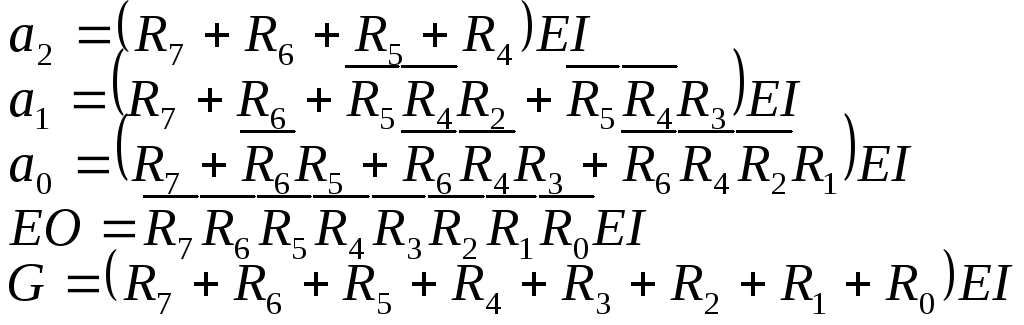

Таблица полностью отражает работу приоритетного шифратора при всех возможных комбинациях сигналов: EI – сигнала разрешения работы шифратора; Е0 – сигнала, вырабатываемого на выходе данного шифратора при отсутствии запросов на его входах для разрешения работы следующего (младшего) шифратора при наращивании размерности шифраторов; G – сигнала, отмечающего наличие сигнала запросов на входе данного шифратора; R7…R0 – запросов на входах шифратора; а2, а1, а0 значения разрядов выходного двоичного кода, формирующего номер старшего запроса. Все перечисленные сигналы формируются при условии EI=1 (работа шифратора разрешена). При EI=0 независимо от состояния входов запросов все выходные сигналы будут нулевыми. Из таблицы можно получить систему булевых выражений, описывающих работу шифратора.

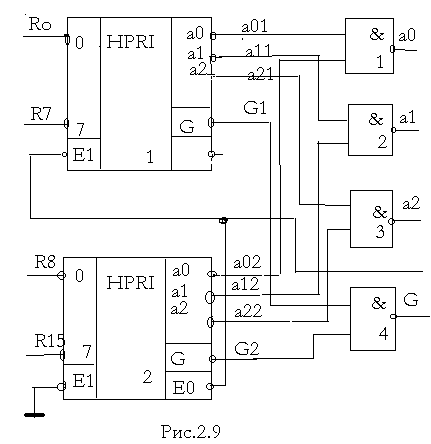

Наращивание размерности приоритетного шифратора показано на рис.2.9, на котором изображено наращивание числа входов запросов вдвое (от 8 до 16). При этом показаны шифраторы с инверсными входами и выходами, как это свойственно большинству серий ИМС.

Шифратор

2 – старший по приоритету, его работа

разрешена подачей низкого уровня

потенциала на вход Е12. Если на входах![]() есть

хотя бы один запрос на обслуживание,

то разрешения на работу младшего

шифратора не будет (Е02 = 1). Выходы

шифратора 1 пассивны, т.е. имеют единичные

значения. При этом вентили И-НЕ с номерами

1,2,3 играют роль инверторов для сигналов

есть

хотя бы один запрос на обслуживание,

то разрешения на работу младшего

шифратора не будет (Е02 = 1). Выходы

шифратора 1 пассивны, т.е. имеют единичные

значения. При этом вентили И-НЕ с номерами

1,2,3 играют роль инверторов для сигналов![]() (i

= 0, 1, 2).

Поэтому на выходах а0,

а1,

а2

формируются двоичные коды числе от

нуля до семи в зависимости от номера

старшего запроса в шифраторе 2, что

вместе с 1 на выходе Е02 дает номера от

8 до 15.

(i

= 0, 1, 2).

Поэтому на выходах а0,

а1,

а2

формируются двоичные коды числе от

нуля до семи в зависимости от номера

старшего запроса в шифраторе 2, что

вместе с 1 на выходе Е02 дает номера от

8 до 15.

Если на входах шифратора 2 запросы отсутствуют, то он разрешает работу младшего, формируя сигнал Е02=0 и приводит свои выходы а0, а1, а2 в пассивное единичное состояние. Теперь на выходы схемы передаются инверсные сигналы с выходов младшего дешифратора, что вместе с нулем в разряде а3 соответствует номерам от нуля до семи.

Таким

образом строится схема с 16 входами

запросов, причем вход

![]() имеет

старший приоритет. Выход элемента 4

принимает единичное значение при

наличии хотя бы одного запроса в любом

из шифраторов, и может быть использован

как сигнал запроса на прерывание для

процессора с последующим указанием

процессору номера старшего запроса.

имеет

старший приоритет. Выход элемента 4

принимает единичное значение при

наличии хотя бы одного запроса в любом

из шифраторов, и может быть использован

как сигнал запроса на прерывание для

процессора с последующим указанием

процессору номера старшего запроса.