- •Features

- •Description

- •Device Pinout, MSP430G2x01

- •Device Pinout, MSP430G2x11

- •Short-Form Description

- •Instruction Set

- •Operating Modes

- •Interrupt Vector Addresses

- •Special Function Registers (SFRs)

- •Memory Organization

- •Flash Memory

- •Peripherals

- •Oscillator and System Clock

- •Brownout

- •Digital I/O

- •WDT+ Watchdog Timer

- •Timer_A2

- •Comparator_A+ (MSP430G2x11 Only)

- •Peripheral File Map

- •Absolute Maximum Ratings

- •Recommended Operating Conditions

- •Electrical Characteristics

- •Active Mode Supply Current Into VCC Excluding External Current

- •Typical Characteristics - Active Mode Supply Current (Into VCC)

- •Low-Power Mode Supply Currents (Into VCC) Excluding External Current

- •Typical Characteristics Low-Power Mode Supply Currents

- •Schmitt-Trigger Inputs - Ports Px

- •Leakage Current - Ports Px

- •Outputs - Ports Px

- •Output Frequency - Ports Px

- •Typical Characteristics - Outputs

- •POR/Brownout Reset (BOR)

- •Typical Characteristics - POR/Brownout Reset (BOR)

- •Main DCO Characteristics

- •DCO Frequency

- •Calibrated DCO Frequencies - Tolerance

- •Wake-Up From Lower-Power Modes (LPM3/4) Electrical Characteristics

- •Typical Characteristics - DCO Clock Wake-Up Time From LPM3/4

- •Crystal Oscillator, XT1, Low-Frequency Mode

- •Internal Very-Low-Power Low-Frequency Oscillator (VLO)

- •Timer_A

- •Comparator_A+ (MSP430G2x11 only)

- •Typical Characteristics - Comparator_A+

- •Flash Memory

- •JTAG and Spy-Bi-Wire Interface

- •JTAG Fuse

- •APPLICATION INFORMATION

- •Port P1 Pin Schematic: P1.0 to P1.3, Input/Output With Schmitt Trigger - MSP430G2x01

- •Port P1 Pin Schematic: P1.4 to P1.7, Input/Output With Schmitt Trigger - MSP430G2x01

- •Port P1 Pin Schematic: P1.0 to P1.3, Input/Output With Schmitt Trigger - MSP430G2x11

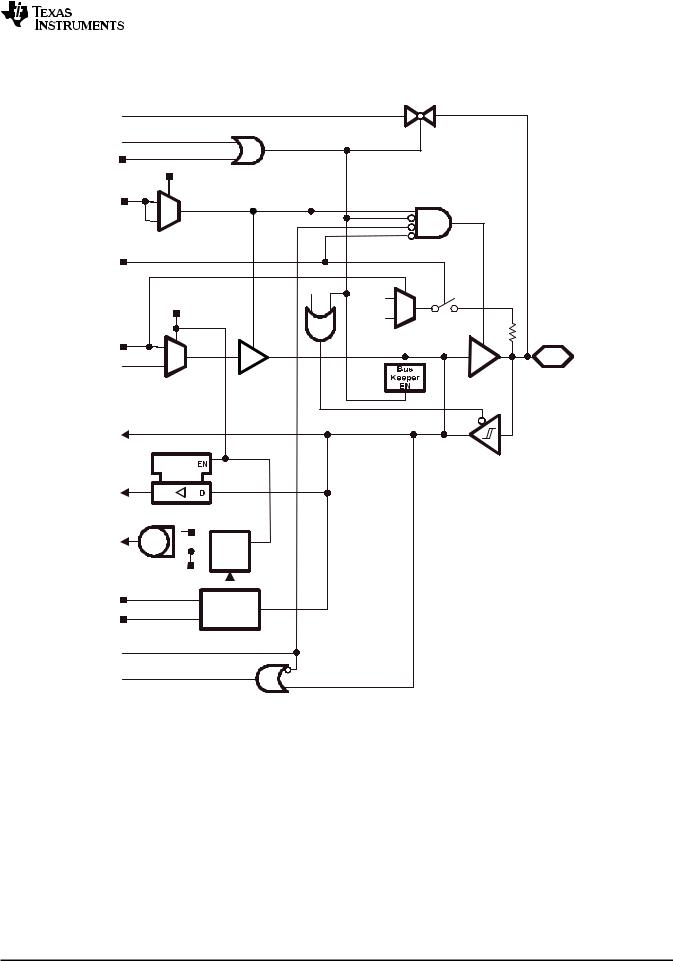

- •Port P1 Pin Schematic: P1.4 to P1.7, Input/Output With Schmitt Trigger - MSP430G2x11

- •Revision History

MSP430G2x11

MSP430G2x01

www.ti.com |

SLAS695G –FEBRUARY 2010 –REVISED DECEMBER 2011 |

Port P1 Pin Schematic: P1.4 to P1.7, Input/Output With Schmitt Trigger - MSP430G2x11

To Comparator |

|

|

|

|

From Comparator |

|

|

|

|

CAPD.y |

|

|

|

|

|

PxSEL.y |

|

|

|

PxDIR.y |

1 |

Direction |

|

|

|

|

|

||

|

0 |

0: Input |

|

|

|

|

1: Output |

|

|

PxREN.y |

|

|

|

|

|

|

DVSS |

0 |

|

|

|

PxSEL.y |

|

|

|

|

DVCC |

1 |

1 |

PxOUT.y |

|

0 |

|

|

|

|

|

|

|

From Module |

|

1 |

|

|

|

|

|

|

P1.4/SMCLK/CA4/TCK |

|

|

|

|

P1.5/TA0.0/CA5/TMS |

|

|

|

|

P1.6/TA0.1/CA6/TDI/TCLK |

|

|

|

|

P1.7/CAOUT/CA7/TDO/TDI |

PxIN.y |

|

|

|

|

To Module |

|

|

|

|

|

|

|

|

PxIE.y |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PxIRQ.y |

|

|

|

EN |

||

|

|

|

|

Q |

||

|

|

|

|

|||

|

|

|

|

Set |

||

|

|

|

|

|||

|

PxIFG.y |

|||||

PxSEL.y |

|

|

|

Interrupt |

||

|

|

|

|

Edge |

||

PxIES.y |

|

|

|

Select |

||

From JTAG

To JTAG

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback |

33 |

MSP430G2x11

MSP430G2x01

SLAS695G –FEBRUARY 2010–REVISED DECEMBER 2011 www.ti.com

Table 17. Port P1 (P1.4 to P1.7) Pin Functions - MSP430G2x11

PIN NAME (P1.x) |

x |

|

FUNCTION |

|

CONTROL BITS / SIGNALS(1) |

|

|

|

P1DIR.x |

P1SEL.x |

JTAG Mode |

CAPD.y |

|||

|

|

|

|

||||

|

|

|

|

|

|

|

|

P1.4/ |

|

P1.x (I/O) |

|

I: 0; O: 1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

SMCLK/ |

4 |

SMCLK |

|

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

CA4/ |

CA4 |

|

X |

X |

0 |

1 (y = 4) |

|

|

|

||||||

|

|

|

|

|

|

|

|

TCK |

|

TCK |

|

X |

X |

1 |

0 |

|

|

|

|

|

|

|

|

P1.5/ |

|

P1.x (I/O) |

|

I: 0; O: 1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

TA0.0/ |

5 |

TA0.0 |

|

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

CA5/ |

CA5 |

|

X |

X |

0 |

1 (y = 5) |

|

|

|

||||||

|

|

|

|

|

|

|

|

TMS |

|

TMS |

|

X |

X |

1 |

0 |

|

|

|

|

|

|

|

|

P1.6/ |

|

P1.x (I/O) |

|

I: 0; O: 1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

TA0.1/ |

6 |

TA0.1 |

|

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

CA6/ |

CA6 |

|

X |

X |

0 |

1 (y = 6) |

|

|

|

||||||

|

|

|

|

|

|

|

|

TDI/TCLK |

|

TDI/TCLK |

|

X |

X |

1 |

0 |

|

|

|

|

|

|

|

|

P1.7/ |

|

P1.x (I/O) |

|

I: 0; O: 1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

CAOUT/ |

7 |

CAOUT |

|

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

CA7/ |

CA7 |

|

X |

X |

0 |

1 (y = 7) |

|

|

|

||||||

|

|

|

|

|

|

|

|

TDO/TDI |

|

TDO/TDI |

|

X |

X |

1 |

0 |

|

|

|

|

|

|

|

|

(1) X = Don't care |

|

|

|

|

|

|

|

34 |

Submit Documentation Feedback |

Copyright © 2010–2011, Texas Instruments Incorporated |

MSP430G2x11

MSP430G2x01

www.ti.com |

SLAS695G –FEBRUARY 2010 –REVISED DECEMBER 2011 |

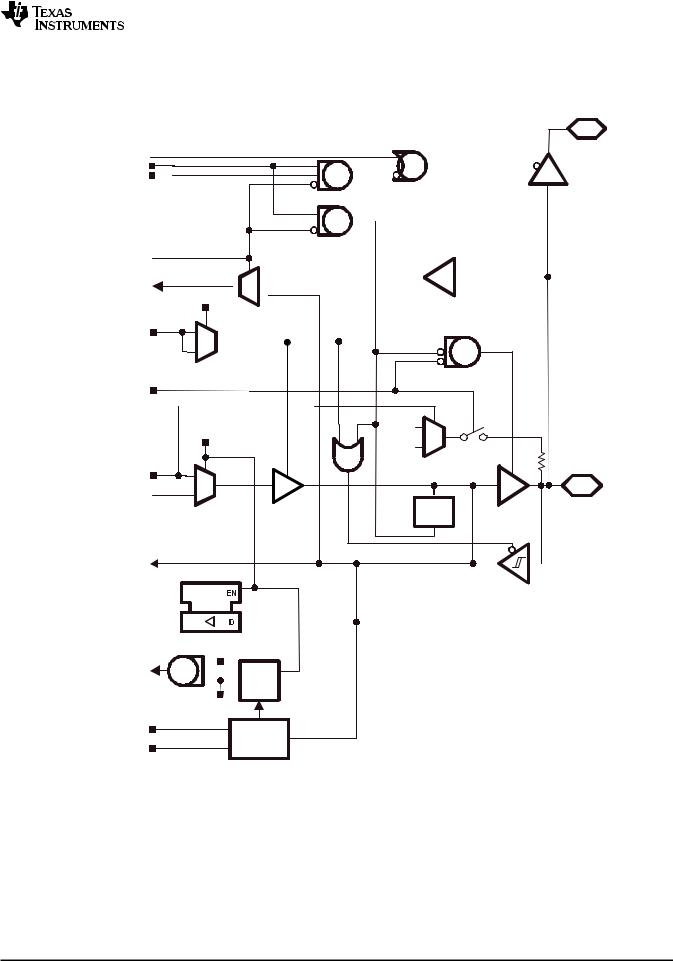

Port P2 Pin Schematic: P2.6, Input/Output With Schmitt Trigger - MSP430G2x01 and

MSP430G2x11

LF off

PxSEL.6

PxSEL.7

BCSCTL3.LFXT1Sx = 11

LFXT1CLK

PxDIR.y

PxREN.y

PxOUT.y

From Module

PxIN.y

To Module

XOUT/P2.7

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PxSEL.6 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1 |

|

Direction |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|||||||||||

0 |

|

0: Input |

|

|

|

|

|

||||||||||

|

|

1: Output |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DVSS |

0 |

|

PxSEL.6 |

|

|

DVCC |

1 |

1 |

0

1

Bus |

|

|

|

XIN/P2.6/TA0.1 |

Keeper |

|

|

|

|

|

|

|

|

|

EN |

|

|

|

|

|

|

|

|

|

PxIE.y

PxIRQ.y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|||

|

|

|

|

Q |

||

|

|

|

|

|||

|

|

|

|

Set |

||

|

|

|

|

|||

|

|

PxIFG.y |

||||

PxSEL.y |

|

|

Interrupt |

|||

|

|

|

|

Edge |

||

PxIES.y |

|

|

Select |

|||

Table 18. Port P2 (P2.6) Pin Functions - MSP430G2x01 and MSP430G2x11

PIN NAME (P2.x) |

x |

|

FUNCTION |

CONTROL BITS / SIGNALS(1) |

||

|

P2DIR.x |

P2SEL.6 |

P2SEL.7 |

|||

|

|

|

|

|||

|

|

|

|

|

|

|

XIN |

|

XIN |

|

0 |

1 |

1 |

|

|

|

|

|

|

|

P2.6 |

6 |

P2.x (I/O) |

|

I: 0; O: 1 |

0 |

X |

|

|

|

|

|

|

|

TA0.1 |

|

Timer0_A2.TA1 |

|

1 |

1 |

X |

|

|

|

|

|

|

|

(1) X = Don't care

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback |

35 |

MSP430G2x11

MSP430G2x01

SLAS695G –FEBRUARY 2010–REVISED DECEMBER 2011 |

www.ti.com |

Port P2 Pin Schematic: P2.7, Input/Output With Schmitt Trigger - MSP430G2x01 and

MSP430G2x11

XIN/P2.6/TA0.1

LF off PxSEL.6 PxSEL.7

BCSCTL3.LFXT1Sx = 11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

LFXT1CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

from P2.6/XIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

PxSEL.7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

PxDIR.y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

1 |

|

|

|

Direction |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

0 |

|

|

|

0: Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1: Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

PxREN.y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DVSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PxSEL.7 |

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

PxOUT.y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DVCC |

|

1 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

From Module |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bus |

|

|

|

|

|

|

|

|

|

|

XOUT/P2.7 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Keeper |

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

PxIN.y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

To Module |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

PxIE.y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

PxIRQ.y |

|

|

|

|

|

|

|

|

|

|

|

EN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Set |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

PxIFG.y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

PxSEL.y |

|

|

|

|

|

|

|

|

|

Interrupt |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Edge |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

PxIES.y |

|

|

|

|

|

|

|

|

|

Select |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

Table 19. Port P2 (P2.7) Pin Functions - MSP430G2x01 and MSP430G2x11 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

PIN NAME (P2.x) |

|

x |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FUNCTION |

|

|

|

|

|

|

|

|

|

|

|

|

CONTROL BITS / SIGNALS |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P2DIR.x |

|

|

|

P2SEL.6 |

P2SEL.7 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

XOUT |

|

7 |

|

|

XOUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

1 |

1 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P2.7 |

|

|

|

P2.x (I/O) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I: 0; O: 1 |

|

|

|

0 |

0 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

Submit Documentation Feedback |

Copyright © 2010–2011, Texas Instruments Incorporated |