Нейросетевые технологии / АСУ Скобцов Искусственные нейронные сети лекции

.pdf

61

Рис.26 Цифровая реализация нейрона,

Сумматор представляет меньше проблем, поскольку может быть использована стандартная библиотека двоичных сумматоров. Декодер может быть реализован либо табличным способом (допускающим любую активационную функцию), либо последовательным соединением нескольких пороговых детекторов.

ПЛИС (FPGA) (особенно Xilinkx) широко используются в настоящее время при цифровой реализации НС. Они являются компромиссом между непрактичными схемами дискретных компонент и стоимостью. Размер ПЛИС все время растет и скоро достигнет 10 миллионов вентилей, что уже достаточно для реализации НС, используемых в приложениях. Основной причиной популярности ПЛИС является возможность перестройки внутренней конфигурации соединений электронным способом в процессе функционирования. Эти свойства делают их идеальным инструментом для экспериментов с растущими или эволюционируюшими НС.

Цифровые нейрочипы, как правило, реализуются на основе трех основных

архитектур:

1) SIMD - архитектура;

62

2)Систолические матрицы (массивы);

3)Секционированная (slice) архитектура .

Цифровые нейрочипы имеют следующие преимущества:

1)высокоразвитая технология производства;

2)хранение синаптических весов в ОЗУ;

3)при арифметических операциях сохраняется точность(число бит сумматора соответствует количеству разрядов операндов);

4)цифровые чипы легко интегрируются в большинство

приложений (которые реализуются в настоящее время, в

основном, в цифровом виде).

Кнедостаткам цифровых нейрочипов можно отнести:

1)арифметические операции обычно выполняются медленнее, чем в аналоговых системах (особенно умножение векторов входных значений и синаптических весов);

2)реальный мир (окружение - среда) аналоговый, поэтому необходимы преобразователи АЦП и ЦАП.

Секционированная архитектура основана на использовании дешевых одноразрядных типовых элементов, которые можно собирать и конструировать нейросети произвольной разрядности и точности.

В чипе, реализованном согласно SIMD-архитектуре параллельно функционируют множество элементов, каждый из которых одновременно выполняет одну и туже команду (инструкцию) на различных данных.

Развитию этого подхода способствуют развитые технологии, методы, и

средства проектирования, которые позволяют реализовать многие типы нейросетей.

В систолических структурах каждый элемент-процессор выполняет один шаг вычислений (один элемент все время одну и ту же операцию) и

полученный результат передает далее на следующий процессор в конвейере.

В систолических структурах эффективно реализуются произведения матриц и векторов (занимающие существенную часть вычислений в НС - X*W).

63

Цифровые сигнальные процессоры также широко используются в качестве элементной базы и имеют преимущество перед универсальными микропроцессорами – возможность работы на максимальных тактовых частотах и реализации практически всех операций алгоритма управления на аппаратном уровне. Это позволяет проектировать на их основе высокопроизводительные нейрокомпьютеры (рассматриваемые в следующем разделе). Однако при изменении алгоритма управления большинство коррекций приходится на схемотехнические решения, что является платой за высокое быстродействие.

Аналоговая реализация модели искусственного нейрона представлена на рис.27. Здесь усилители выполняют умножение входных сигналов на свои синаптические веса. Для обученной сети сети (это возможно путем эмуляции) усилители должны иметь фиксированные коэффициенты усиления. В этом случае нет особых проблем с реализацией. Однако, если сеть предполагается доучивать в процессе эксплуатации, должна быть возможность изменять коэффициенты усиления. Это можно реализовать различными средствами.

Рис.27.Аналоговая реализация нейрона

64

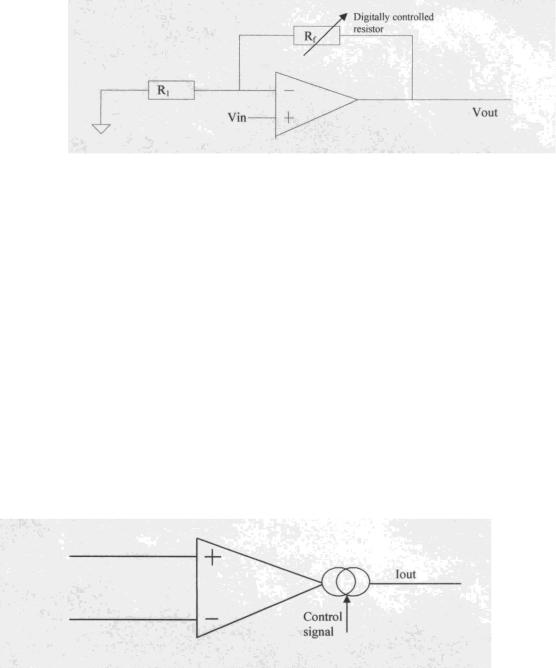

Например, при использовании операционных усилителей (Op-Amps)

применяются резисторы с цифровым управленим, как показано на рис.28.

Такие резисторы могут устанавливаться в требуемые значения одним цифровым сигналом. Все резисторы с помощью мультиплексора могут управляться единственным цифровым сигналом.

Рис.28 Управляемый усилитель

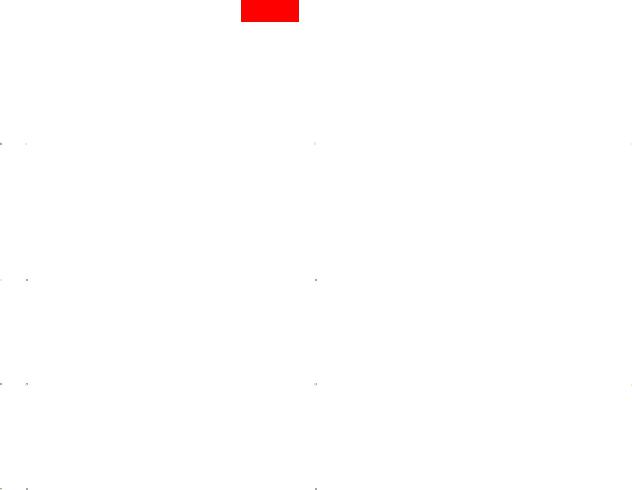

Болем элегантной реализацией управляемых синаптических весов является применение операционных усилителей тока, управляемых напряженим, которая представлена на рис.29 Здесь усилитель на выходе дает ток, который конвертируется (назад) в напряжение.

В настоящее время стали доступны FPAA, которые подобно АЗПФ могут перепрограммироваться в процессе функционирования схемы. Это позволяет реализовать динамические схемы с изменяемыми параметрами и топологией, что дает большие возможности для реализации НС.

Рис.29 Операционный усилителель тока, управляемый напряженим

65

Основными преимуществами аналоговых нейрочипов являются:

1)высокое быстродействие;

2)высокая плотность;

3)простая реализация арифметических операций (например,

электрическое соединение |

синаптических входов реализует |

суммирование).

К недостаткам можно отнести:

1)сложность проектирования вследствие необходимости компенсировать влияние окружающей среды (температура, влажность и т.п.);

2)сложность запоминания синаптических весов (особенно в случае необходимости их неизменности);

В гибридных нейрочипах пытаются комбинировать цифровые и аналоговые технологии, используя лучшие свойства тех и других с целью получения их лучших характеристик. Распространены следующие варианты гибридицации:

1)для повышения быстродействия используется внутренняя аналоговая обработка, но синаптические коэффициенты хранятся в цифровом виде

(например, на периодически восстанавливаемых емкостях);

2)сети с импульсной модуляцией используют отношение или ширину импульсов для эмуляции амплитуды входов, выходов и синаптических весов.

Кгибридным также можно отнести так называемые «нейроморфические»

(neuromorphic) НС, в которых точнее моделируются естественные нейронные структуры. Здесь обработка сигналов выполняется аналоговыми средствами, хотя выходы могут быть цифровыми. Функционально они реализуют скорее сенсоры, чем классификаторы.

Аналогично к гибридным относятся так называемые Pulse Couple Neural Networks (PCNN) (с импульсной модуляцией парные НС),

построенные по образцу зрительной системы млекопитающихся. Эти НС могут эффективно выполнять препроцессорную обработку изображений, в

66

том числе, выделение контуров и сегментацию. Они инвариантны относительно поворотов, изменения масштаба и переноса изображений.

Рассмотренные технологии (как цифровые так и аналоговые) основаны на использовании свойств полупроводников. Известны работы по реализации НС на других физических принципах. К ним можно отнести, например, оптические и квантовые устройства. Оптические НС даже реализованы в исследовательских лабораториях, но пока их характеристики не позволяют применять их в практических задачах (не говоря уже о конкуррентноспособности).

3.3Аппаратная реализация нейрокомпьютеров

Внастоящее время можно выделить три основных направления развития вычислительных систем с массовым параллелизмом (ВСМП) [], представленные в табл.1 [10] Власов.

|

|

|

|

|

|

|

Таблица 1 |

|

|

|

|

|

|

|

|||

№ |

Наименование направления |

|

Описание |

|

|

|||

|

|

|

|

|

|

|

||

|

ВСМП |

на |

базе каскадного |

Элементная база - |

универсальные |

|||

|

RISC или CISC процессоры: Intel, |

|||||||

1 |

соединения |

универсальных |

SISD, |

|||||

AMD, Sparc, Alpha, Power PC, MIPS и |

||||||||

|

SIMD, MISD микропроцессоров. |

|||||||

|

т.п. |

|

|

|||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

На |

базе |

процессоров |

с |

Элементная база - DSP процессоры: |

|||

2 |

распараллеливанием |

на |

||||||

TMS, ADSP, Motorola, ПЛИС. |

||||||||

|

аппаратном уровне. |

|

||||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

ВСМП |

на |

специализированной |

Элементная |

база |

от |

||

3 |

специализированных |

однобитовых |

||||||

элементной базе |

|

|||||||

|

|

процессоров до нейрочипов. |

|

|||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

67

Нейросетевые системы, реализованные на аппаратных платформах первого направления ( даже многпроцессорных) обычно относят к нейроэмуляторам -

т.е. системам реализующим типовые нейрооперации (умножение X*W,

суммирование и нелинейное преобразование) на программном уровне.

Нейросети, реализованные на аппаратных платформах второго и третьего направления в виде плат расширения стандартных вычислительных систем

(1-го направления) - называют нейроускорителями и системы, реализованные на аппаратной платформе третьего направления в виде функционально законченных вычислительных устройств, относят к нейрокомпьютерам (все операции выполняются в нейросетевом логическом базисе).

Нейроускорители можно разделить на два класса "виртуальные" (вставляемые в слот расширения стандартного РС) и "внешние" (соединяющиеся с управляющей Host ЭВМ по конкретному интерфейсу или шине) [2-5]. Далее рассмотрим принципы реализации и основные структурно-функциональные особенности нейровычислителей второго и третьего типа на конкретных примерах.

Нейроускорители на базе ПЛИС.

Построение нейровычислителей на базе ПЛИС с одной стороны позволяет гибко реализовать различные нейросетевые парадигмы, а с другой сопряжено с большии проблемами разводки всех необходиых межсоединений. Выпускаемые в настоящее время ПЛИС имеют различные функциональные возожности (с числом вентилей от 5 до 100 тысяч).

Нейровычислители на базе ПЛИС - как правило позиционируются как гибкие нейровычислительные систеы для научно-исследовательских целей и мелкосерийного производства. Для построения более производительных и эффективных нейровычислителей, как правило, требуется применение сигнальных процессоров. Вопросам создания нейровычислителей на ПЛИС посвящено большое число работ [?-В-3].

68

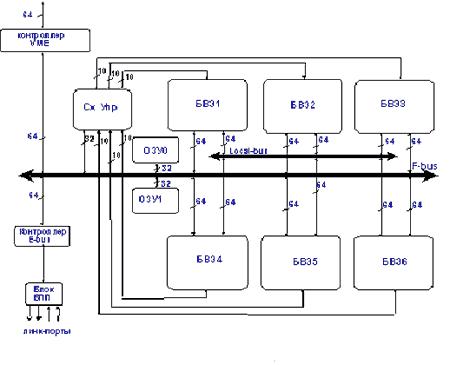

Параллельный перепрограммируемый вычислитель (ППВ) разработан в стандарте VME и реализован на базе перепрограммируемых микросхем семейства 10К фирмы Altera. Вычислитель предназначается для работы в качестве аппаратного ускорителя и является ведомым устройством на шине

VME. Он должен включаться в систему как подчиненное устройство основной управляющей ЭВМ (host-машины) с универсальным процессором.

Тактовая частота вычислителя 33 МГц [?-В-3].

ППВ используется для построения систем распознавания образов на основе обработки телевизионной, тепловизионной и другой информации, а

также систем, основанных на реализации алгоритмов с пороговыми функциями и простейшими арифметическими операциями и позволяет добиться значительной скорости вычислений.

Вычислитель состоит из следующих функциональных блоков [?-В-3]:

схема управления (Сх Упр);

базовые вычислительные элементы (БВЭ1-БВЭ6);

контроллер внешней шины (Контроллер E-bus);

контроллер системной шины (Контроллер VME);

два массива статической памяти (ОЗУ0, ОЗУ1);

блок высокоскоростных приемников/передатчиков.

Схема управления используется для управления БВЭ и потоками данных в вычислителе и представляет собой простейший RISC процессор. Структура и набор команд процессора могут изменяться в зависимости от типа решаемой задачи.

БВЭ используются для выполнения простейших арифметических операций типа суммирования, вычитания, умножения и вычисления пороговых функций. Так как БВЭ реализованы на перепрограммируемых микросхемах, их архитектура может изменяться. Архитектура БВЭ для различных алгоритмов может отличаться, но обычно легко реализуются

69

путем комбинации библиотечных функций, компиляции их при помощи САПР (типа MaxPlus) и загрузки файла конфигурации в выбранный БВЭ.

Рис.29 Структурная схема ППВ [3].

Два массива локальной статической памяти собраны из 8 микросхем статической памяти емкостью 0,5 Мбайт, имеют размер 4Мбайт и организованы как массив 512К 8-байтовых слов. Массивы памяти связаны со схемой управления отдельными адресными шинами и могут функционировать независимо друг от друга. Память предназначена для хранения общих коэффициентов, а также промежуточных результатов вычислений или окончательных результатов, подготовленных к передаче через контроллер системной шины в центральный процессор или через контроллер E-bus на линк-порты.

Связь нескольких вычислителей между собой или вычислителя с устройством оцифровки изображения, при наличии у устройства оцифровки соответствующего интерфейса, осуществляется посредством последовательного канала приемников/передатчиков HOTLink фирмы

CYPRESS. Управление передачей данных выполняет контроллер внешней

70

шины, который представляет из себя набор 4-х стандартных FIFO и

регистров управления и данных. Контроллер шины VME выполняет функцию интерфейса с центральным процессором и является стандартным устройством.

С точки зрения программиста вычислитель можно представить как

RISC-процессор (схема управления или управляющий процессор) и шесть векторных процессоров (вычислительных элементов), отрабатывающих

SIMD-команды (одна команда для многих данных). Большое количество шин данных, возможность одновременной работы всех БВЭ и выполнение арифметических операций умножения и сложения за один такт позволяет эффективно распараллеливать процесс обработки информации.

Нейроускорители на базе каскадного соединения сигнальных процессоров

Нейровычислители на основе сигнального процессора, как правило,

являются быстродействующими и надежными устройствами для ввода,

вывода и обработки аналоговой и цифровой информации. При этом их можно рассматривать и как удобное средство для многоканального сбора информации, так и как законченную систему с собственным процессором,

позволяющую реализовать алгоритмы по предварительной обработки сигналов на уровне программирования установленного на платах сигнального процессора, в качестве которых могут использоваться DSP

американских фирм Analog Devices (cерий ADSP21xx, ADSP21xxx), Texas

Instruments (TMS320C1x,2x,5x,6201, TMS320C3x,4x,8x), а также DSP фирм

Motorola (DSP56100, DSP56000, DSP96000), AT&T Microelectronics (DSP32C)

и др.

Такие нейровычислители представляют собой мультипроцессорные системы с возможностью параллельной обработки, что позволяет реализовывать на их основе нейровычислительные системы, в структуре которых можно выделить две основные части: