Нейросетевые технологии / АСУ Скобцов Искусственные нейронные сети лекции

.pdf

71

управляющую Host-ЭВМ, реализованную на основе обычной вычислительной системы с CISC или RISC микропроцессорами;

виртуальное (или внешнее) аппаратное средство, подключаемое к Host-

ЭВМ посредством внутренних (внешних) системных интерфейсов,

выполняющее основные вычислительные операции.

Остановимся на особенностях аппаратной реализации нейровычислителя

(НВ) с возможностью параллельной обработки, реализующие элементы нейросети.

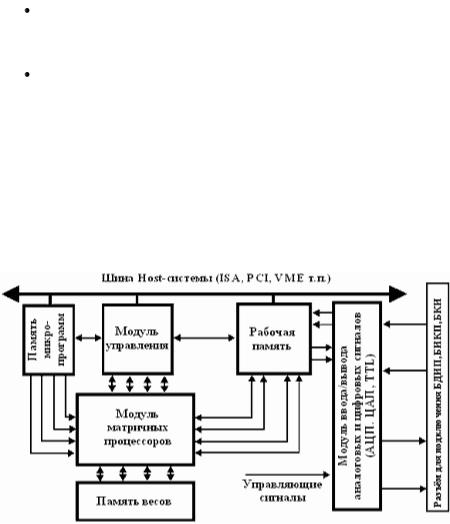

Рис.30 Обобщенная функциональная схема виртуального НВ.

В основе построения НВ данного типа лежит использование сигнальных процессоров, объединенных между собой согласно определенной архитектуры, которая обеспечивает параллельность выполнения вычислительных операций. Как правило, такие НВ строятся на основе гибкой модульной архитектуры, которая обеспечивает простоту конфигурации системы и наращиваемость вычислительной мощности путем увеличения числа процессорных модулей или применения более производительных сигнальных процессоров (рис.30). НВ данного типа реализуются в основном на базе несущих модулей стандартов ISA, PCI, VME. Основными их функциональными элементами являются модуль матричных сигнальных процессоров (МСП), рабочая память, память программ, модуль обеспечения

72

ввода/вывода сигналов (включающий АЦП, ЦАП и TTL линии), а также модуль управления, который может быть реализован на основе специализированного управляющего сигнального процессора (УП), на основе ПЛИС или иметь распределенную структуру, при которой функции общего управления распределены между МСП.

Для построения НВ данного типа наиболее перспективным является использование сигнальных процессоров с плавающей точкой ADSP2106x, TMS320C4x,8x, DSP96002 и др.

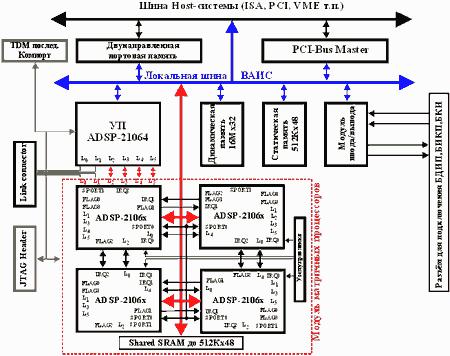

Типовая структурная схема реализации НВ на основе сигнальных процессоров ADSP2106x приведена на рис.31 [?-В-5]. В еѐ состав включены один управляющий сигнальный процессор для осуществления функций общего управления, и до восьми процессоров осуществляющих параллельные вычисления согласно заложенным алгоритмам (матричные сигнальные процессоры).

Управляющий и матричные процессоры образуют кластер процессоров с общей шиной и ресурсами разделяемой памяти. Обмен информацией между управляющим процессором, матричными процессорами, Host-ЭВМ и внешней средой осуществляется посредством портов ввода/вывода. Для тестирования и отладки предназначен отладочный JTAG-порт. Так, в случае использования четырех МСП, обмен информацией между ними и УП осуществляется посредством четырех связанных портов ADSP2106x, по два связанных порта УП и модуля МСП выводятся на внешние разъемы для обеспечения связи с внешними устройствами. Имеется 12 внешних линков, а

по 3 линка каждого из МСП предназначены для внутримодульного межпроцессорного обмена. Синхронизация работы системы может осуществляться как от внутренних кварцевых генераторов, так и от внешних генераторов. Активизация вычислений программная или внешняя.

Для ввода/вывода и АЦ/ЦА преобразований сигналов предназначен специализированный модуль, который включает в себя: универсальный цифровой TTL порт, АЦП, ЦАП, узел программируемых напряжений для

73

смещения шкал АПЦ и установки порога срабатывания стартовых компараторов, узел фильтрации выходных аналоговых сигналов, подсистему тестирования, узел синхронизации и управления, буферную память FIFO.

Первоначальная загрузка осуществляется по Host-интерфейсу или по линкам.

Управляющий интерфейс любого МСП позволяет управлять процессорным сбросом и прерываниями, его идентификационным номером и т.п.

Рис.31. Реализация НВ на основе ADSP2106x

Такая архитектура НВ обеспечивает выполнение операций ЦОС в реальном времени, ускорение векторных вычислений, возможность реализации нейросетевых алгоритмов с высоким параллелизмом выполнения векторных и матричных операций.

Нейрокомпьютеры

74

Практически единственно возможным способом построения эффективных многомерных и многосвязанных нейровычислительных систем,

как было отмечено выше, является их реализации на основе нейросетевого логического базиса. Только при таком подходе удается добиться работы многомерных нейросистем в реальном масштабе времени. Данных подход подразумевает построение вычислительной системы на основе нейрокомпьютера, который чаще всего реализуется в виде модуля параллельно работающих спецпроцессоров - нейровычислителей.

Использование специализированных нейропроцессоров (НП) позволяет еще больше увеличить порядок практически реализуемых многомерных систем. В [?-В-7] приведена оценка производительности некоторых нейрокомпьютеров. Так, например, для НК0I.04 (серия “Геркулес”), с

трактом конвейера 120 нс, пиковое быстродействие при параллельно работающих двух нейровычислителях на матричных и векторных операциях составляет 60 нс., что соответствует 16x106 переключений связей в секунду.

Число эмулируемых связей в нейросети зависит от емкости памяти весов и векторов нейровычислителя и их разрядности. Для НК0I.04 (2 НП) при 16

разрядных векторах число эмулируемых связей составляет 512 103. Число эмулируемых нейронов определяется структурой нейросети, возможным числом реализуемых связей и объемом памяти программ (память нейросети).

При реализации нейросетей с многовходовыми нейронами число эмулируемых связей нейронов убывает с ростом числа входов. Для НК0I.04

при размерности входного вектора 256 и числе входов нейронов также равном 256, число эмулируемых нейронов составит 2000 (355), т.е. возможно реализовать АСАГ с пространственной размерностью равной 2000 (произведение числа каналов на число слоѐв НС должно быть не более 2000).

При использование одного нейровычислителя с трактом конвейера 120 нс время выполнения операции перемножения 256 мерного вектора на квадратную матрицу размерностью 256 составит 8 мс.

75

Критерии оценки производительности НС

Наиболее распространенным критерием оценки производительности является число соединений в секунду (connection-per-sec CPS) , которое определяется как число операций умножения и сложения в секунду в процессе запуска и функционирования сети. Однако, следует отметить, что сеть с четырехразрядными весами и входами не всегда можно считать лучше сети, имеющей худший показатель CPS, но 16-разрядные веса и входы.

Для измерения скорости обучения иногда используется увеличение числа соединений в секунду(Connection-Update-Per-Sec CUPS). Этот критерий, естественно зависит от применяемого алгоритма обучения. Чип,

выполненный на основе сети с радиальным базисом (RBF), может иметь меньший коэффициент CUPS по сравнению с чипом, реализующим многослойную НС прямого распространения, но обучается за меньшее число итераций. К сожалению, в настоящее время нет стандартных тестовых данных (standard benchmark datasets) для оценки эффективности аппаратной реализации НС.

76

Вопросы для самоконтроля

1.Что такое искусственный нейрон? Приведите его схему и опишите функционирование первого и второго каскадов.

2.Что такое активационные функции? Приведите основные активационные функции в аналитическом и графическом виде.

3.Найдите выражения для производных сигмоидальной и тангенциальной активационных функций. Каково значение этих производных в начале координат?

4.Приведите основные типы архитектур искусственных нейронных сетей.

5.Приведите пример однослойного персептрона с 5 входами и 2 выходами.

6.Приведите пример двухслойной НС в виде схемы с 7 входами и 3

выходами, активационные функции первого слоя сигмоидные, а второго – линейные.

7.Приведите пример многослойной НС.

8.Чем отличаются НС прямого распространения от рекуррентных?

9.Приведите два режима работы персептрона.

10.Что такое “обучение с учителем” ?

11.Какие недостатки вы видите в алгоритме обучения персептрона?

12.Что дает увеличение числа слоев в сети прямого распространения?

13.Какие параметры НС изменяются в процессе обучения?

14.Что минимизируется в методе обратного распространения?

15.Ч то такое “обучающая выборка”?

16. Какие два этапа в методе обратного распространения?

17.Что в этом методе распространяется вперед (от входов к выходам) и что в обратном направлении?

18.Что такое “обучение без учителя” ?

19.Чем отличается классический метод обучения Хэбба от дифференциального?

77

20.Какие два основных подхода в обучении “без учителя” ?

21.Чем отличается обучение “по Кохонену” от обучения “по Хэббу” ?

22.Что такое “нейрон-победитель” ?

23.Приведите методы определения нейрона-победителя.

24.В какую сторону вращаются весовые вектора “нейронов-победителей и побежденных” ?

25.Чем отличаются карты Кохонена от сетей Кохонена?

26.Какую роль играют внутрислойные связи в картах Кохонена?

27.Чем отличается коррекция весов в картах Кохонена?

28.Приведите функции определения расстояния на карте Кохонена.

29.Чем отличаются рекуррентные НС от сетей прямого распространения?

30.Приведите структуру сети Хопфилда с 4 нейронами в двух видах.

31.Что такое состояние сети Хопфилда? Чем отличаются устойчивые

состояния от неустойчивых?

32.Что такое функция энергии сети Хопфилда и чем она определяется?

33.Что такое ассоциативная память?

34.Приведите алгоритм обучения сети Хопфилда.

35.Приведите основные прикладные аспекты применения нейронных сетей.

36.В чем заключается предварительная обработка данных?

37.Что такое обучающее и тестовое множество?

38.Приведите основные вида кодирования выходных сигналов НС.

39.Приведите список основных задач, которые можно решать с помощью НС.

40.Что такое нейроэмулятор и каковы его состав и функции?

41.Приведите основные способы реализации элементной базы НС.

42.Приведите основные подходы цифровой реализации нейрочипов.

43.Приведите основные направления реализации аппаратной реализации нейрокомпьютеров.

78

Литература к разделу

1.Ф. Уоссерман. Нейрокомпьютерная техника: теория и практика/ под ред. А.И. Галушкина. М.: Мир. 1986.

2.В.В.Круглов,В.В.Борисов.Искусственные нейронные сети.- М:Горячая линия.-Телеком,2001.-382с.

3.Л.Г.Комарцова,А.В.Максимов.Нейрокомпьютеры.-Москва:МГТУ им.Баумана.2002.-320с.

4.О.Г.Руденко, Е.В.Бодянский. Основы терии искусственных нейронних сетей.-Харьков:2002.-2002.-317с.

5.В.Дьяконов,В.В.Круглов. Математические пакеты расширения МАТЛАБ.Специальный справочник.Спб:Питер.-2001.-480с.

6.В.С.Медведев, В.Г.Потемкин. Нейронные сети.МАТЛАБ.- М:Диалог.-МИФИ.-2002.-496с.

7.С.Осовский. Нейронные сети для обработки информации.Москва: Финансы и статистика .-2002.-344с.

8.А.В. Назаров, А.И. Лоскутов. Нейросетевые алгоритмы прогнозирования и оптимизации систем.С.Петербург:Наука и техника.-2003.-384с.

9.В. Шахнов, А. Власов, А. Кузнецов. Нейрокомпьютеры - архитектура и реализация. Часть 2.2 Элементная база нейровычислителей//

10.В. Шахнов, А. Власов, А. Кузнецов. Нейрокомпьютеры - архитектура и реализация. Часть 3. Аппаратная реализация нейровычислителей // 11.А.Власов.Аппаратная реализация нейровычислительных

систем//http://neuronews.iu4.bmstu.ru

12.Нейрокомпьютеры и их применение. Книга 7. Нейрокомпьютеры в системах обработки изображений/ под общей редакцией А.и.Галушкина.-М.:Радиотехникаб2003.-192с.

13.Комашинский В.и.,Смирнов Д.а.нейронные сети и их применение в системах управления и связи.-М.:Горячая линия.-Телекомб2002.-94с.

Дополнительная литература

1.Галушкин А.И. Некоторые исторические аспекты развития элементной базы вычислительных систем с массовым параллелизмом (80- и 90-е годы) // Нейрокомпьютер. 2000. № 1. С. 6882.

2.Горбань А.Н., Россиев Д.А. Нейронные сети на персональном компьютере. Новосибирск: Наука. Сибирская издательская фирма РАН. 1996. 276 с.

3.Кирсанов Э.Ю. Цифровые нейрокомпьютеры: Архитектура и схемотехника / Под ред. А.И. Галушкина. Казань: Казанский Гос. У-т. 1995. 131 с.

4.Уоссермен. Нейрокомпьютерная техника / под ред. А.И. Галушкина. М.: Мир. 1986.

79

5.Роберт Хехт-Нильсен. Нейрокомпьютинг: история, состояние, перспективы // Открытые системы. 1998. № 4.

6.Власов А.И. Аппаратная реализация нейровычислительных управляющих систем //Приборы и системы управления. 1999. № 2. С.

6165