Скобцовы Моделирование и тестирование

.pdf

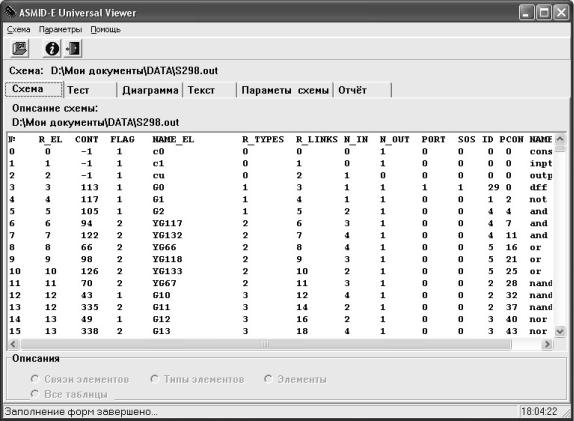

программ моделирования и генерации тестов, списки непроверенных неисправностей, число событий процесса моделирования и т.д.

Рис.9.9 Программа просмотра результатов работы

Для удобства отдельно реализована программа просмотра временных диаграмм (рис.9.6).

9.8 Экспериментальные результаты

Апробацию алгоритмов моделирования и генерации тестов по международным стандартам принято проводить на наборах стандартных схем ISCAS-85 и ISCAS-89. В табл.9.2 в качестве примера приведены результаты машинных экспериментов, проведённых с использованием системы АСМИД-Е. Для каждой схемы указаны основные характеристики:

число вентилей, число неисправностей в сжатом списке, число проверенных неисправностей, время генерации тестовых наборов

421

программой, реализующей генетический алгоритм, полнота полученных тестовых наборов и время моделирования схем с неисправностями в 3-х

значном алфавите.

Таблица 9.2

Имя |

Всего / |

Полнота / |

Время |

Время |

|

схемы |

проверилось |

усл.полнота |

генерации |

Моделирования |

|

|

неисправностей |

% |

мин.:сек. |

мин.:сек. |

|

|

|

|

|

|

|

C432 |

22 |

/ 22 |

99.24 / -//- |

0:35 |

0:00 |

|

|

|

|

|

|

C499 |

758 |

/ 750 |

98.94 / -//- |

0:33 |

0:00 |

|

|

|

|

|

|

C880 |

942 |

/ 942 |

100 / -//- |

0:56 |

0:00 |

|

|

|

|

|

|

C1355 |

1574 |

/ 1564 |

99.36 / -//- |

1:09 |

0:01 |

|

|

|

|

|

|

C1908 |

1879 |

/ 1864 |

99.20 / -//- |

2:21 |

0:02 |

|

|

|

|

|

|

C2670 |

2899 |

/ 2165 |

74.68 / -//- |

4:07 |

0:05 |

|

|

|

|

|

|

C3540 |

3428 |

/ 3274 |

95.51 / -//- |

2:37 |

0:07 |

|

|

|

|

|

|

C5315 |

5350 |

/ 5291 |

98.90 / -//- |

2:34 |

0:09 |

|

|

|

|

|

|

C7552 |

7552 |

/ 6975 |

92.37 / -//- |

6:04 |

0:30 |

|

|

|

|

|

|

S298 |

308 |

/ 254 |

82.79 / 85.39 |

3:14 |

0:02 |

|

|

|

|

|

|

S344 |

342 |

/ 323 |

96.20 / 97.95 |

2:15 |

0:02 |

|

|

|

|

|

|

S349 |

350 |

/ 329 |

95.71 / 97.43 |

0:46 |

0:02 |

|

|

|

|

|

|

S386 |

384 |

/ 263 |

68.49 / 68.49 |

2:31 |

0:04 |

|

|

|

|

|

|

S641 |

467 |

/ 404 |

86.30 / 87.79 |

2:20 |

0:04 |

|

|

|

|

|

|

S713 |

581 |

/ 469 |

80.38 / 81.76 |

1:57 |

0:05 |

|

|

|

|

|

|

S1196 |

1242 |

/ 1148 |

96.38 / 96.38 |

1:54 |

0:15 |

|

|

|

|

|

|

S1238 |

1355 |

/ 1206 |

90.18 / 90.18 |

3:54 |

0:21 |

|

|

|

|

|

|

S1488 |

1486 |

/ 1047 |

70.46 / 70.59 |

9:33 |

0:35 |

|

|

|

|

|

|

S1494 |

1506 |

/ 1063 |

70.58 / 71.18 |

9:31 |

0:31 |

|

|

|

|

|

|

S3271 |

3270 |

/ 3204 |

97.98 / 97.98 |

8:29 |

0:28 |

|

|

|

|

|

|

Длина

теста

53

53

70

85

132

66

150

127

150

637

192

295

606

727

677

1642

1183

1975

1712

1125

Таким образом, можно сделать следующие основные выводы:

− Применение новых методов моделирования неисправных схем

существенно улучшает эксплуатационные характеристики системы

422

моделирования АСМИД-Е: повышается скорость и адекватность процесса

моделирования, а также процесса генерации тестов.

−Применение генетического алгоритма для построения тестовых наборов как стратегии, основанной на моделировании, позволяет добиться высокой полноты генерируемых наборов, которая сравнима с результатами детерминированного подхода. Однако при этом генетический алгоритм обладает преимуществами прозрачности стратегии и простоты реализации.

−Использование единой системы математических моделей на основе универсального 16-значного алфавита и унифицированных моделей многозначных функций позволяет наращивать функциональные возможности системы путём разработки новых методов моделирования и генерации тестов.

−Программная совместимость с распространённой системой PCAD

позволяет встраивать АСМИД-Е в интегрированные САПР ЦУ.

− Унифицированный подход к построению моделей логических

устройств позволяет легко пополнять библиотеку элементов, в том числе

элементами высокой степени интеграции.

423

СПИСОК ЛИТЕРАТУРЫ

1.Барашко А.С., Скобцов Ю.А., Сперанский Д.В. Моделирование и тестирование дискретных устройств. – Киев: Наукова думка, 1992. – 288с.

2.Богомолов А.М., Сперанский Д.В. Аналитические методы в задачах

контроля и анализа дискретных устройств. – Саратов: Изд-во Саратов.

ун-та, 1986. – 240с.

3.Скобцов Ю.А. Модели операторов языков регистровых передач для различных методов кодирования троичного алфавита // Автоматика и вычислительная техника. – 1988. – №1. – С.79-86.

4.Скобцов Ю.А. Многозначные алфавиты в моделировании и построении тестов цифровых устройств // Электронное моделирование.

–1989. – №3. – С.54-60.

5.Скобцов Ю.А., Шатохин П.А. Троичные модели операторов языков

регистровых передач // Автоматика и телемеханика. – 1988. – №2. –

С.160-172.

6.Скобцов Ю.А. Многозначные модели цифровых устройств логического и функционального уровня // Автоматика и вычислительная техника. – 1995. – №4. – С.42-52.

7.Скобцов В.Ю., Скобцов Ю.А. Применение символьного моделирования при построении характеристических последовательностей // Искусственный интеллект. – 2000. – №1. – С.6572.

8.Скобцов Ю.А. Моделирование неисправностей в многозначных алфавитах// Труды Ин-та прикладной матем. и механики.

Идентификация и моделирование управл. систем. – 1997. – Т.1. – С.50-

59.

9. Скобцов Ю.А. Дифференциальный метод моделирования неисправностей для синхронных последовательностных схем //

424

Техническая диагностика и неразрушающий контроль. – 1996. – №3. –

С.51-56.

10.Скобцов Ю.А. Моделирование неисправностей типа “задержка распространения сигналов” // Техническая диагностика и неразрушающий контроль. – 1997. – №3. – С.30-34.

11.Скобцов Ю.А., Иванов Д.Е. Параллельное моделирование константных и функциональных неисправностей в многозначных алфавитах // Техническая диагностика и неразрушающий контроль. – 1998. – №3. – С.35-41.

12.Скобцов Ю.А., Иванов Д.Е. Параллельное моделирование неисправностей для последовательностных схем // Искусственный интеллект. – 1999. – №1. – С.44-50.

13.Скобцов Ю.А. Применение булевых дифференциальных операторов при построении проверяющих последовательностей // Автоматика и телемеханика. – №9. – 1979. – С.136-148

14.Скобцов Ю.А., Копытова О.М., Задорожная Л.В. Генерация тестов для комбинационных и последовательностных схем методом критических путей // Сб. научн. тр. Теория и моделирование управляющих систем. –

Киев: Наукова думка, 1989. – С.65-75.

15. Скобцов Ю.А. Построение тестов в многозначных алфавитах //

Сб.научн.тр. Моделирование и диагностика управляющих систем. –

Киев: Наукова думка, 1991. – С.96-102.

16.Скобцов Ю.А. Построение тестов для последовательностных дискретных устройств // Межвуз. науч сб. Методы и системы технической диагностики. – Вып.18. – Саратов: Из-во СГУ,1993. – с.5559.

17.Скобцов Ю.А. Построение тестов для последовательностных цифровых схем в 16-значном алфавите // Электронное моделирование. – 1997. – №1. – С.50-58.

18.Скобцов В.Ю., Скобцов Ю.А. Генерация проверяющих тестов для последовательностных цифровых устройств на основе символьного

425

моделирования неисправностей // Автоматика и вычислительная

техника. – 1999. – №4. – С.73-84.

19.Скобцов Ю.А. Скобцов В.Ю. Единый подход к построению идентифицирующих последовательностей для цифровых устройств с памятью // Наукові праці Донецького державного технічного університету. Серія: Обчислювальна техніка та автоматизація. – Вип.12.

– Донецьк, 1999. – С.136-142.

20.Skobtsov V.Y., Skobtsov Y.A. Test generation for sequential digital systems based on symbolic simulation // Proceedings of the 6th Biennial Baltic Electronics Conference. Tallinn, Estonia. – 1998. – P.341-344.

21.Скобцов В.Ю. Символьное моделирование неисправностей последовательностных цифровых устройств // Автоматика и вычислительная техника. – 1997. – №5. – С.40-50.

22.Скобцов В.Ю. Символьно-аналитический метод генерации проверяющих тестов для последовательностных цифровых устройств //

Техническая диагностика и неразрушающий контроль. – 1997. – №3. –

С.22-29.

23.Скобцов В.Ю., Cадымак Р.И. Структурный подход к тестированию функциональных неисправностей в дискретных устройствах // Труды института прикладной математики и механики. – 1999. – №4. – С.149156.

24.Иванов Д.Е., Скобцов Ю.А. Генерация тестов цифровых устройств с использованием генетических алгоритмов // Труды института прикладной математики и механики НАН Украины.Т.4. Донецк ИПММ - 1999. – С.82-88.

25.Скобцов Ю.А. Применение генетических алгоритмов в интеллектуальных САПР // Наукові праці Донецького Державного технічного університету. Серія: Обчислювальна техніка та автоматизація. – Вип.25. – Донецьк, 2001. – С.101-109.

26.Скобцов Ю.О., Закусило С.А., Іванов Д.Є. Адаптивні механізми в генетичних алгоритмах // Наукові праці Донецького Державного

426

технічного університету. Серія: Обчислювальна техніка та

автоматизація. – Вип. 38. – Донецьк, 2002. – С.104-109.

27.Скобцов Ю.А., Іванов Д.Е., Скобцов В.Ю. Генетические алгоритмы в диагностике и проектировании цифровых схем // Искусственный интеллект. – №2. – 2002. – С.250-258.

28.Skobtsov Y.A., Ivanov D.E., Skobtsov V.Y. Genetic algorithms in test generation for digital circuits // Proceedings of the 8th Biennial Baltic Electronics Conference. Tallinn, Estonia. – 2002. – P.291-294.

29.Скобцов Ю.А., Ермоленко М.Л. Эволюционный подход к тестированию микропроцессорных систем // Наукові праці Донецького державного технічного університету. Серія: Обчислювальна техніка та автоматизація. – Вип.64. – Донецьк, 2003. – С.241-247.

30.Закусило С.А., Иванов Д.Е., Скобцов В.Ю., Скобцов Ю.А.

Эволюционный подход к генерации проверяющих тестов цифровых

систем // Труды конференций "Интеллектуальные системы" и

"Интеллектуальные САПР". – Москва:Физматлит, 2003. – С.76-81.

31.Skobtsov Y.A., Ivanov D.E., Skobtsov V.Y. Evolutionary approach to the test pattern generation for the sequential circuits // Радиоэлектроника и информатика. – 2003. – №3. – С.46-51.

32.Скобцов Ю.А., Скобцов В.Ю. Эволюционный подход к построению тестов цифровых систем // Труды I Всероссийской научной конференции ”Методы и средства обработки информации”. –

Москва:Физматлит, 2003. – С.142-147.

33.Иванов Д.Е., Скобцов В.Ю. Сжатие списка неисправностей с помощью генетического алгоритма // Наукові праці Донецького державного технічного університету. Серія: Обчислювальна техніка та автоматизація. – Вип.25. – Донецьк, 2001. – С.161-167.

34.Иванов Д.Е., Скобцов Ю.А. Ускорение работы генетических алгоритмов при построении тестов // Искусственный интеллект. – 2001.

– №1. – C.52-60.

427

35.Скобцов Ю.А., Скобцов В.Ю. Система логического моделирования и генерации тестов АСМИД-П // Управляющие системы и машины. – 1996. – №1,2. – С.39-45.

36.Иванов Д.Е., Скобцов Ю.А. Система моделирования и генерации тестов цифровых схем // Наукові праці Донецького державного технічного університету. Серія: Обчислювальна техніка та автоматизація. – Вип.12. – Донецьк,1999. – С.143-150.

37.Скобцов Ю.О., Іванов Д.Є., Скобцов В.Ю. Генерація тестів та логічне моделювання цифрових схем в системі АСМІД-Е // Вісник Технологічного університету Поділля. – 2002. – Т.1. – С125-128.

38.Закусило С.А., Иванов Д.Е., Скобцов В.Ю., Скобцов Ю.А.

Генетический подход к генерации проверяющих тестов в системе

АСМИД-Е // Труды международных конференций "Искусственный

интеллект" и "Интеллектуальные САПР" (IEEE AIS'02 CAD-2002). –

Москва: Физматлит, 2002. – С.49-55

39.Mourad S., Zorian Y. Principles of testing electronic systems. – John Wiley&Sons,2000. – 420p.

40.Яблонский С.В. Введение в дискретную математику. – М.:Наука,1979.

41.Lee C. Representation of switching circuits by binary decision diagrams // Bell system technical journal. – 1959. – Vol.38, N6. – P.985-999.

42.Akers S.B. Binary decision diagrams // IEEE Trans. on computers. –1978.

– Vol.C-17, N6. – P.509-516.

43.Плакк М.П., Убар Р.Р. Построение тестов цифровых схем при помощи модели альтернативных графов // Автоматика и телемеханика, 1980,N5,с.152-163.

44.Abramovici M. Digital System Testing and Testable Design. – New York: Computer Science Press, 1990. – 652p.

45.Brglez F., Bryan D., Kozminski K. Combinatorial Problems of Sequential Benchmark Circuits // Proc. IEEE Int. Symp.Circuits and Systems. – Los Alamitos, Calif.:IEEE Computer Soc. Press.,1989. – P.1929-1934.

428

46.Бибило П.Н. Синтез логических схем с использованием языка VHDL.

–М.: СОЛОН-Рб, 2002. – 384 с.

47.Автоматизированное проектирование цифровых устройств / Под. ред.

С.С.Бадулина. – М.:Радио и связь,1981. – 240 с.

48.Малышенко Ю.В., Чипулис В.П., Шаршунов С.Г. Автоматизация диагностирования электронных устройств. – М.:Энергоатомиздат, 1986.

–240 с.

49.Bushnell M.L., Agrawal V.D. Essentials of electronic testing for digital, memory and mixed-signal VLSI circuits. – Kluwer academic publishers, 2001. – 690 p.

50.Eihelberger E.B. Hazard detection in combinational and sequential switching circuits // IBM J. Res. and Develop. – 1965. – Vol.9, N2. – P.90-99.

51.Hays Y.P. A systematic approach to multivalued digital simulation // Proc. Int. Conf. Comput. Design. – 1984. – P.177-182.

52.Akers S.B. A logic system for fault test generation // IEEE Trans. on Comp.

–1976. – N6. – P.620-630.

53.Hayes J.P. Pseudo-boolean logic circuits // IEEE Trans. On Comput. – 1986. – C.35, N7. – P.602-612.

54.Зеленевская Е.Л., Пимахов С.Г., Темченко В.А. Подход к логико-

функциональному моделированию МДП-СБИС // Управляющие

системы и машины. – 1985. – №6. – С.59-62.

55. Вейцман И.Н., Кондратьева О.М. Тестирование КМОП-схем //

Автоматика и телемеханика. – 1991. – №2. – с.3-34.

56.Harris I.G. Fault models and test generation for hardware-software covalidation // IEEE Design and Test of computers. – 2003. – Vol.20,N.4. – P.40-47.

57.Beizer B. Software testing techniques. New York :Van Nostrand Rheinhold, second edition , 1990.

58.Tasiran S., Keutzer K. Coverage metrics for functional validation of hardware designs // IEEE Design and Test of computers. – 2001. – Vol.18, N.4. – P.36-45.

429

59.King K.N., Offutt A.J. Fortran language system for mutation-based software testing // Software practice and eng. – 1991. – Vol.21, N.7. – P.685718.

60.Hayek G.AI., Robach C. From specification validation to hardware testing: a unified message // Proc. Int. Test Conf. (ITC 96). IEEE Press, 1996. – P.885-893.

61.Devadas S., Ghosh A., Keutzer K. An observability-based code coverage metric for functional simulation // In Proc. of the Int. conference on computer-aided design. – November, 1996. – P.418-425.

62.F.Ferrandi, G.Ferrara, D.Sciuto. Functional Test Generation for behaviorally sequential models // Proc. IEEE Design Automation and Test in Europe Conference (DATE). – 2001. – P.403-410.

63.Paoli C., Nivet M.-L., Santucci J.-F. Use of constraint solving in order to generate test vectors for behavioral validation // Proc. IEEE Int. High Level Design Validation and Test Workshop. – IEEE CS Press, 2000. – P.15-20.

64.Богомолов А.M., Барашко А.С., Грунский И.С. Эксперименты с автоматами. – Киев: Наук. думка, 1973. – 144 с.

65.Geist D. et al. Coverage-Directed Test Generation Using Symbolic Techniques // Proc. 1st Int. Conf. Formal Methods in Computer-Aided Design (FMCAD’96). – Springer. Lecture Notes in Computer Science. – Vol.1166, 1996. – P.143-158.

66.Ho R.C. et al. Architecture Validation for Processors // Proc. 22nd Ann. Int. Symp. Computer Architecture (ISCA 95). – ACM Press,1995. – P.404-413.

67.Lee D., Yannakakis M. Principles and Methods of Testing Finite State Machines – A Survey // IEEE Trans. Computers. – 1996. – Vol.84, N8. – P.1090-1123.

68.Грунский И.С. Анализ поведения конечных автоматов. – Луганск:

ЛНПУ, ИПММ. – 2003. – 210 с.

69. Thatte S.M., Abraham J.A. Test generation for microprocessors // IEEE Trans. Computers. – 1980. – Vol.C-29, N6. – P.429-441.

430