- •ПРЕДИСЛОВИЕ

- •1. КЛАССИФИКАЦИЯ И ФУНКЦИОНАЛЬНОЕ НАЗНАЧЕНИЕ СОВРЕМЕННЫХ ИЗДЕЛИЙ МИКРОЭЛЕКТРОНИКИ

- •1.1. Полупроводники

- •1.2. Электронно-дырочной переход (p-n переход)

- •1.3. Полупроводниковые диоды

- •1.4. Биполярные транзисторы

- •1.5. Полевые транзисторы

- •1.6. Элементы интегральных схем

- •1.7. Силовые полупроводниковые приборы

- •2. АНАЛОГОВЫЕ ЭЛЕКТРОННЫЕ УСТРОЙСТВА — УСИЛИТЕЛИ СИГНАЛОВ

- •2.1. Основные параметры и характеристики

- •2.2. Усилители на биполярных транзисторах

- •2.3. Усилители на полевых транзисторах

- •2.4. Усилители с обратной связью

- •2.5. Усилители мощности

- •2.6. Усилители постоянного тока

- •2.7. Дифференциальные усилители

- •2.8. Операционные усилители

- •3. ОСНОВЫ ЦИФРОВОЙ ЭЛЕКТРОНИКИ

- •3.1. Сигналы цифровых устройств

- •3.2. Алгебра логики

- •3.3. Транзисторные ключи

- •3.3.1. Ключи на биполярных транзисторах

- •3.3.2. МДП-транзисторные ключи

- •3.4. Логические интегральные микросхемы

- •3.4.1. Общие сведения

- •3.4.2. Базовые элементы логических интегральных микросхем

- •3.5. Комбинационные устройства

- •3.5.1. Дешифраторы и шифраторы

- •3.5.2. Распределители и коммутаторы

- •3.5.3. Цифровой компаратор

- •3.6. Последовательностные устройства

- •3.6.1. Триггеры. Общие сведения

- •3.6.2. Транзисторные триггеры

- •3.6.3. Интегральные триггеры

- •3.6.4. Счетчики

- •3.6.5. Регистры

- •3.7. Полупроводниковые запоминающие устройства

- •4. ГЕНЕРАТОРЫ И ФОРМИРОВАТЕЛИ СИГНАЛОВ

- •4.1. Генераторы синусоидальных колебаний

- •4.1.1. Генераторы LC-типа (LC-генераторы)

- •4.1.2. Кварцевые генераторы

- •4.1.3. Генераторы RC-типа (RC-генераторы)

- •4.2. Генераторы прямоугольных импульсов

- •4.3. Генераторы линейно изменяющегося напряжения и тока

- •5. УСТРОЙСТВА И ЭЛЕМЕНТЫ АВТОМАТИКИ

- •5.2. Датчики различной физической природы

- •5.3. Аналоговые компараторы

- •5.4. Устройства сопряжения микропроцессорных систем с объектами

- •5.4.1. Аналого-цифровые преобразователи

- •5.4.2. Цифро-аналоговые преобразователи

- •5.5. Релейные схемы

- •5.5.1. Электромагнитные контактные реле. Общие сведения и основные параметры

- •5.5.2. Электронные реле

- •5.5.3. Фотоэлектронные реле

- •5.5.4. Электронные реле на тиристорах

- •5.6. Магнитные усилители, их назначение и классификация

- •5.7. Микропроцессоры

- •6. ИСТОЧНИКИ ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ

- •6.1. Выпрямители

- •6.1.1. Определение и параметры выпрямителя

- •6.1.2. Схемы выпрямителей

- •6.2. Сглаживающие фильтры

- •6.2.1. Активные фильтры на транзисторах

- •6.2.2. Активные фильтры на операционных усилителях

- •6.3. Стабилизаторы напряжения

- •6.3.1. Виды стабилизаторов и основные характеристики

- •6.3.2. Параметрические стабилизаторы напряжения

- •6.3.3. Стабилитронные интегральные микросхемы (СИМС)

- •6.4. Компенсационные стабилизаторы напряжения

- •6.4.1. Компенсационные стабилизаторы напряжения на транзисторах

- •6.5. Импульсные источники питания

- •6.5.1. Виды и особенности импульсных источников питания

- •6.5.2. Импульсные стабилизаторы напряжения

- •ПРИЛОЖЕНИЕ

- •СПИСОК РЕКОМЕНДУЕМОЙ ЛИТЕРАТУРЫ

- •СОДЕРЖАНИЕ

кий сигнал, значение которого определено номером выхода дешифратора, подается на шифратор, и на его выходах устанавливается преобразованный код.

Примером использования шифраторов являются такжеустройства ввода двоичных кодов в цифровое устройство с клавиатуры. При нажатии клавиши на определенной входной шине шифратора появляется логическая 1 (шина возбуждается) и на выходах устанавливается двоичный код, соответствующий нанесенному на клавишу знаку (букве, цифреит.д.).

3.5.2. Распределители и коммутаторы

Распределители. Узел, последовательно распределяющий по выходамсигналы, поступающиенаеговход, называютраспределителем.

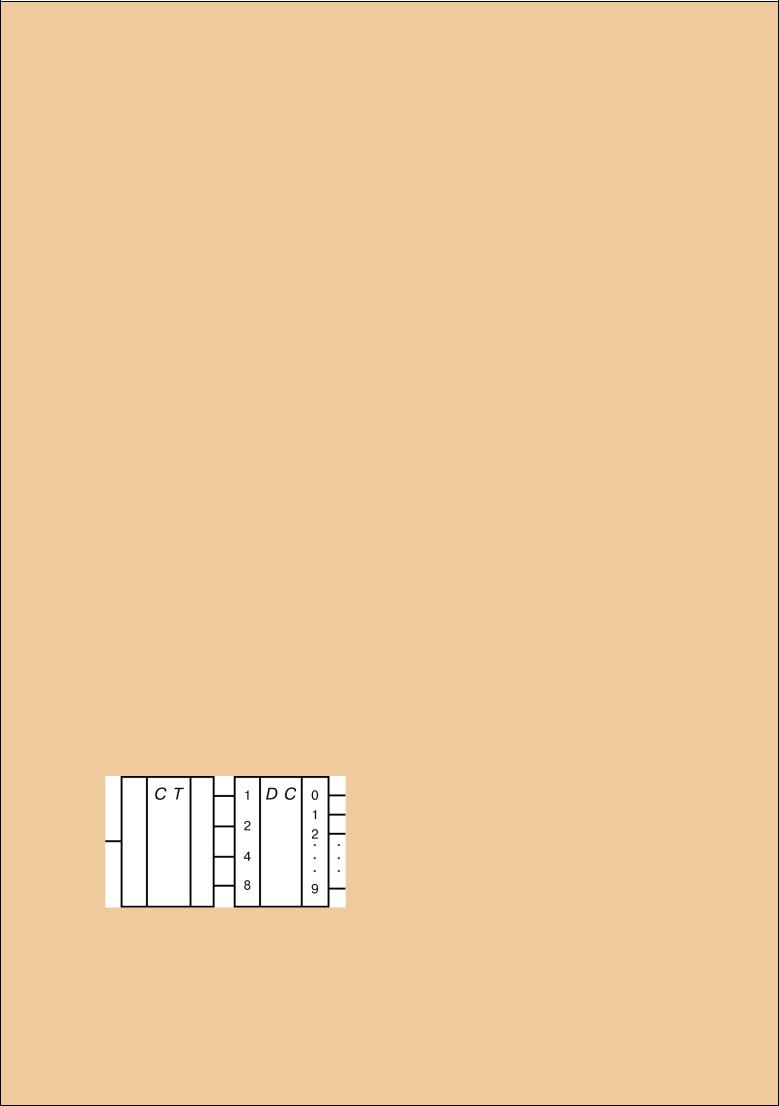

На рис. 3.25 приведена функциональная схема распределителя, содержащая счетчик и дешифратор. Каждый импульс на входе счетчика увеличивает на единицу зафиксированное в нем число. Благодаря этому логическая 1 поочередно появляется на выходах дешифратора.

Распределители применяются при решении различных задач. В частности, сигналами с выходов распределителя можно осуществлять поочередное включение и отключение устройств, получать выборки сигнала через равные промежутки времени. В последнем случае выборки формируются с помощью ключа, управляемого логической 1 с одного из выходов распределителя и на время ее действия подключает источник сигнала к линии.

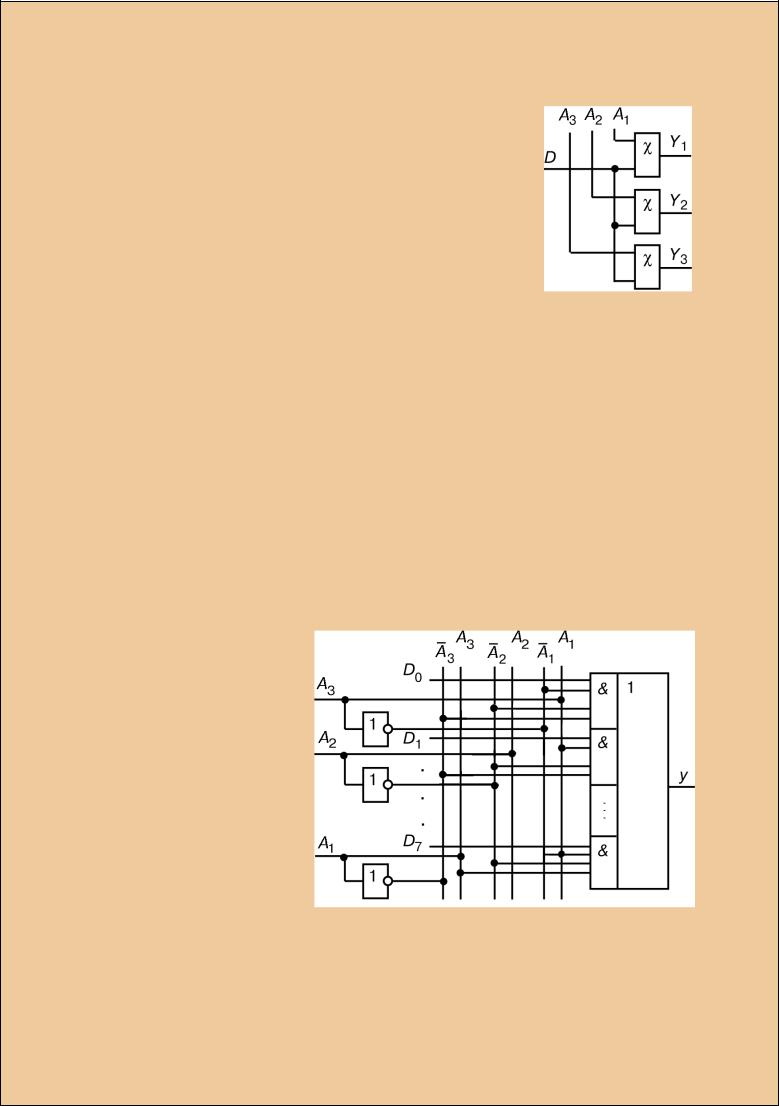

Коммутаторы. Коммутатор — устройство, осуществляющее переключение цепей. На рис. 3.26 изображена схема коммутатора, позволяющего подключить источник цифровой информации D к

разным каналам (y1, y2, y3). Информация будет поступать в тот канал,

на элемент И которого подается разрешение в виде логической 1 с одного из адресных входов А1, А2, А3. Рассмотренный коммутатор выполнен на одной микросхеме, содер-

Рис. 3.25. Функциональная жащей в корпусе три элемента И.

схема распределителя

138

Коммутатор (рис. 3.26) позволяет подклю- |

|

чать канал y к разным источникам информации |

|

(D1, D2, D3). Выбор присоединяемого источника |

|

(входа коммутатора) осуществляется подобно |

|

выбору канала в предыдущей схеме. |

|

Задачу, аналогичную той, которую решает |

|

коммутатор (рис. 3.26), выполняет мультиплек- |

|

сор-коммутатор, в котором выбор входа по его |

|

номеру (адресу) осуществляется с помощью циф- |

|

рового сигнала (цифрового кода). |

Рис. 3.26. Схемапро- |

На рис. 3.27 приведена функциональная схе- |

стого коммутатора |

ма мультиплексора. Он содержит конъюнктуры, |

|

к которым подходят информационные шины, и дизъюнктор. Данный мультиплексор имеет восемь информационных (D0...D7) и три адресных (А1...А3) входа. На адресные входы поступает трехэлементный цифровой код, полное число комбинаций которого равно 23, т.е. восьми. Естественно предположить, что код 111 должен обеспечить соединение выхода y со входом D7 (1112 = 710), код 110 — со входом D6 (1102 = 610) и т.д., код 000 — со входом D0.

Так же, как в схеме рис. 3.26, каждый вход подключается к выходу через определенный конъюнктор. Однако в данном случае коммутация осуществляется при наличии на конъюнкторе трех разрешающих логических единиц (с трех адресных входов). Для их получения нужно входы соответствующего конъюнктора соединить непосредственно с теми адресными входами, на которых при данном коде присутствуют единицы, и через инверторы— стемивходами, на которых находятся нули. Такие соединения выполнены в схеме (рис. 3.26).

Так, на второй сверху Рис. 3.27. Схема коммутатора-мультиплексора

139

конъюнктор непосредственно поступает сигнал с входа A1 и через инверторы — с входов A2 и A3 , что при коде адреса 001 обеспечит на этом конъюнкторе три логические1, т.е. подключениеквыходумультиплексора входа D1. Входы нижнего конъюнктора соединены с адресными входами непосредственно, что при коде адреса 111 обеспечит подключение к выходу мультиплексораинформационноговходаD7 .

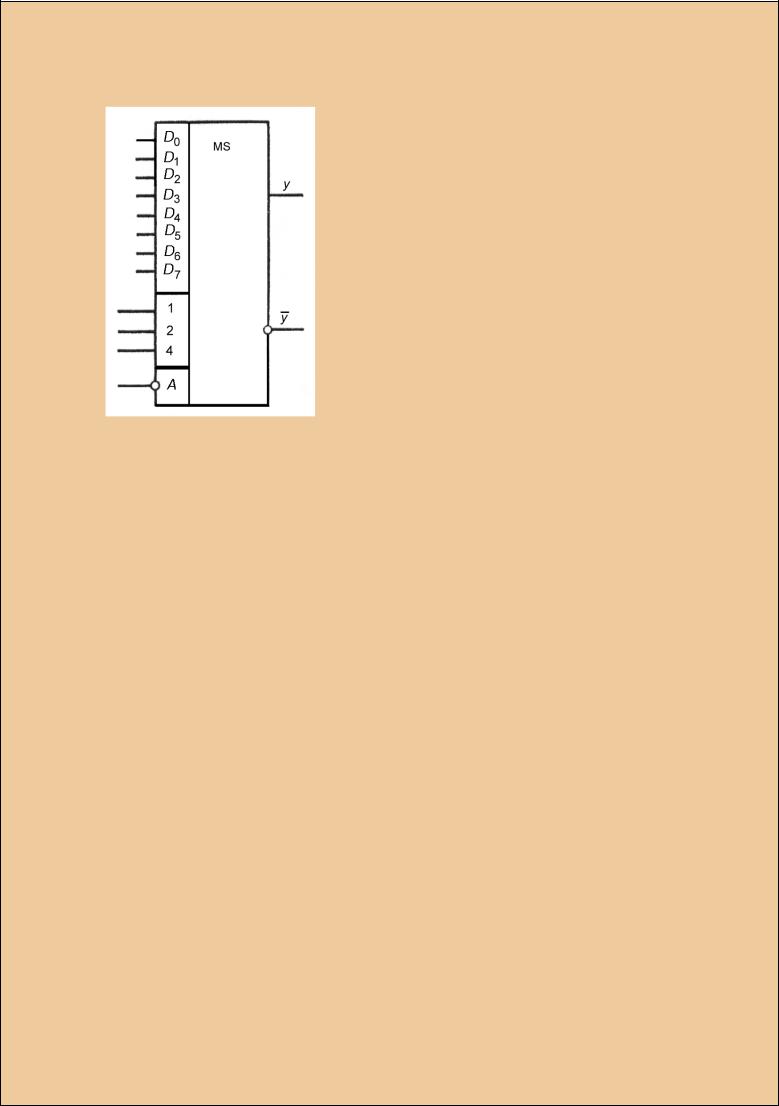

Отечественная промышленность выпускает несколько типов микросхемных мультиплексоров. На рис. 3.28 показано условное изображение мультиплексора

Рис. 3.28. Условное изоб- (микросхема серии К155), имеющего во- ражение мультиплексора семь информационных входов, три ад-

ресных входа для кода с весами 4, 2, 1, вход стробирования А и два выхода — прямой и инверсный. При наличии на входе А логической 1 мультиплексор блокируется: на прямом выходе устанавливается логический 0 вне зависимости от потенциалов на информационных входах. Наличие входа стробирования позволяет увеличивать число коммутируемых информационных входов.

3.5.3. Цифровой компаратор

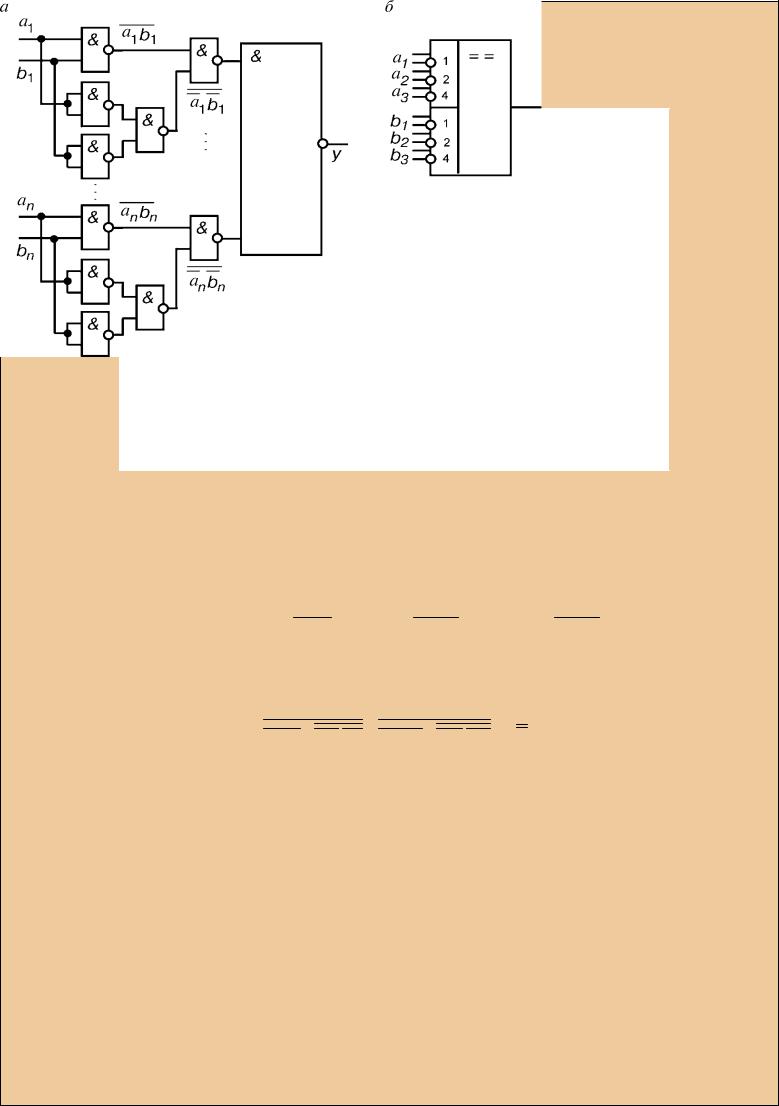

Цифровой компаратор предназначен для определения равенства двоичных чисел.

Два числа равны при равенстве цифр в одноименных разрядах (аi = bi , где аi — цифра в i-м разряде одного числа; bi — цифра в том же разряде другого числа).

Равенство аi = bi имеет место при аi = 1, bi = 1 или при аi = 0, bi = 0. Поэтому логическая функция, выражающая это равенство, равна единице, если единице равно произведение этих цифр или произведение их инверсных значений: y = aibi + aibi . Заметим, что записанная функция — функция «Равнозначность».

Так как числа равны при равенстве цифр в первых, во вторых разрядах и в n-х разрядах, то логическая функция, выражающая ра-

140

Рис. 3.29. Схема (а) и условное изображение (б) цифрового компаратора

венство двух чисел — логическая функция, описывающая компаратор, имеет вид:

y = (a1b1 + а1b1 )(a2b2 + а2b2 )...(anbn + аnbn ).

Чтобы построить компаратор только на элементах И—НЕ, запишем ее в другой форме, используя теорему де Моргана:

a1b1 а1 b1 ...anbn a n bn = y,

–

где отрицание левой части (при изменении в правой части y на у) сделано для той же цели.

Схема, реализующая это выражение, приведена на рис. 3.29, а. Если необходимо, чтобы при равенстве кодов на выходе компаратора была логическая 1, то к выходу схемы следует присоединить инвертор.

Условное изображение цифрового компаратора приведено на рис. 3.29, б.

141