- •ПРЕДИСЛОВИЕ

- •1. КЛАССИФИКАЦИЯ И ФУНКЦИОНАЛЬНОЕ НАЗНАЧЕНИЕ СОВРЕМЕННЫХ ИЗДЕЛИЙ МИКРОЭЛЕКТРОНИКИ

- •1.1. Полупроводники

- •1.2. Электронно-дырочной переход (p-n переход)

- •1.3. Полупроводниковые диоды

- •1.4. Биполярные транзисторы

- •1.5. Полевые транзисторы

- •1.6. Элементы интегральных схем

- •1.7. Силовые полупроводниковые приборы

- •2. АНАЛОГОВЫЕ ЭЛЕКТРОННЫЕ УСТРОЙСТВА — УСИЛИТЕЛИ СИГНАЛОВ

- •2.1. Основные параметры и характеристики

- •2.2. Усилители на биполярных транзисторах

- •2.3. Усилители на полевых транзисторах

- •2.4. Усилители с обратной связью

- •2.5. Усилители мощности

- •2.6. Усилители постоянного тока

- •2.7. Дифференциальные усилители

- •2.8. Операционные усилители

- •3. ОСНОВЫ ЦИФРОВОЙ ЭЛЕКТРОНИКИ

- •3.1. Сигналы цифровых устройств

- •3.2. Алгебра логики

- •3.3. Транзисторные ключи

- •3.3.1. Ключи на биполярных транзисторах

- •3.3.2. МДП-транзисторные ключи

- •3.4. Логические интегральные микросхемы

- •3.4.1. Общие сведения

- •3.4.2. Базовые элементы логических интегральных микросхем

- •3.5. Комбинационные устройства

- •3.5.1. Дешифраторы и шифраторы

- •3.5.2. Распределители и коммутаторы

- •3.5.3. Цифровой компаратор

- •3.6. Последовательностные устройства

- •3.6.1. Триггеры. Общие сведения

- •3.6.2. Транзисторные триггеры

- •3.6.3. Интегральные триггеры

- •3.6.4. Счетчики

- •3.6.5. Регистры

- •3.7. Полупроводниковые запоминающие устройства

- •4. ГЕНЕРАТОРЫ И ФОРМИРОВАТЕЛИ СИГНАЛОВ

- •4.1. Генераторы синусоидальных колебаний

- •4.1.1. Генераторы LC-типа (LC-генераторы)

- •4.1.2. Кварцевые генераторы

- •4.1.3. Генераторы RC-типа (RC-генераторы)

- •4.2. Генераторы прямоугольных импульсов

- •4.3. Генераторы линейно изменяющегося напряжения и тока

- •5. УСТРОЙСТВА И ЭЛЕМЕНТЫ АВТОМАТИКИ

- •5.2. Датчики различной физической природы

- •5.3. Аналоговые компараторы

- •5.4. Устройства сопряжения микропроцессорных систем с объектами

- •5.4.1. Аналого-цифровые преобразователи

- •5.4.2. Цифро-аналоговые преобразователи

- •5.5. Релейные схемы

- •5.5.1. Электромагнитные контактные реле. Общие сведения и основные параметры

- •5.5.2. Электронные реле

- •5.5.3. Фотоэлектронные реле

- •5.5.4. Электронные реле на тиристорах

- •5.6. Магнитные усилители, их назначение и классификация

- •5.7. Микропроцессоры

- •6. ИСТОЧНИКИ ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ

- •6.1. Выпрямители

- •6.1.1. Определение и параметры выпрямителя

- •6.1.2. Схемы выпрямителей

- •6.2. Сглаживающие фильтры

- •6.2.1. Активные фильтры на транзисторах

- •6.2.2. Активные фильтры на операционных усилителях

- •6.3. Стабилизаторы напряжения

- •6.3.1. Виды стабилизаторов и основные характеристики

- •6.3.2. Параметрические стабилизаторы напряжения

- •6.3.3. Стабилитронные интегральные микросхемы (СИМС)

- •6.4. Компенсационные стабилизаторы напряжения

- •6.4.1. Компенсационные стабилизаторы напряжения на транзисторах

- •6.5. Импульсные источники питания

- •6.5.1. Виды и особенности импульсных источников питания

- •6.5.2. Импульсные стабилизаторы напряжения

- •ПРИЛОЖЕНИЕ

- •СПИСОК РЕКОМЕНДУЕМОЙ ЛИТЕРАТУРЫ

- •СОДЕРЖАНИЕ

•выполняемая логическая функция определяется включением транзисторов нижнего этажа;

•полярность источника питания Е зависит от типа канала транзисторов нижнего этажа.

Напряжение питания выбирают из условия Е > U0n + U0p , где U0n — пороговое напряжение n-канального транзистора; U0p — пороговое напряжение р-канального транзистора.

Время переключения логических элементов на КМДП-транзис- торах определяется временем перезаряда выходной емкости Свых .

3.5.Комбинационные устройства

3.5.1.Дешифраторы и шифраторы

Дешифраторы. Каждому цифровому сигналу на входах дешифратора соответствуетлогическая1 (илилогический0) наопределенномвыходе.

Так, на одном выходе дешифратора появляется логическая 1, а на остальных — логические 0, когда на входных шинах устанавливается, к примеру, двоичный код десятичного числа «четыре»; логическая 1 на другом выходе и логические 0 на остальных появляются, когда на шинах присутствует двоичный код десятичного числа «пять» и т.д. Таким образом, дешифратор расшифровывает (дешифрирует) число, записанное в двоичном коде, представляя его логической 1 (логическим 0) на определенном выходе.

Число входов дешифратора равно количеству разрядов поступающих двоичных чисел, а число его выходов — полному количеству различных двоичных чисел этой разрядности. Так как каждый разряд двоичного кода принимает два значения, то полное количество n-разрядных комбинаций (n-разрядных двоичных чисел) равно 2n. Такое число выходов имеет любой полный дешифратор.

Рассмотримпринцип, заложенныйвосновепостроениядешифратора. Чтобы выяснить, является ли данное двоичное число ожидаемым, нужно инвертировать цифры в определенных разрядах данного числа (где в ожидаемом числе записаны нули), а затем перемножить цифры всех разрядов преобразованного таким образом числа. Если результатом перемножения будет единица, то данное число является ожидаемым. Если в результате указанных дей-

134

ствий появится нуль, это означает, что нули находятся не в тех или не только в тех разрядах, где они стоят в ожидаемом числе. Поэтому после инверсии цифр в определенных разрядах не все цифры преобразованного числа оказались единицами и их перемножение дало нуль. В соответствии с изложенным дешифратор можно построить на инверторах и конъюнкторах, выходы которых являются выходами дешифратора.

Чтобы на выходе данного конъюнктора появлялась логическая 1, когда на входных шинах присутствует определенный двоичный код, надо соответствующим образом соединить шины с входами конъюнктора. Легко понять, что одни входы конъюнктора должны соединяться непосредственно с теми шинами, на которых при данном коде присутствуют единицы; другие входы с оставшимися шинами должны быть соединены через инверторы.

Пусть на выходе определенного конъюнктора надо получить логическую единицу, если на входных шинах появится, к примеру, код 01011, представляемый совокупностью высоких и низких потенциалов. Если инвертировать потенциалы на шинах третьего и пятого разрядов и реализовать конъюнкцию инвертированных и неинвертированных потенциалов, то результатом будет 1. Очевидно, что если на входных шинах присутствует совокупность потенциалов, отличающаяся от предыдущей хотя бы в одном разряде, то результатом описанных действий будет 0.

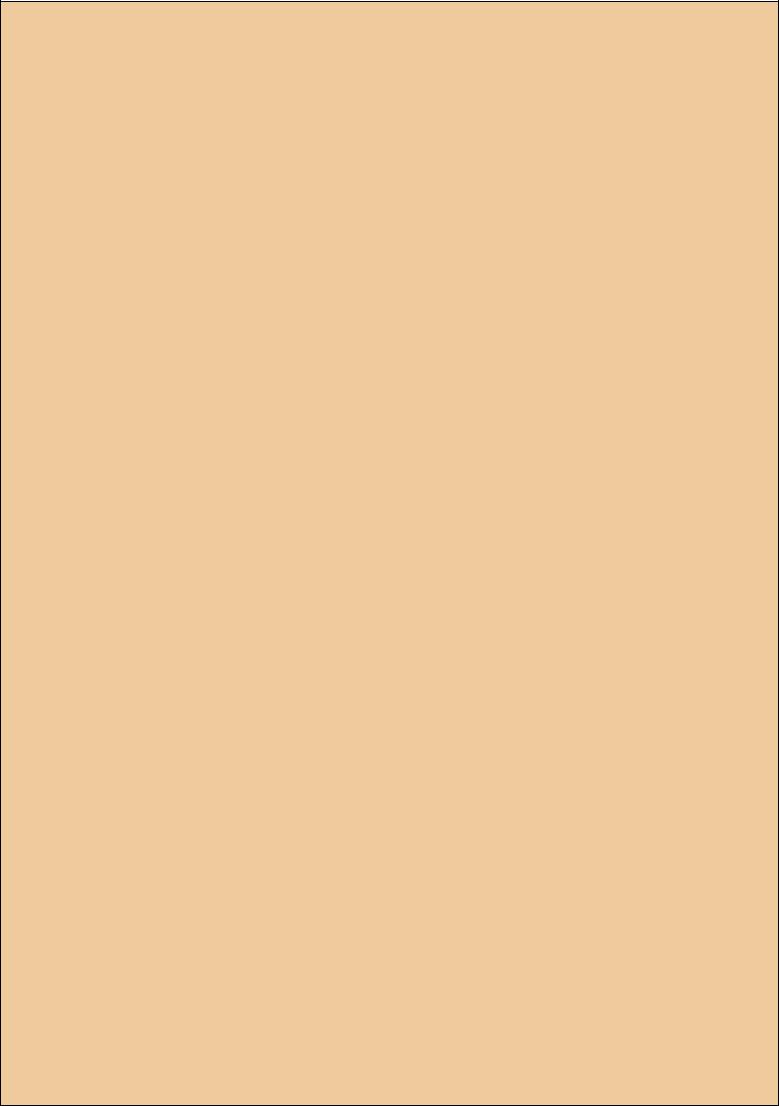

Изложенный принцип по- |

|

ложен в основу построения |

|

схемы на рис. 3.20. |

|

Логическая 1 на выходе y0 |

|

должна фиксировать присут- |

|

ствие на входных шинах х3, х2, |

|

x1 двоичного кода 000 деся- |

|

тичного числа 0; поэтому вхо- |

|

ды верхнего по схеме конъюн- |

|

ктора должны быть соедине- |

|

ны с шинами х3, х2, x1, на каж- |

|

дой из которых присутствует |

|

логическая 1, когда на вход- |

|

ныхшинахх3 = x2 = x1 = 0. Ло- |

Рис. 3.20. Линейный дешифратор |

гическая 1, к примеру, на вы- |

135

ходе y2 фиксирует появление на входных шинахх3, х2 , x1 кодадесятичногочисла2 (010); поэтому входы соответствующего конъюнктора должны быть соединены с

|

шинамих3 , х2 , x1 , накаждойизкоторых |

||

|

имеетсялогическая1, когдах3 = 0, х2 |

= 1, |

|

|

x1 |

= 0. Аналогично соединяются с шина- |

|

|

мивходыдругихконъюнкторов. |

|

|

|

|

Дешифратор (рис. 3.20) называется |

|

|

линейным (матричным, одноступен- |

||

|

чатым). В нем каждый конъюнктор |

||

|

получает информацию о всех n разря- |

||

|

дах кода, поэтому число его входов |

||

|

равно n (в данном случае — трем). |

|

|

|

|

На рис. 3.21 изображена схема пира- |

|

Рис. 3.21. Пирамидальный |

мидального дешифратора. Предпола- |

||

гается, что входные переменные x , x , |

|||

дешифратор |

x1 |

3 |

2 |

|

поступают на него в прямой и инвер- |

||

|

сной формах, благодаря чему схема де- |

||

шифратора не содержит инверторов. В рассматриваемом дешифра-

|

|

торе конъюнкции входных переменных образуют- |

|

|

|

ся постепенно. Вначале создаются всевозможные |

|

|

|

конъюнкции двух переменных х2, x1, затем — |

|

|

|

конъюнкции каждого из этих произведений и тре- |

|

|

|

тьей переменной х3, взятой в прямой и инверсной |

|

|

|

формах, и т.д. Из принципа построения пирами- |

|

|

|

дального дешифратора следует: в нем используют- |

|

|

|

ся двухвходовые конъюнкторы. Количество их на |

|

|

|

входе дешифратора равно четырем, следующее |

|

|

|

«сечение» имеет восемь конъюнкторов, а число их |

|

|

|

на выходе дешифратора такое же, как и в схеме |

|

|

|

рис. 3.20, т.е. в общем случае равно 2n. Каждый из |

|

|

|

выходов устройства, присоединенного к дешифра- |

|

Рис. 3.22. |

Схемо- |

тору, нагружен только двумя конъюнкторами. |

|

техническое изоб- |

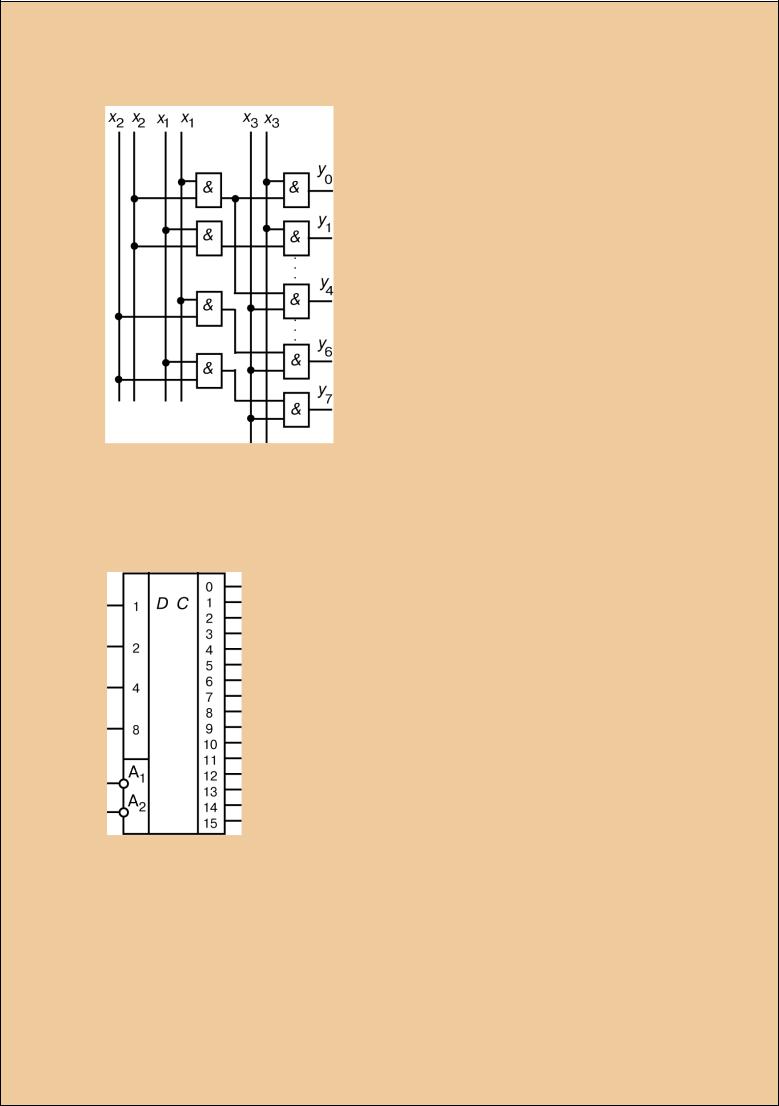

Условноеизображениедешифратораприведенона |

||

рис. 3.22. Вданномслучаеонимеетчетыреинформаци- |

|||

ражение дешифра- |

|||

тора в |

соответ- |

онныхвхода(накоторыепоступаютразрядывходного |

|

ствии с ЕСКД |

кодасвесами8, 4, 2, 1) ишестнадцатьвыходов. |

||

136

Дешифраторы широко используются в цифровой аппаратуре. Так, к одному из его выходов может быть подключено управляемое устройство, на которое будет поступать логический сигнал, когда на входах дешифратора установится определенный двоичный код.

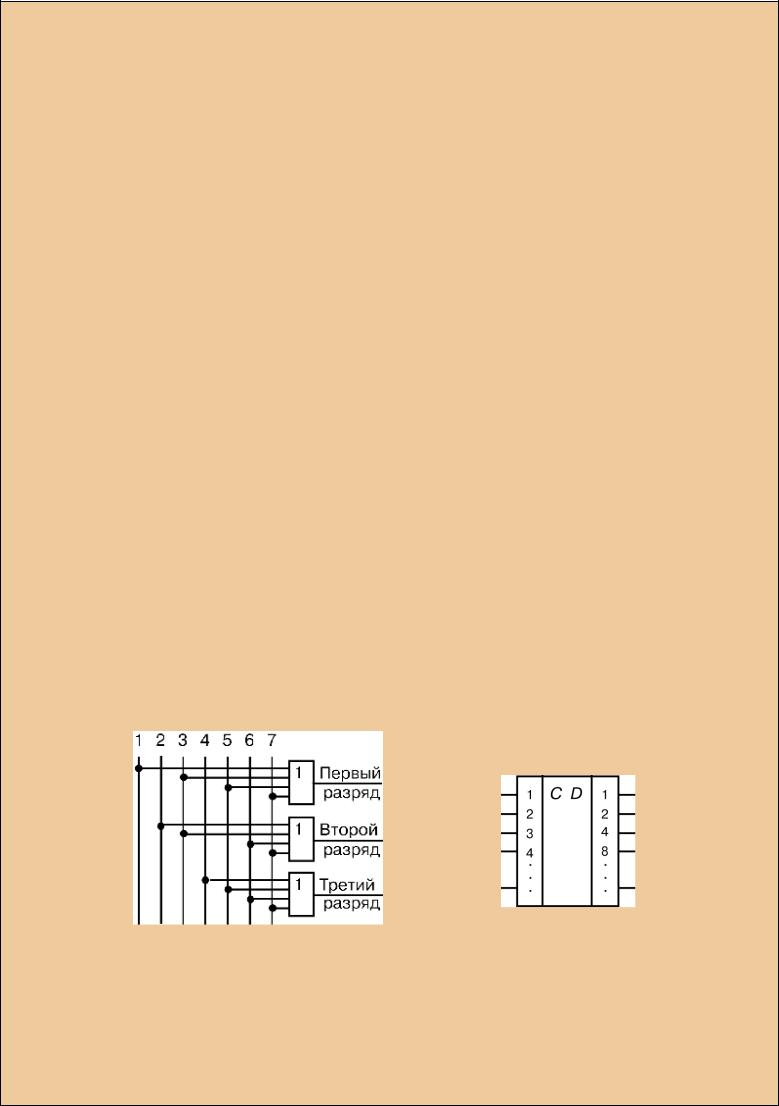

Шифраторы. Шифратор решает задачу, обратную дешифратору: на его выходных шинах устанавливается код, соответствующий номеру входа, на котором появилась логическая 1.

При построении шифратора для получения натурального двоичного кода учитывают, что единицу в младшем разряде такого кода имеют нечетные десятичные цифры 1, 3, 5, 7, т.е. на выходной шине младшего разряда должна быть 1, если она есть на входной шине № 1 или на входной шине № 3 и т.д. Поэтому входные шины под указанными номерами через элемент ИЛИ соединяются с выходной шиной младшего разряда.

Единицу во втором разряде двоичного кода имеют десятичные цифры 2, 3, 6, 7,...; шины с этими номерами через элемент ИЛИ должны подключаться к выходу шифратора, на котором устанавливается второйразрядкода. Аналогичношинысномерами4, 5, 6, 7, ... черезэлемент ИЛИ должны быть соединены с выходом, на котором устанавливается третийразряд, таккакихкодыимеютвэтомразрядеединицу, ит.д.

Схема шифратора, построенная в соответствии с изложенным принципом, изображена на рис. 3.23. Условное изображение шифратора приведено на рис. 3.24.

Шифраторы применяются в устройствах, преобразующих один вид кода в другой. При этом вначале дешифрируется каждая комбинация исходного кода, в результате чего на соответствующем выходе дешифратора появляется логическая 1. Затем этот логичес-

Рис. 3.23. Схема шифратора |

Рис. 3.24. Условное изобра- |

жение шифратора |

137