- •26. Арифметико-логічний пристрій.

- •27. Цифро-аналогові перетворювачі. Схеми з додаванням струмів.

- •29. Цифро-аналогові перетворювачі. Схема на матриці r-2r.

- •30. Аналого-цифрові перетворювачі паралельного типу.

- •31. Аналого-цифрові перетворювачі послідовного типу.

- •32. Аналого-цифрові перетворювачі послідовного наближення.

- •33. Послідовно-паралельні аналого-цифрові перетворювачі.

- •34. Σδ- та слідкуючі аналого-цифрові перетворювачі.

- •35. Статичні оперативні запам’ятовуючі пристрої.

- •36. Динамічні оперативні запам’ятовуючі пристрої.

- •37. Постійні запам’ятовуючі пристрої.

- •38. Генератори на базі логічних елементів.

- •39. Одновібратори.

- •40. Мультивібратори.

- •41. Пристрої вибірки-збереження.

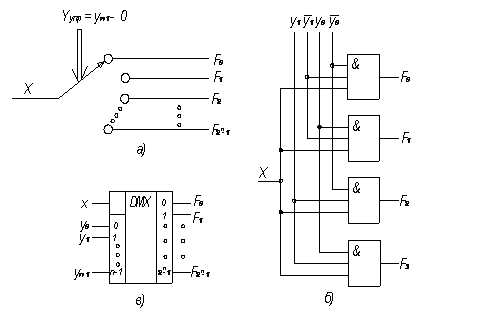

Питання № 22. Мультиплексор.

Мультиплексор – коммутатор логических сигналов, обеспечивающий передачу информации, поступающей по нескольким входным линиям связи, на одну выходную линию. Мультиплексор состоит из дешифратора адреса входной линии, схем И и схемы объединения ИЛИ.

В условных графических обозначениях функция мультиплексирования именуется MUX (от слова multiplexor).

Управление мультиплексором может производиться не только с помощью двоичного кода, но и кодом «1 из N». В этом случае число управляющих входов увеличивается становится равным числу информационных входов. Такой режим мультиплексора используется, в частности, в межразрядных цепях реверсивных счетчиков и регистров.

Мультиплексоры можно использовать для синтеза логических функций от нескольких переменных

Мультипле́ксоривідносяться до пристроїв комутування цифрової інформації. Вони здійснюють комутацію одного з декількох інформаційних входів xiдо одного виходуy. Мультиплексори мають декілька інформаційних входів, адресні входи, вхід дозволу мультиплексування (стробуючий вхід) та один вихід.

Адресний дешифратор D1, перетворює двійковий код у десятковий для керування роботою мультиплексора. В залежності від комбінації стану адресних входів а1та а2на одному з чотирьох виходів дешифратора з'являється одиничний потенціал, який дає дозвіл на спрацьовування відповідної схеми І (D2…D5).

Функціонування мультиплексора описується таблицею істинності

|

Адресні входи |

Керуючий вхід E |

Вихід y | |

|

а1 |

а2 |

|

|

|

X 0 1 0 1 |

X 0 0 1 1 |

0 1 1 1 1 |

0 x0 x1 x2 x3 |

Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства.

Сигналы на адресныхвходах определяют,

какой конкретно информационный канал

подключен к выходу. Если между числом

информационных входов![]() и

числом адресных входов

и

числом адресных входов![]() действует

соотношение

действует

соотношение![]() ,

то такой мультиплексор называют полным.

Если

,

то такой мультиплексор называют полным.

Если![]() ,

то мультиплексор называют неполным.

,

то мультиплексор называют неполным.

Разрешающиевходы используют для расширения функциональных возможностей мультиплексора. Они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов.

Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах, сдвигающих устройствах и др. Мультиплексоры могут использоваться для преобразования параллельного двоичного кода в последовательный.

Его назначение – передавать по одному широкополостному и скоростному каналу некоторое количество потоков различной скорости. На выручку приходит мультиплексирование. Мультиплексирование делается с помощью разделения потоков разными способами. Это разделение на частотные полосы.Потоки можно направить в разных временных;и способ кодирования. Мультиплексоры разделяют по месту применения, на терминальные и устройство ввода-вывода.

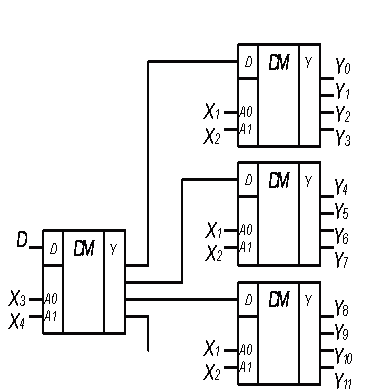

Питання № 23. Демультиплексори.

Демультиплексор відноситься до пристроїв комутування цифрової інформації. Він здійснює комутацію одного інформаційного входу до одного з декількох виходів, адреса якого задана. Демультиплексор має один інформаційний вхід, декілька виходів та адресні входи.

На приймальному кінці мультиплексованої магістралі потрібно виконати зворотну операцію - демультиплексування. Демультиплексор можна реалізувати на дешифраторі з n-входами, в якому вхід дозволу E використовується як інформаційний. Входи дешифратора a1, а2 є адресними. Тому в залежності від адресного числа лише на одному з виходів дешифратора з'являється логічна одиниця, яка дає дозвіл до спрацювання лише одного з чотирьох кон'юкторів D2…D5.

Если между числом выходов и числом адресных входов действует соотношение n=2m для двоичных демультиплексоров или n=3m для троичных демультиплексоров, то такой демультиплексор называют полным. Если n<2m для двоичных демультиплексоров или n<3m для троичных демультиплексоров, то демультиплексор называют неполным. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора.

Демультиплексоры выполняют унарные (одновходовые, однооперандные) логические функции с n-арным выходом.

Работа демультиплексора описывается логическими выражениями:

![]()

![]() где

mi

– минтермы n

адресующих переменных.

где

mi

– минтермы n

адресующих переменных.

Рисунок 3.18 – Принцип работы (а), схемная реализация (б)

и условное обозначение для мультиплексора (в)

Таблица 3.6 – Функционирование демультиплексора

При

большом числе входов, при необходимости,

может быть построено демультиплексорное

дерево.

При

большом числе входов, при необходимости,

может быть построено демультиплексорное

дерево.

Рисунок 3.19 – Мультиплексорное дерево

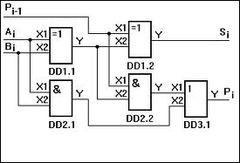

Питання №24. Двійкові суматори.

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов.

Двоичный сумматор

Двоичный сумматор может быть определён тремя способами:

табличным, в виде таблицы истинности,

аналитическим, в виде формулы,

графическим, в виде логической схемы.

Так как формулы и схемы могут преобразовываться, то, одной таблице истинности двоичного сумматора могут соответствовать множества различных формул и схем. Поэтому, с точки зрения получения результата без учёта времени, табличный способ определения двоичного сумматора является основным. Обычное табличное и обычное формульное задание сумматора не учитывают времена задержек в реальных логических элементах и не годятся для определения быстродействия реальных сумматоров.

Схема, которая обеспечивает сложение двух однобитных чисел А и В называется полусумматором. Полусумматор имеет 4 сигнальных линии: два входа для сигналов, представляющих одноразрядные двоичные числа А и В, и два выхода: сумма А и В по модулю 2 (S) и сигнал переноса (P). При этом S наименее значимый бит, а P наиболее значимый бит.

Схема полного сумматора может быть использована в качестве «строительных блоков» для построения схем многоразрядных сумматоров, путём добавления одноразрядных полных сумматоров. Для каждой цифры, которую схема должна быть в состоянии обрабатывать, используется один полный сумматор.

Двоичный одноразрядный полный сумматор является полной тринарной (трёхоперандной) двоичной логической функцией с бинарным (двухразрядным) выходом. Все три операнда и оба выходных разряда однобитные.

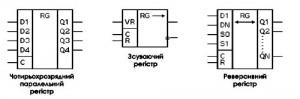

Питання № 25. Регістри.

Регістр— послідовний або паралельний логічний пристрій, який виконує функцію приймання, запам'ятовування і передавання інформації.

Інформація в регістрі зберігається за видом числа (слова), зображеного комбінацією сигналів 0 і 1. Кожному розряду числа, що записаний в регістр, відповідає свій розряд, побудований, як правило, на базі тригерів RS-, D- або JK- типу.

На регістрах можна виконувати операції перетворення інформації з одного виду на інший. Регістри можуть використовуватися для виконання деяких логічних операцій.

Класифікація регістрів

За способом запису і зчитування двійкової інформації

Послідовні

В послідовних регістрахзапис і зчитування інформації здійснюється послідовно за часом, тобто почергово. Вони мають послідовні виходи. Інформація записується шляхом послідовного зсуву числа синхроімпульсами. Тому регістри послідовного типу носять назвурегістрів зсуву.

В паралельних регістрах, які мають паралельні входи та виходи, запис інформації виконуються одночасно в усіх розрядах за один такт керування. Такі регістри називаютьрегістрами пам'яті.

Паралельно-послідовні регістримають або паралельний вхід та послідовний вихід, або послідовний вхід та паралельний вихід. Паралельно-послідовні регістри можуть бути як регістрами зсуву, так і регістрами пам'яті.

За способом приймання та передавання інформації

Регістри типу SISO - з послідовним входом та послідовним виходом;

Регістри типу SIPO - з послідовним входом та паралельним виходом;

Регістри типу PISO - з паралельним входом та послідовним виходом;

Регістри типу PIPO - з паралельними входом та виходами.

Найбільш універсальними вважаються

регістри, які мають у своєму складі

одночасно послідовні і паралельні входи

й виходи. Такі регістри називають

регістрами з послідовно-паралельним

прийманням інформації та послідовно-паралельним

передаванням.

Основною класифікаційною ознакою регістрів є спосіб запису двійкового коду в регістр і його видача.Зсовуючі регістри діляться на одно- і двонаправлені.

В загальному випадку регістр може виконувати наступні мікрооперації над кодовими словами:

встановлення в початковий стан (запис нульового коду);

запис вхідної інформації в послідовній формі;

запис вхідної інформації в паралельній формі;

зберігання інформації;

зсув береженої інформації управо або вліво;

видача береженої інформації в послідовній формі;

видача береженої інформації в паралельній формі;

Характеристики регістрів

Регістр являє собою набір двійкових ланок (тригерів з керуючими елементами), головним призначенням якого є зберігання інформації у вигляді багаторозрядних двійкових чисел

(двійкового коду). На відміну від пристроїв довгочасної пам'яті в регістрах інформація запам'ятовується короткочасно, тобто на період одного або кількох циклів роботи всієї системи.

Регістри призначені для запису, зберігання і читання одного двійкового числа або іншої кодової комбінації.

26. Арифметико-логічний пристрій.

Важнейшими функциональными узлами ЭВМ и МП являются арифметико-логические устройства (АЛУ), которые выполняют заданный набор арифметических (сложение, вычитание, умножение, деление, возведение в степень и др.) и логических (дизъюнкция, конъюнкция, инверсия, исключающее ИЛИ (И), сдвиг, сравнение, и др.) операций над двумя многоразрядными операндами. Аппаратными средствами, выполняющими эти операции, являются сумматоры.

Арифметико-логічний пристрій(АЛП) (англ.Arithmetic Logic Unit, ALU) — блок процесора, що служить для виконання арифметичних та логічних перетворень над даними, що іменуються операндами. Цей пристрій є фундаментальною частиною будь-якого обчислювача, навіть найпростіші мікроконтролери мають його в складі свого ядра.

Класифікація

Арифметико-логічні пристрої можуть класифікуватися за багатьма ознаками, наприклад розглянемо наступну класифікацію

За структурою

з розподіленою логікою (з закріпленими мікроопераціями);

з зосередженою логікою (з загальними мікроопераціями).

В першому випадку, апаратура для реалізації обчислень закріплена за регістрами та розділена між ними, тобто кожен з них використовує власну логіку для виконання операцій. У пристроях другого типу вся апаратура об'єднана в АЛП, а всі регістри — в регістровому файлі.

АЛП другого типу також можна класифікувати.

За типом запису даних

послідовні;

паралельні;

послідовно-паралельні.

В основу цієї класифікації покладено особливості роботи цифрового регістра.

За архітектурними особливостями

з двоспрямованою шиною та одноадресним регістровим файлом;

з односпрямованою шиною та одноадресним регістровим файлом;

з односпрямованою шиною та двоадресним регістровим файлом.

Використання двоадресного блоку регістрів чи шини дозволяє збільшити швидкодію, адже запис та читання даних може проводитися одночасно.

За формою подання даних

з фіксованою комою;

з плаваючою комою;

універсальні.

В деяких ЕОМ передбачається спеціальний режим цілих чисел, за якого кома фіксується за останнім розрядом.

За основою системи числення операндів

двійкові;

трійкові;

десяткові;

шістнадцяткові.

Окрім наведених, можливі й варіанти АЛП, що працюють в системах числення з основою 2k, де k — додатнє ціле число.

Залежно від часу виконання операцій

синхронного типу;

асинхронного типу;

комбінованого типу.

На виконання всіх обчислень в синхронних АЛП відводиться один і той самий час. Проте в асинхронних, витрачається скільки тактів, скільки потрібно, а наступна операція почне виконуватись лише після сигналу про завершення поточної. Комбіновані були створення з метою поєднати простоту та швидкодію і поділяють всі операції на дві групи — одно- та багатотактні. Операції першої групи виконуються за синхронним принципом, а другої — асинхронним.

Залежно від реалізації мікроалгоритму

зі схемним керуванням;

з мікропрограмним керуванням.

Виконання цих операцій зводиться до виконання послідовності мікрооперацій на регістрах, суматорах та інших цифрових схемах, що входять до складу АЛП - мікроалгоритмом.

Кожен АЛП може бути представлений як композиція пристрою управління, що керує та операційним пристроєм, що безпосередньо виконує операції.