- •3. Режимы функционирования технических объектов.

- •4. Основные виды анализа технических систем (тс) при математическом

- •5. Классификация математических моделей.

- •6. Операторные модели систем (частотные, преобразование Лапласа, z-преобразование).

- •7. Свойства преобразования Лапласа.

- •9. Свойства пф. Классификация типовых пф.

- •10. Анализ систем в частотной области.

- •11. Анализ устойчивости тс: определения, критерии устойчивости, примеры анализа.

- •12. Качественный анализ технических систем. Необходимость выполнения качественного анализа технических систем, его цели.

- •13. Моделирование нелинейных систем: определение нелинейной системы, виды нелинейных характеристик элементов технических систем.

- •14. Особенности поведения и анализа нелинейных систем, методы решения систем нелинейных ду.

- •15. Модели нелинейных систем на фазовой плоскости. Анализ технических систем по фазовому портрету. Примеры построения фазовых портретов.

- •16. Факторные модели и модели регрессионного анализа. Примеры реализации.

- •17. Состав пакета OrCad. Порядок работы с пакетом OrCad.

- •18. Спектральный анализ в OrCad.

- •19. Частотный анализ в OrCad.

- •20. Статистический анализ в OrCad.

- •21. Язык моделирования pSpice. Основные семантические конструкции языка pSpice.

- •22. Язык моделирования pSpice. Описание топологии схемы.

- •23. Язык моделирования pSpice. Первые символы имён компонентов.

- •24. Язык моделирования pSpice. Классификация моделей компонентов. Имена типов моделей.

- •25. Математические операции в pSpice: классификация, порядок и примеры применения.

- •Name — имя функции;

- •27. Язык pSpice. Анализ режима по постоянному току.

- •28. Язык pSpice. Частотный анализ.

- •29. Язык pSpice. Спектральный анализ.

- •30. Язык pSpice. Анализ шума.

- •31. Примеры описания директив на языке pSpice.

- •35. Реализация поведенческой модели в пакете OrCad. Применение элементов библиотеки abm.Slb.

- •36. Моделирование аналого-цифрового преобразователя (ацп) в пакете OrCad.

- •37. Моделирование цифро-аналогового преобразователя (цап) в пакете OrCad.

- •38. Основные блоки и конструкции языка vhdl.

- •39. Модели описания цифровой системы. Примеры.

- •40. Структура описания архитектурного тела vhdl. Примеры.

- •41. Структура описания интерфейса проекта на языке vhdl. Примеры.

- •42. Синтезируемое подмножество языка vhdl.

- •43. Интерфейс и архитектура объекта в языке vhdl.

- •44. Карта портов и карта настройки в языке vhdl.

- •45. Параллельный оператор generate в языке vhdl: назначение, общая формаописания, примеры применения.

- •46. Алфавит языка vhdl.

- •47. Скалярные типы в vhdl.

- •48. Регулярные типы в vhdl.

- •49. Физические типы в vhdl. Тип time.

- •50. Стандартные типы в vhdl.

- •51. Понятия сигнала и переменной в vhdl.

- •52. Атрибуты сигналов в языке vhdl.

- •53. Атрибуты скалярного типа в языке vhdl.

- •54. Атрибуты регулярного типа в языке vhdl.

- •55. Циклы в vhdl.

- •56. Оператор ветвления и селектор в vhdl.

- •57. Объявление компонента в vhdl. Включение компонента в схему.

- •58. Модели задержки в языке vhdl. Примеры применения.

- •59. Примеры описания регистровых схем на языке vhdl. Триггер d-типа

- •Vhdl-файл имеет следующее описание:

- •D-триггер с асинхронным сбросом

- •60. Основные операции в vhdl. Приоритеты операций.

- •61. Типы std_ulogic и std_logic.

- •62. Спецификация процедуры в vhdl.

- •63. Спецификация функции в vhdl.

- •Объявление функции

- •64. Пакет std_logic_arith. Функции преобразования типов.

57. Объявление компонента в vhdl. Включение компонента в схему.

Объявление компонента определяет интерфейс и модели на VHDL (Entity или Architecture). В момент моделирования должны существовать объявления Entity и Architecture для компонентов, которые не только объявлены, но и установлены в схему. Это позволяет задавать объявления библиотечных элементов, а реальные их описания (объявления Entity и Architecture) задавать по мере использования этих элементов.

Объявление компонента записывается в виде: Componentname [port (port_list);] endcomponent.

58. Модели задержки в языке vhdl. Примеры применения.

Объект с задержкой можно представить состоящим из двух: идеального элемента и элемента задержки:

В языке VHDL встроены две модели задержки: инерционная (inertial) и транспортная (transport).

Инерциальная модель предполагает, что элемент не реагирует на сигналы, длительность которых меньше порога, равного времени задержки элемента.

Транспортная модель не имеет такого ограничения.

Инерциальная модель по умолчанию встроена воператор назначения сигнала языка VHDL. Например, оператор назначения

Y<= inertialXIand Х2 after 10ns;

описывает работу вентиля 2И и соответствует инерциальной модели.

Указание на использование транспортной модели обеспечивается ключевым словом Transport в правой части оператора назначения. Например:

YT<= transportXIandX2 after 10ns;

Он отображает транспортную модель задержки вентиля. Если ключевое слово transport отсутствует, то подразумевается инерционная задержка. При транспортной задержке все изменения входных сигналов будут передаваться в выходные, но с указанной задержкой.

Задержка может быть задана не константой, а выражением. Для этого ее надо задать как параметр настройки в описании интерфейса объекта. Например:

Entity 12 is

Generic (T: time=10ns); - параметр настройки Т равен 10 не

Port (XI, Х2: in std_logic;

Y: out std_logic);

End 12;

Architecture A1 inert of 12 is

Begin

Y <= XI and X2 after T;

EndA1 inert;

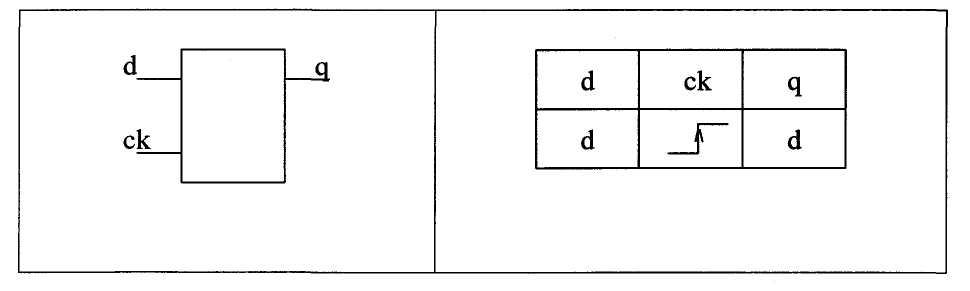

59. Примеры описания регистровых схем на языке vhdl. Триггер d-типа

Триггер работает по положительному фронту импульса. При этом происходит запись информации со входа D-триггера на его выход Q.

Vhdl-файл имеет следующее описание:

Library ieee;

Use ieee.std_logic_1164.all;

Entity dtype is Port (d, ck: in std_logic; q: out std_logic); end dtype;

architecture behavior of dtype is

begin

process (d, ck)

begin

if ck=' 1' and ck'event then

q<=d;

end if;

end process;

endbehavior;

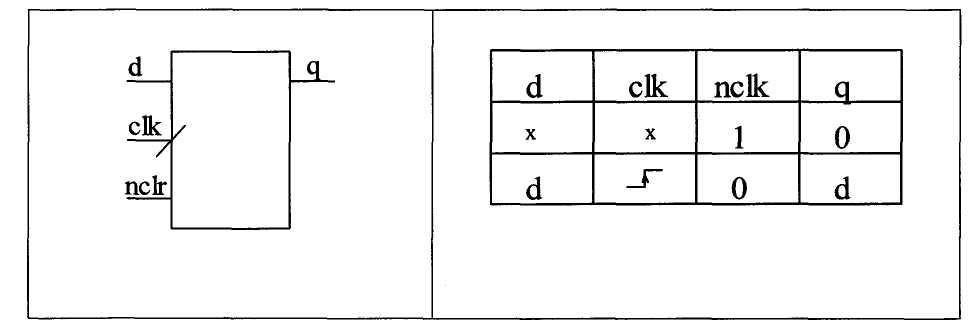

D-триггер с асинхронным сбросом

Library

ieee;

Use ieee.std_logic_l164.all;

Entity tr is

Port (d, clk, nclr: in std_logic;

q: out std_logic); end tr;

architecture beh of tr is

Begin

Process (nclr, clk)

Begin

If nclr='0' then q<='0';

elsif clk=' 1' and clk'event --(номожноитак:elsif clk='1' and not clk'stable)

then q<=d;

End if;

End process;

End beh;

Т-триггер - это счетный триггер. Он срабатывает по отрицательному фронту тактового импульса. Его описание приведено ниже:

Libraryieee;

Useieee.std_logic_l164.all;

Entity T is

Port ( c: in std_logic;

q: out std_logic); end T;

architecture beh of T is

Signal d: std_logic :='0';

Begin

Process(c)

Begin

if c='0' and с'event then

d <= not d; q <= d;

End if;

Endprocess;

Endbeh;