КТ.Модуль 1

.pdfЯкправило,пів |

нічнийпівденниймостиреалізуютьсявиглядіокремих |

|

|

|

|||

надвеликихінтегральнихсхем |

|

|

, але існуютьодночіповірішення.Саменабір |

|

|

||

системноїлогікивизначаєвсіключовіособливостісистемноїплати,які |

|

|

|

|

|

|

|

пристроїможутьпідключатисядонеї. |

|

|

|

|

|

|

|

Завантажувальний пристрій - збепрігограмнезабезпеченняє,яке |

|

||||||

виконуєтьсявідразупісля |

|

|

вімкнення живлення.Якправило,завантажувальний |

|

|||

пристрій міститьBIOS,однакможеміститий |

|

|

|

програмнезабезпечення |

,що |

||

працюєврамкахEFI. |

|

|

|

|

|

|

|

BIOS (basic input/output system - базовасистемавводу |

-виводу) |

- частина |

|||||

системногопрограмногозабезпечення |

|

|

|

, реалізованого увиглядімікропрограм, |

|||

які призначаєтьсядлязабезпеченняопераційнсистемідоступуапаратурий |

|

|

|

|

|||

комп'ютераіпідключенимдоньогопристроям. |

|

|

|

|

|

|

|

Уперскональнихмп |

|

|

'ютерахBIOSявляєсобоюнабірзаписаногов |

|

|

|

|

мікросхеперско'ютеранальногоммікропрограму,якізабезпечують |

|

|

|

|

|

||

почзавантаженнявекомп'ютераіподз операційноїльшпуски.стеми |

|

|

|

|

|

||

Дляновихплатформ,компнIntelзамінуніятрадиційномуBIOS |

|

|

|

|

|||

пропонуєEFI. |

|

|

|

|

|

|

|

EFI - інтерфейсміжопераційнситамікропрограмамитемою,які |

|

|

|

||||

керуютьнизькорівневимифункціямиобладнання,й сновнегопр :значення |

|

|

|

|

|||

коректноініціаобладнприізуванняти |

|

|

|

вімкненні |

системиіпередати |

||

керування завантажувачуопераційноїсистем |

|

и. |

|

|

|

||

ПрогрналаштумаможеBIOSбутивикликанаанняпісля |

|

|

|

|

|

||

перезаванкомп'ютерна певноїисканнямженняклавішічигрупиклавіш. |

|

|

|

|

|

|

|

Найбільшпоширені |

- Del, F2, F10, Esc. |

|

|

|

|||

Форм-фактор системноїплати |

- стандарт,щовизначаєрозміри |

|

|

||||

системноїплатидляперсонал |

|

|

ьнкомп'ютераго,місцяїїкріпленнядокорпусу; |

|

|

|

|

розташуваннянанійінтерфейсівшин,портіввводу/вив,роз'ємуду |

|

|

|

|

|

|

|

центпральоцесякщ(вінє) олдлягораопертівпам'я,такожіивної |

|

|

|

|

|

|

|

типроз'ємудляпідкблживленняюченоку. |

|

|

|

|

|

|

|

2Мікропроцесо.3. |

р |

|

|

|

|

|

|

Центральнийпроцесор |

|

|

- електрблокабмікрнн,щовисхемайконує |

|

|

||

машинніінструкційкоди(прогр),головнач апарстинам |

|

|

|

|

|

атногозабезпечення |

|

комп'ютера. |

|

|

|

|

|

|

|

Зчасіввинаходумікросхеми1959роцісвбулорозробленоті велику |

|

|

|

|

|||

кількістьрізнихпроцесорів, |

|

|

універсальспеціалізованих,різнимступенем |

|

|

|

|

інтеграціїтощо.Однакбудь |

|

|

-якийпроцесорсклзарифметикодається |

|

|

-логічного |

|

пристАЛП(), ристроюкеруванняісисте |

|

|

|

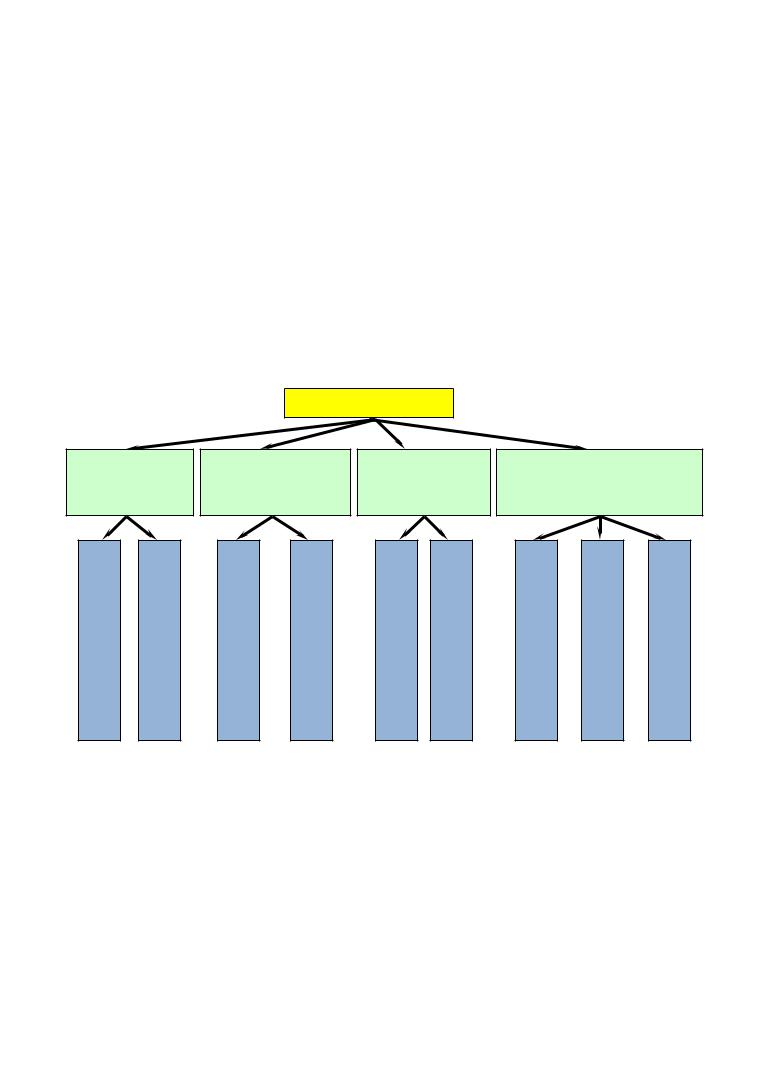

мнихрегістріврис(.2.5). |

|

|

|

Арифметико-логічнийпристрій |

єоднимз |

головних пристроїв процесора. |

|||||

Вінвикодзнусновнихфунємікропроцесорацій |

|

|

|

|

– обробкуданихі |

||

обчислення. |

|

|

|

|

|

|

|

Пристрійкерування |

|

|

служитьдля |

керування робкютерної' мптою |

|

||

системивцілромуцентботоюпральноцесзокрема.Оснжйгораговне |

|

|

|

|

|

|

|

44

завдання - дешифруванняком |

анд,щонадпроцесораходять |

іформування |

сигналувикотихчиіншиханняопевраційифметико |

|

-логічномупристрої. |

|

|

|

Рис. 2Загальна.5схема. процесора |

|

|

|

||

Системнірегістри |

призначенідлятимчасовогозберігоператаннядів |

|

|

|

||||

результатівобчислень.Алене |

|

|

|

дивлячнасвоєєд""призначеннясьне,ці |

|

|||

пристрозрізної |

|

яютьсязасвоїмифункціями. |

|

|

|

|

||

Головнимихарактеристиками |

|

процесора є:тактовачастота, |

|

|||||

продуктивність, |

|

енергосп,нормилітогживанняпрафічногооцесу |

|

|

, |

|||

використпри таоархітектуравуваногобництві |

|

|

|

. |

|

|||

Тактовачастотахарактеризуєпродукпідс, обкількістьвністьоеми |

|

|

|

|

|

|||

викопераційнувсекундух.Однаксистемизоднієютієюжтактовою |

|

|

|

|

|

|||

частотоюможутьматирізнупродукт,томущонавиковністьоднієїання |

|

|

|

|

|

|||

операціїврізнихсистемахможевимага |

|

|

|

тисярізн |

|

акільтактів. ість |

Крімтого, |

|

системи,щовикористовуютьконвеєрнуіпаралельнуобр,м набкуоднихжуть |

|

|

|

|

|

|||

ітихжетактахвиконуватиодночаснокількаоперацій. |

|

|

|

|

|

|

||

Архітектумікропроцесоріва |

|

. Підархітектурпроцесрозумієтьсяраю |

|

|||||

його «внутрішняко |

нструкція» |

або «організац»Більші. сучасятьних |

|

|||||

процесорівдля |

ПК взагальному |

базуються натійчиіншійверсіїциклічного |

|

|||||

процесупосліобрданихо,винайдеоїбкиДжономфоНейманом.ого |

|

|

|

|

|

|||

ВідмінноюособливісархітектурифонНейманає,щоюінструкці |

|

|

|

|

їідані |

|||

зберігаютьсяводнійтійжепам'яті. |

|

|

|

|

|

|

|

|

Етапицикл |

ічногопроцесусліобрданиховноїбки |

|

|

: |

|

|||

• |

Процесор зчитує число,щозберігаєть |

сявреглічильникастрікоманд |

і |

|||||

|

віддаєпам'ятікомандучитання. |

|

|

|

|

|

||

• |

Пам'ять,отримавши |

число,щоєдлянеїадресою, |

|

іком андучитання, |

||||

|

зчитує вміст,щозберігаєтьсязацієюадресоюповідпромляє |

|

|

|

||||

|

готовність. |

|

|

|

|

|

||

• |

Протримуєцесордан |

|

і,інтерпретує |

їх яккомашиннуанду( |

|

|||

|

інструкц)зісвоєїсистемикомандівиконуєюїї. |

|

|

|

|

|

||

• Якщоостамандаєкоманденяпереходу,прзбільюцесор |

|

|

|

|

шуєна |

|||

|

одиницючисло,щозберігаєтвлічилкоманд;врезультатіникуся |

|

|

|

|

|||

|

тамутворюєадресанаскомандитупноїься. |

|

|

|

|

|

||

Данциклв йконуєтьсянезмінно,саме |

|

|

|

вінназиваєтьсяпроцесом |

|

|||

(звідс иіпішланазвапристрою |

|

– процесор). |

|

|

|

|||

45

Послідовністькомандназивається |

|

прогі редставляєамоюалгоритм |

|

|

роботипроцесора. |

Послідовність зчитувкомзміанудняюється |

випадку, |

||

якщопрзчитуєцесоркомандупереходу, |

|

|

- тоаднаступноїресаікоможеанди |

|

виявитисяіншою. |

|

|

|

|

Швидкіспереходувід ноготциклуьапудоіншоговизна |

|

|

чається |

|

тактовимгенерат.Тактовийгенераторвиробляєромі пу,щос угуютььси |

|

|

||

ритмомдляцентпральноцес.Частотатактімпульсівгораназиваєтьсявих |

|

|

||

тактовчастотою |

. |

|

|

|

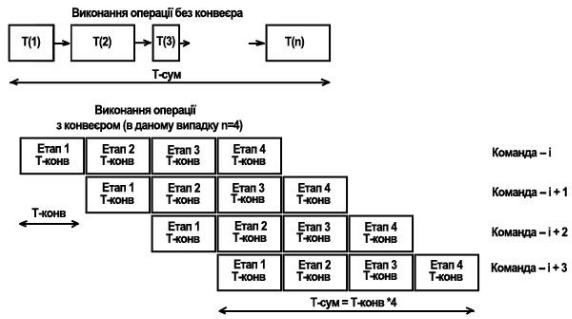

Конвеєрнаархітектура |

булавведенацентпрзоцесоральнийметою |

|

||

підвищенняшвидко |

дії.Заздлявичайкожнкомандинап няїтрібно |

|

|

|

здійснитидеякукількісодноопераційт.Кожнуьипнихзцихоперацій |

|

|

|

|

зіставляють з однимступ |

енем конвеєра. |

|

|

|

Післязвільнення |

k-гоступіняконвеєра |

інвідпразуиступаєдороботи |

|

|

наднаступноюкомандою.Як |

|

щоприпустити,щок ступіньженконвеєра |

|

|

витрачодичансвоаицюєроботу,товикоманаконвеєріяди |

|

|

|

|

завдовжкиступенівn займеодиницьn часу, |

|

|

але викожноїнаступноїня |

|

командибудепроходитичерезкожнуодиницючасу |

|

|

(рис. 2.6) . |

|

|

|

Рис. 2 .6Принцип. роботиконвеєрноїархітектури |

|

Фактори,що |

знижуютьефеконти: веєраність |

|

|

• |

Прконвстій,колидеступєраякі |

еніневикористовуються. |

|

• |

Очікування:якщонаступкомандавикористовуєрезультат |

|

|

|

поперед,тоостанеможепочатиньоїня |

сяраніше виконанняпершої. |

|

•Очищенняконвеєраприпопаданнінькомандигопереходуцю( проблемувдається вирішити,використовуюмодульпередбаченняи

|

переходів). |

|

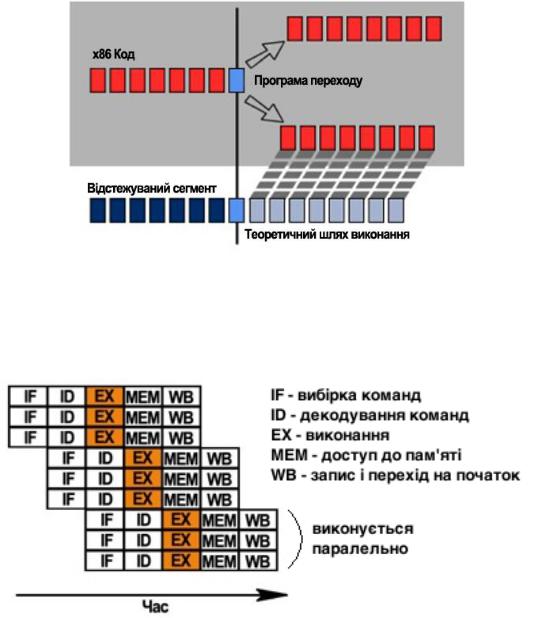

Модульпередбачумовнихеходівння |

— пристрій,якв значає |

|

напрямрозгалуженьпередбач( ,виконаєть |

сяумовперехід,чин)вий |

|

програмі,що |

запущена.Входитьдоскладумікропроцесорів,якімають |

|

конвеєрнуархіт.П редбаченняктурурозгалуженьдозволяєробитипопередню |

|

|

46

вибіркуінстаданихрукційзпам'я,такожвиконуватиінструкції,які |

|

розташовані післяумовнперехдтого,квінбуделидувиконаний |

(рис. |

2.7).Модульпередбаченняєневід'ємноючастиноюу учаснихіх |

|

мікропроцесорів,бобільшостівипадків |

дозволяєоптимально |

використовобчислювальніреспроцесораурси.вати |

|

Рис. 2Модуль.7. |

передбачумовнихенняходів |

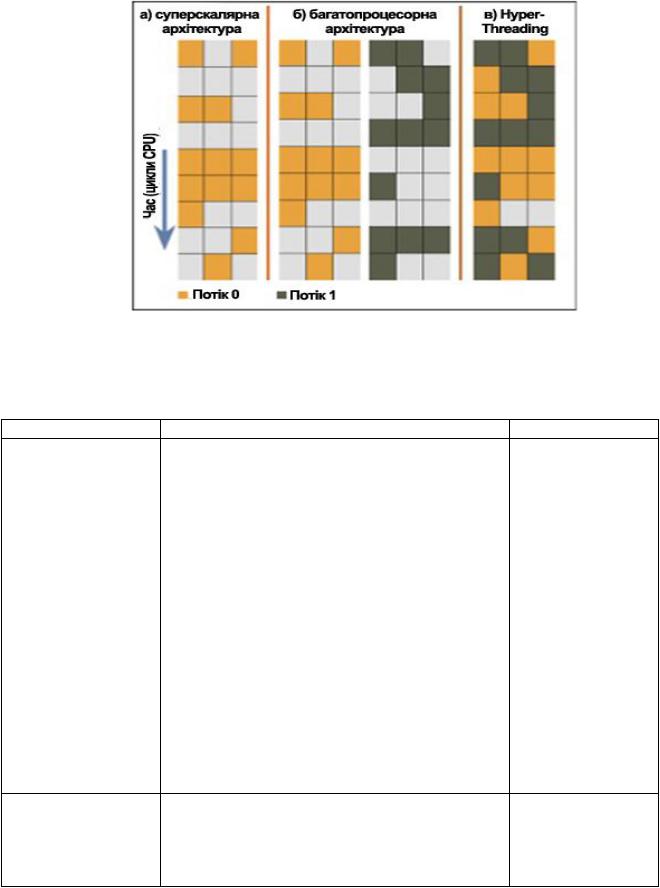

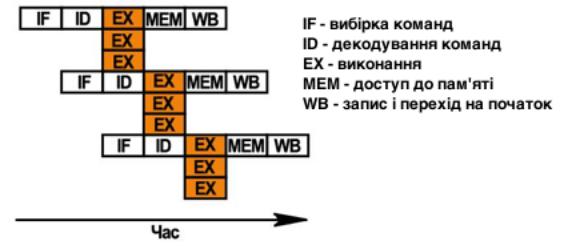

Супеархитектураскалярна |

- здатністьвиконаннядекількохмашинних |

інструзаодинтактпроцесораційшляхомзбільшенчиславиконавчихя |

|

пристроїв (рис. 2.8) .Появацієїтехнологіїпризвел |

а доістотногозбільшення |

продуктивності. |

|

Рис. 2Супе.8. архітектураскалярна

Оскількиприв користаннісупеархітескалярної,деякачастинатури ресурсівпроцесонезадіянаможебутир(.ис2),була.розроблена9 технологія

Hyper Threading,щод використатизволяєціресурсидляпаралель ного обчисленнярис(. в),2.творюючи9двапот,якідляопераційноїкисистеми виглядаютьякная ністьохпроцесорівгічн(.иб2)х..9

47

Рис. 2Технологія.9.HyperThreading

Крімархітектури значнурольвідіграєконцепціяпроектування процесорівтабл( . 2.1)

Назва

CISC - обчисленнязі склнаборомдним

команд

RISC - обчисленняіз спрощенимнаборо

команд

MISC - обчисленняз мінімальним

наборкоманд

Концепроектуванняроцесорівції

Характеристика

Характеризуєтьсянаступнимнабором |

|

властивостей: |

|

• нефіксзначендовкомандижини; яе |

|

• арифметичнідіїкодуютьсяводній |

оманді; |

• невеликечислорегістрів,кожензяких |

|

виконуєстрогопевнуфункцію. |

|

Архітектурапроцесора,вякійшвидкодія |

|

збільшуєтьсязарахунок |

спрощекома, нняд |

щобїхдекодуваннябулопр,часстішим |

|

виконання - меншим.Цетакполегшуєж |

|

підвищеннятактовчастробитьбільштиї |

|

ефективноюсуперскалярність. |

|

Процес,щоутворюютькомп«'ютериз |

|

мінімальнимнабко»,якмандромпроцесори |

|

RISC,характерневеликимчисломзуються |

|

ком,щонайчастішендзустрічаються.Порядок |

|

викомандрозподіляєтьсянаннятакимчином, |

|

щобмаксизавантажитимаршально |

рути,по |

якихпроходятьпотокиданих. |

|

VLIW – дужедовге |

Характеризуєтьсятим,щооднаінструкція |

|

|

процесораміститькількаоперацій,якіповинні |

|

||

команднеслово |

|

||

виконуватисяпаралельно. |

(рис. 2.10) |

||

|

48

Таблиця2. 1.

Представники

Intel Pentium 4,

Pentium D, Core

AMD Athlon,

Phenom

Motorola MC680x0

ARM, DEC Alpha,

SPARC, AVR,

MIPS,і POWER

PowerPC

Philips TriMedia, TI DSP C6000 (в

чистомувигляді)

GPU AMD R600 і

вище

Рис. 2Архітектура.10VLIW. |

|

АрхітфонНемаєктураймананедолік |

- вонапослідовна.Якбий |

величезниймасивданне магалосяхбобр,к йогобитиженбайтповинен |

|

будепройтичерезцентпр,оцесорнавітьальякщоусімаадийбайтами |

|

потрібнопр днувестиітужоперацію.Дляподоланняцьогонедоліку |

|

пропонувалисяіпропонуютьназиваютьсяархітектурипроце,які орів |

|

паралельними.Паралельніпроцесоривикористовуютьсясуперкомп'ютерах. |

|

Можливимиваріпантаархітектуриралельноїможут |

ьслужитиза( |

класифікацієюФлінна): |

|

• SISD - одинпотіккоманд,одинпотікданих; |

|

• SIMD - одинпотіккоманд,багаподанихто; ків |

|

• MISD - багапокомандто,одинківпотікданих; |

|

• MIMD - багапокомандто,багаківподанихто. ків |

|

Набіркоманд – додатковийнабірінструкцій,щод виконуватизволяє характернідляпропцзаоднураціїсівмашиннуінструкцію,розширюючи цимможливопроце. сораті

Доосновнихабкомавідрів:ндосять MMX, 3DNow!, SSE, SSE2, SSE3, SSSE3, SSE4.

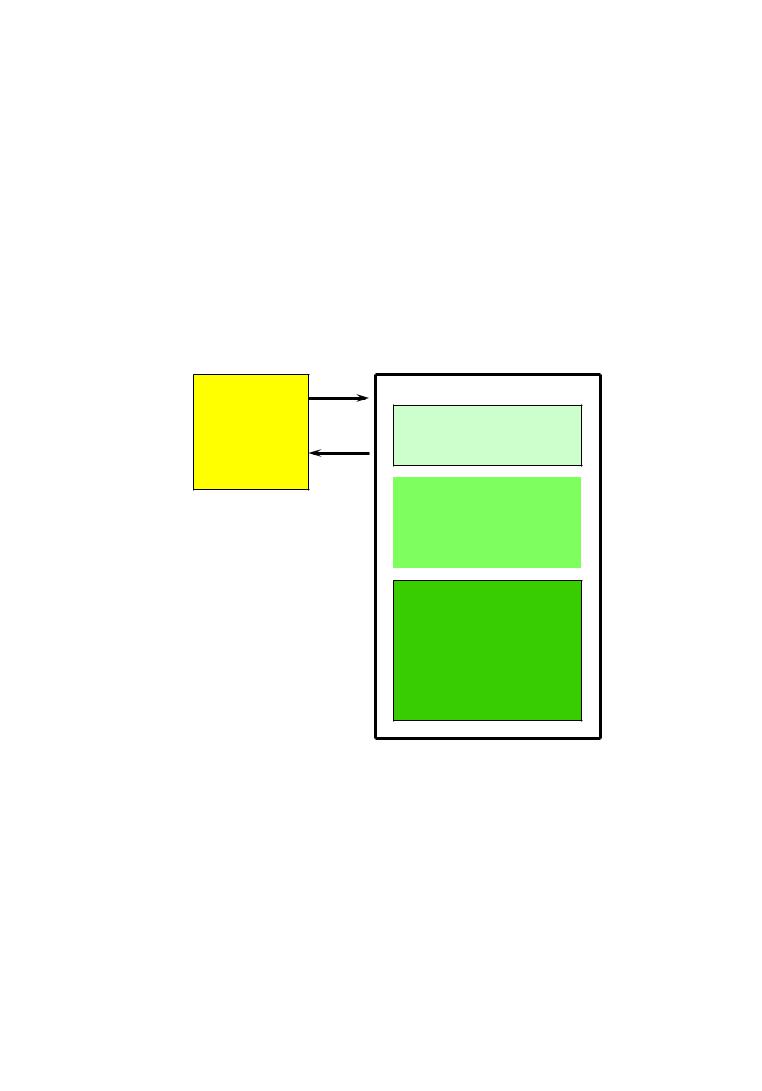

Кеш-пам'ятьпроцесора |

. Кеш - проміжнийбуферзшвидкимдоступом, |

щоміститьінформацію,якаможебутизапрошенанайбільшоюймовірністю. |

|

Доступдоданихвкеші |

здійснюється швидше,ніжвибіркавихіднихданихз |

оперативноїізовнішньоїпам'яті,зарахунокчогозменшуєтьсясереднійчас |

|

доступуізбільшуєтьсязагальнапродуккомп'ютсерноїи.встемиість |

|

Більшісучамікропроцесотьнихдлякомп'ютісервемаютьівякрів |

|

мінімумтринезалежнихкеш |

і:кешінструкційдляприскореннязавантаження |

машинногоко,кешдуанихдляприскореннячит |

анняізаписуданих,ібуфер |

асоцітра.Кештивнсляціїдачастореалізуєтьсяихоївигляді |

|

багаторівневогокешу(L1, L2, L3). |

|

Збільшеннярозмірукеш |

-пам'ятіпозитивновпливаєнапродуктивність |

майжевсіхпрограм. |

|

|

49 |

Придоступіпроцесвпам'ятьспочаткура |

|

|

здійснюєтьсяперевірка,чи |

||

зберігаєкешзапитуваніпам'ятідані.Дляцьогопровпорівняннядиться |

|

|

|

|

|

адресизапитузізначеннямивсіх |

|

|

міток кешу,вякихціданіможуть |

|

|

зберігається.Випадокзбігу |

|

|

зміткою |

будь-якоїеш |

-лініїназивається |

попаданнямвкеш(ca |

che hit), |

випназиваєтьсядоккеш |

-промахом |

||

(cacheВідношеннякількостіmiss)попаданьвкешдозага. кільнкоїсті |

|

|

|

|

|

запиназиваютьдопам'яті рейтингомпопадань(hit rate) |

|

|

|

,вінємірою |

|

ефекешутивності |

дляобраналгоритмуабопрограми. |

|

|

||

Великікешімаютьб високийльшвідсотокпопаданьале,разомти,і |

|

|

|

|

|

великузатримку.Щпослабпротиріччяміжцимидвомапар, метрами |

|

|

|

||

більшістькомп'ютеріввикокількарівнівисткешу, опіслявуєлималеньких |

|

|

|

|

|

швидкихкешейзнахповдятьсяільніші |

|

|

еликікешізараз( |

- сумардорів3 ноів |

|

вієрархіїкешей |

,рис. 2.14 |

)У.поодинокихреал зуютьвні |

- |

||

пам'яті. |

|

|

|

|

|

L1 (перівеньший )

L2 (другийрівень |

) |

256Кб – 12Мб |

|

|

|

L3 (третійрів ень) до24Мб,вокремих випадкахможебутиі

більше

Рис. 2Ієрархія.11 |

-пам’ятіпроцесора |

Багаторівневікешізазвичайпрацюютьпослвменідкешейовностіих довеликих.Спочаткувідбуваєперевірканайменшоготанайвидшогоьсякешу перівняшого(L1),уразіпопаданняроцесроботпроднависокійвжує швидкості.Якщоменкешдавпромахий,перевіряєтьсянаступний,більший

повільнкешдругогорівняший(L2), ітакдалі,покинебудезапитудо основногоОЗП.

2Орг.4. пам’ятікомпн’ютеразація

Комп'ютернапам'ятьзабезпечпідтримкуодніф сучасногоєнкційї комп'ютера, - здатністьтривалогозберіганняінф.Разомцентральним

50

ключовиланка,такзваноїми ,закладвосновуп ного

вимб рянанезалежно

системічисленняфункціонує

представити

послідовн стями ми довстатньоїємності

агато пристроївдлязберігання

в кожногопереваги |

ісвої,ткомпму' |

Пам’ять

Доступні

Віртуальна

. Класифікаціятипів. пам’яті |

|

|

|

|

ієрархіяпам |

врегістровий |

- найбільш |

|

1зько),алер зміром |

|

|

(L1) - |

декільк |

а тактів |

кілобайт |

|

|

(L2) - |

доступу10разів |

|

б . |

|

|

• Кешпроцесораго3рівня |

|

(L3) - часдоступублизьсотніта,ктіво |

|

|||

|

розміромвдекількамегабайту процесорах(сових |

|

|

|

||

|

використовуєтьсязнедавньогочасу). |

|

|

|

||

• |

ОЗП системи - часдоступувідсотень |

тисячітактів,алеличезні |

||||

|

розміривкількагіг,ажбайт |

|

додесятків. |

|

|

|

• |

Дисковесховище |

|

- багамільйотактів,якщоданібулиеів |

|

|

|

|

закешовабозабуфезаздалегідьні,рои деоміривані |

|

|

кількох |

||

|

терабайт. |

|

|

|

|

|

• Третиннапам'ять |

|

- затримкидодекількохсекундабохвилин,але |

|

|

|

|

|

практичнонеобмеженіобсягистрічкові( бібліотеки). |

|

|

|

||

Нарисунку2представлена.12класипампів’фікяті. ція |

|

|

|

|||

2Оперативна.5. пам’ять |

|

|

|

|

|

|

Оперативнапам'ять |

|

(RAM - Random Access Memory,пам'ятьз |

||||

довільнимдоступом) |

- |

енергозалчасистемитинакомп'ютерноїжнапам'яті,в |

|

|

|

|

якійтимчасовозберданікомандигаються,необхідніпроцесорудля |

|

|

|

|

||

викнимонанняперації. |

|

|

|

|

|

|

Обов'язковоюумовоюєадресованістьпам'ятікожне( машиннесловомає |

|

|

|

|||

індивідуальнуадресу). |

|

|

|

|

|

|

Дані,щомістятьсявоперпам'ятідоступтількитивнійтоді,колина |

|

|

|

|||

модуліпам'ятіподна,єтьсятобтопруга,коликомп'ютерувімкнений. |

|

|

|

|||

Припиненняподачіживленнянамодуліпам'яті,навітькороткочасне, |

|

|

|

|||

призвдоспоадитьтворення |

|

боповногознищенняданих |

|

|

ОЗП. |

|

Операзапам'ятовуючийивнийпристрій |

,ОЗП |

- |

технічнийпристрій,що |

|||

реалізуєфункціїоперпам'яті. тивної |

|

|

|

|

|

|

ОЗПможевиготовякокремийблабовходитиятисяконструкцію, |

|

|

|

|||

наприклоднокристальноїЕОМмікроконтролерабо. |

|

|

|

|||

ОЗПбільшсучако'юсмптявляєнихерівсобмдинамічноїдулію |

|

|

|

|||

пам'яті,щомістятьнапівпровідниковіінтегральнісхеми,організованіза |

|

|

|

|||

принципомпристрздовільним.ступомПамїв'ятьдинамічноготипу |

|

|

|

|||

дешевша,ніжстатичного,іїїщільністьвища,щод з |

|

|

|

воляєнатійжеплощі |

||

кремнієвоїпідкладрозміщуватибільшекомірокпам'яті,алеприцьомуїї |

|

|

|

|

||

швидкодіянижча.Статична,навпаки,більшшвпам'ять,аледкавонаі |

|

|

|

|

|

|

дорожча.Узв'язцимкуоперативнусовупам'ятьбудуютьнамодулях |

|

|

|

|||

динапа'яті,ма ічної |

пам'ятьстатвикпучнодляристовуєтьсягопобудови |

|

|

|

||

кеш-пам'ятівсерединімікропроцесора. |

|

|

|

|||

Пам'ятьдинамічноготипу |

|

- DRAM (Dynamic random access memory - |

||||

динп'ятьамздовільнимічнадоступом) |

|

|

- |

типенергозалежної |

||

напівпровідниковоїпам'ятіздовільним |

|

доступом; |

DRAM широко |

|||

використовуєтьякостіоперпам'ятісучативноїкомп'ютерівс,янихатакож |

|

|

|

|

||

якостіпосховищатійногоінформаціїсистем,вимдозагливихтримок. |

|

|

|

|||

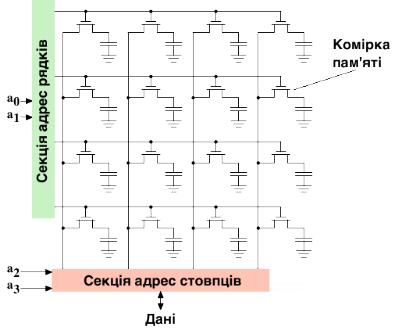

Фізично DRAM-пам'ятьпредстсобоюнабірзапам'ятовуючихвляє |

|

|

|

|||

комірок,якіскладают |

|

ьсязконденсаторівтранзисторів,розташо аних |

|

|

|

|

всерединінапівпровідниковихм кросхемпам'яті |

(рис. 2.1 |

|

3). Зазвичайкомірки |

|||

52

пам’ятіконфігувматрядківтастовпцівуютьсяицю.Такимчином,повна |

|

|

адресакоміркиданихділнадвакомпонентиться |

– адреса ядкатаадреса |

|

стовпця. |

Привідсутностіподачіелектроенергіїдопам'ятіцьоготипу |

|

відбувається розрядкон,іпаменсат'ятьспустошуєтьсяобнуляється( рів). |

||

Навідмінушвидкстатичної,аледоропамгої'ятипуі |

SRAM,якає |

|

конструктивнобільшскладни |

мібільшдорогимтипопам'яті,повільна,але |

|

дешевапам'ять |

DRAM виготовляєтьнаосновіконденвеликоїсяаторів |

|

ємнос,якішвтидкоірзаряд,томучаютьінформаціюдоводитьсяоновлювати |

|

|

черезпевніпроміжкичасу,щобуникнутивтратданих.Цейпроцес |

азивається |

|

регенерацієюпам'яті.Протягомчасу,щоназиваєтьсякрокомрегенерації, |

|

|

DRAM перезаписуєтьсяцілийрядоккомі,че8ок |

-64мсоновсілюються |

|

рядкипам'яті. |

|

|

|

|

Рис. 2Структура.13DRAM. |

|

Призверненнідокоміркипам'ятіконтролерпам'ятіза |

|

даєномербанку, |

|

номерстовньому,номерінкирядкатаномерстоінавцсіпцязапити |

|

|

|

витрч,крімачаєтьсяцьдоситьвеликийгоперіодйденаві закриття |

|

|

|

банкупіслясамоїоперації.Накожнудіюпотрібенчас,щоназивається |

|

|

|

таймінгом. |

|

|

|

Основнимитаймінгами |

DRAM є:затримкаміжподачномерарядкаі ю |

|

|

номерастовпця,щозиваєтьсячасомповногодоступу( |

RAS to CAS delay), |

||

затримкаміжподачномерастіювпцятривмістукоміркианням,що |

|

|

|

називаєтьсячасомробочогоциклу( |

CAS delay),затримка |

іжчитанням |

|

останньоїкоміркиподачномерановогорядкаю( |

RAS precharge). Таймінги |

||

вимірюютьсянаносеаботактах,чимменшаундахвелцитаймінгівчинах, |

|

|

|

тимшвидшепрацюєоперативнапам'ять. |

Позначтаймінгиступнимються |

|

|

чином: 2 |

-2-2. |

|

|

53