- •Contents

- •List of tables

- •List of figures

- •1 Introduction

- •2 Description

- •2.1 Device overview

- •2.2 Overview

- •2.3 Embedded Flash memory

- •2.4 CRC (cyclic redundancy check) calculation unit

- •2.5 Embedded SRAM

- •2.6 Nested vectored interrupt controller (NVIC)

- •2.7 External interrupt/event controller (EXTI)

- •2.8 Clocks and startup

- •2.9 Boot modes

- •2.10 Power supply schemes

- •2.11 Power supply supervisor

- •2.12 Voltage regulator

- •2.16 Timers and watchdogs

- •2.16.3 Basic timers TIM6 and TIM7

- •2.16.4 Independent watchdog

- •2.16.5 Window watchdog

- •2.16.6 SysTick timer

- •2.18 Universal synchronous/asynchronous receiver transmitter (USART)

- •2.19 Serial peripheral interface (SPI)

- •2.22 Remap capability

- •2.25 Temperature sensor

- •3 Pinouts and pin description

- •4 Memory mapping

- •5 Electrical characteristics

- •5.1 Parameter conditions

- •5.1.1 Minimum and maximum values

- •5.1.2 Typical values

- •5.1.3 Typical curves

- •5.1.4 Loading capacitor

- •5.1.5 Pin input voltage

- •5.1.6 Power supply scheme

- •5.1.7 Current consumption measurement

- •5.2 Absolute maximum ratings

- •5.3 Operating conditions

- •5.3.1 General operating conditions

- •5.3.2 Operating conditions at power-up / power-down

- •5.3.3 Embedded reset and power control block characteristics

- •5.3.4 Embedded reference voltage

- •5.3.5 Supply current characteristics

- •5.3.6 External clock source characteristics

- •5.3.7 Internal clock source characteristics

- •5.3.8 PLL characteristics

- •5.3.9 Memory characteristics

- •5.3.10 EMC characteristics

- •5.3.11 Absolute maximum ratings (electrical sensitivity)

- •5.3.12 I/O port characteristics

- •5.3.13 NRST pin characteristics

- •5.3.14 TIMx characteristics

- •5.3.15 Communications interfaces

- •5.3.17 DAC electrical specifications

- •5.3.18 Temperature sensor characteristics

- •6 Package characteristics

- •6.1 Package mechanical data

- •6.2 Thermal characteristics

- •6.2.1 Reference document

- •6.2.2 Selecting the product temperature range

- •7 Ordering information scheme

- •8 Revision history

STM32F100x4, STM32F100x6, STM32F100x8, STM32F100xB |

Electrical characteristics |

|

|

5 Electrical characteristics

5.1Parameter conditions

Unless otherwise specified, all voltages are referenced to VSS.

5.1.1Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at TA = 25 °C and TA = TAmax (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean±3 ).

5.1.2Typical values

Unless otherwise specified, typical data are based on TA = 25 °C, VDD = 3.3 V (for the 2 V VDD 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean±2 ).

5.1.3Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

5.1.4Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 8.

5.1.5Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 9.

Doc ID 16455 Rev 3 |

31/86 |

Electrical characteristics |

STM32F100x4, STM32F100x6, STM32F100x8, STM32F100xB |

|

|

|

|

Figure 8. Pin loading conditions |

Figure 9. Pin input voltage |

|

C = 50 pF |

|

|

|

|

|

|

|

|

|

|

|

|

|

STM32F10xxx pin |

|

|

V |

|

|

|

|

|

|

|

|

|

STM32F10xxx pin |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

IN |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ai14123b |

|

|

|

|

|

|

|

|

|

|

|

|

|

ai14124b |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

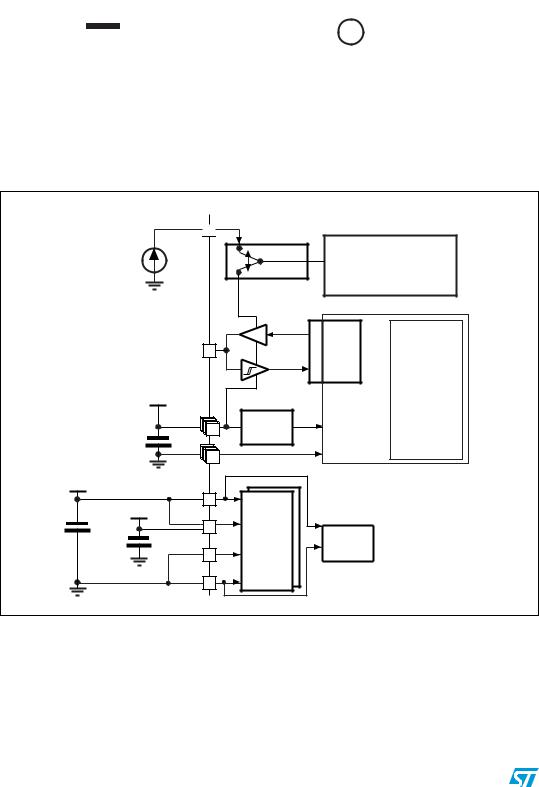

5.1.6Power supply scheme

Figure 10. Power supply scheme

VBAT

1.8-3.6V

Power switch |

Backup circuitry (OSC32K,RTC, Wake-up logic Backup registers)

|

OUT |

shifter |

|

|

|

|

|

GP I/Os |

|

|

IO |

IN |

Level |

Logic |

|

|

|

||

|

|

|

|

|

VDD |

|

|

|

|

|

|

VDD |

|

|

|

|

|

1/2/3/4/5 |

Regulator |

|

|

|

|

|

|

|

|

5 × 100 nF |

|

VSS |

|

|

|

+ 1 × 4.7 µF |

|

1/2/3/4/5 |

|

|

VDD |

|

|

VDDA |

|

|

|

|

|

|

|

|

|

VREF |

VREF+ |

|

|

|

|

|

|

|

|

|

10 nF |

10 nF |

|

VREF- |

ADC |

Analog: |

+ 1 µF |

|

RCs, PLL, |

|||

+ 1 µF |

|

||||

|

|

|

|

... |

|

|

|

|

|

|

|

|

|

|

VSSA |

|

|

Kernel logic (CPU, Digital

& Memories)

ai14125d

Caution: In Figure 10, the 4.7 µF capacitor must be connected to VDD3.

32/86 |

Doc ID 16455 Rev 3 |