- •Contents

- •List of tables

- •List of figures

- •1 Introduction

- •2 Description

- •2.1 Device overview

- •2.2 Overview

- •2.3 Embedded Flash memory

- •2.4 CRC (cyclic redundancy check) calculation unit

- •2.5 Embedded SRAM

- •2.6 Nested vectored interrupt controller (NVIC)

- •2.7 External interrupt/event controller (EXTI)

- •2.8 Clocks and startup

- •2.9 Boot modes

- •2.10 Power supply schemes

- •2.11 Power supply supervisor

- •2.12 Voltage regulator

- •2.16 Timers and watchdogs

- •2.16.3 Basic timers TIM6 and TIM7

- •2.16.4 Independent watchdog

- •2.16.5 Window watchdog

- •2.16.6 SysTick timer

- •2.18 Universal synchronous/asynchronous receiver transmitter (USART)

- •2.19 Serial peripheral interface (SPI)

- •2.22 Remap capability

- •2.25 Temperature sensor

- •3 Pinouts and pin description

- •4 Memory mapping

- •5 Electrical characteristics

- •5.1 Parameter conditions

- •5.1.1 Minimum and maximum values

- •5.1.2 Typical values

- •5.1.3 Typical curves

- •5.1.4 Loading capacitor

- •5.1.5 Pin input voltage

- •5.1.6 Power supply scheme

- •5.1.7 Current consumption measurement

- •5.2 Absolute maximum ratings

- •5.3 Operating conditions

- •5.3.1 General operating conditions

- •5.3.2 Operating conditions at power-up / power-down

- •5.3.3 Embedded reset and power control block characteristics

- •5.3.4 Embedded reference voltage

- •5.3.5 Supply current characteristics

- •5.3.6 External clock source characteristics

- •5.3.7 Internal clock source characteristics

- •5.3.8 PLL characteristics

- •5.3.9 Memory characteristics

- •5.3.10 EMC characteristics

- •5.3.11 Absolute maximum ratings (electrical sensitivity)

- •5.3.12 I/O port characteristics

- •5.3.13 NRST pin characteristics

- •5.3.14 TIMx characteristics

- •5.3.15 Communications interfaces

- •5.3.17 DAC electrical specifications

- •5.3.18 Temperature sensor characteristics

- •6 Package characteristics

- •6.1 Package mechanical data

- •6.2 Thermal characteristics

- •6.2.1 Reference document

- •6.2.2 Selecting the product temperature range

- •7 Ordering information scheme

- •8 Revision history

Description |

STM32F100x4, STM32F100x6, STM32F100x8, STM32F100xB |

|

|

2 Description

The STM32F100xx value line family incorporates the high-performance ARM Cortex™-M3 32-bit RISC core operating at a 24 MHz frequency, high-speed embedded memories (Flash memory up to 128 Kbytes and SRAM up to 8 Kbytes), and an extensive range of enhanced peripherals and I/Os connected to two APB buses. All devices offer standard communication interfaces (up to two I2Cs, two SPIs, one HDMI CEC, and up to three USARTs), one 12-bit ADC, two 12-bit DACs, up to six general-purpose 16-bit timers and an advanced-control PWM timer.

The STM32F100xx lowand medium-density value line family operates in the –40 to +85 °C and –40 to +105 °C temperature ranges, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F100xx value line family includes devices in three different packages ranging from 48 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F100xx value line microcontroller family suitable for a wide range of applications:

●Application control and user interface

●Medical and handheld equipment

●PC peripherals, gaming and GPS platforms

●Industrial applications: PLC, inverters, printers, and scanners

●Alarm systems, Video intercom, and HVAC

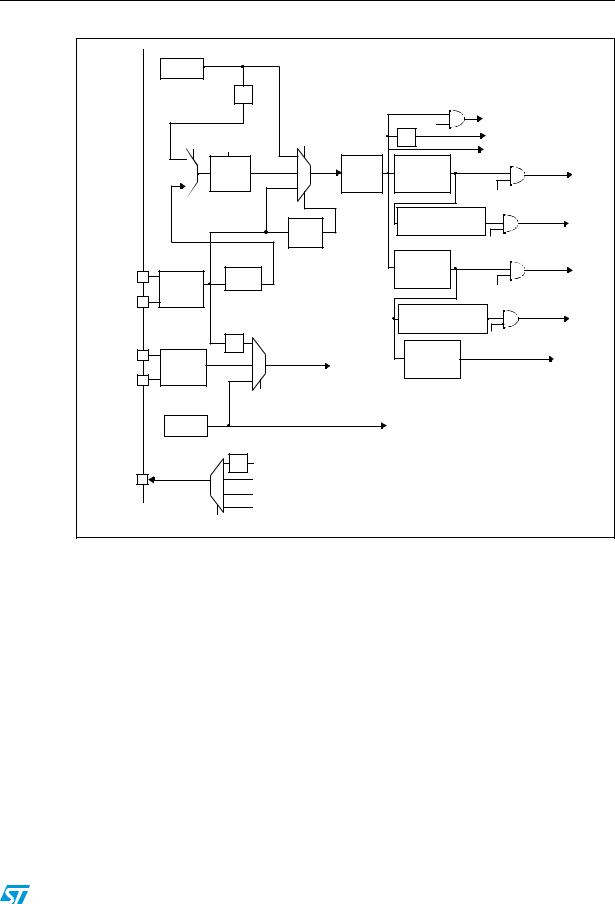

Figure 1 shows the general block diagram of the device family.

10/86 |

Doc ID 16455 Rev 3 |

STM32F100x4, STM32F100x6, STM32F100x8, STM32F100xB |

Description |

|

|

2.1Device overview

Table 2. |

STM32F100xx features and peripheral counts |

|

|

|

|

|

|

|

|

|

|

|||||||||

|

Peripheral |

STM32F100Cx |

|

|

|

STM32F100Rx |

STM32F100Vx |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Flash - Kbytes |

16 |

|

32 |

|

64 |

|

128 |

|

16 |

|

32 |

|

64 |

|

128 |

64 |

|

128 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

SRAM - Kbytes |

4 |

|

4 |

|

8 |

|

8 |

|

4 |

|

4 |

|

8 |

|

8 |

8 |

|

8 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timers |

|

Advanced-control |

1 |

|

|

1 |

|

|

|

1 |

|

|

1 |

|

1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

General-purpose |

5(1) |

|

|

6 |

|

|

|

5(1) |

|

|

6 |

|

6 |

||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

SPI |

1(2) |

|

|

2 |

|

|

|

1(2) |

|

|

2 |

|

2 |

|||||

Communication |

I2C |

1(3) |

|

|

2 |

|

|

|

1(3) |

|

|

2 |

|

2 |

||||||

interfaces |

|

USART |

2(4) |

|

|

3 |

|

|

|

2(4) |

|

|

3 |

|

3 |

|||||

|

|

CEC |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12-bit synchronized ADC |

|

|

|

1 |

|

|

|

|

1 |

|

|

|

|

1 |

||||||

number of channels |

|

10 channels |

|

|

|

|

16 channels |

|

|

16 channels |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

GPIOs |

|

|

|

|

|

37 |

|

|

|

|

51 |

|

|

|

|

80 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12-bit DAC |

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

Number of channels |

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

CPU frequency |

|

|

|

|

|

|

|

|

|

24 MHz |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Operating voltage |

|

|

|

|

|

|

|

|

2.0 to 3.6 V |

|

|

|

|

|

|

|||||

|

|

|

|

|||||||||||||||||

Operating temperatures |

Ambient operating temperature: –40 to +85 °C /–40 to +105 °C (see Table 8) |

|||||||||||||||||||

|

|

|

Junction temperature: –40 to +125 °C (see Table 8) |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Packages |

|

|

|

|

LQFP48 |

|

|

LQFP64, TFBGA64 |

LQFP100 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.TIM4 not present.

2.SPI2 is not present.

3.I2C2 is not present.

4.USART3 is not present.

Doc ID 16455 Rev 3 |

11/86 |

Description |

STM32F100x4, STM32F100x6, STM32F100x8, STM32F100xB |

|

|

Figure 1. STM32F100xx value line block diagram

42!#%#,+ |

|

|

|

|

|

4RACE |

|

|

|

|

|

|

|

|

42!#%$; = |

40)* |

|

|

PBUS |

|

|

|

|

|

6$$ |

|

0OWER |

|

|

|

%4- |

|

CONTROLLER |

|

|

|

|

|

||||||

AS !& |

|

|

|

|

|

|

|

|

|

6$$ 66TO 6 |

||||

|

TRACE TRIGGER |

|

|

|

|

|

|

|

|

6OLTAGE REG |

||||

|

37*4!' |

|

|

|

|

|

|

|

|

|||||

.*4234 |

|

|

|

|

|

OBL |

|

|

|

|

66TO 6 |

633 |

||

|

|

|

|

|

|

|

&LASHA H+" |

|

|

|||||

*4$) |

|

|

|

)BUS |

|

|

|

|

|

|

|

|||

#ORTEX - #05 |

|

&LASH INTERFACE |

|

|

|

|

|

|||||||

*4#+ 37#,+ |

|

|

|

BIT |

|

|

6$$ |

|

||||||

*4-3 37$)/ |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

*4$/ |

|

|

|

$BUS |

|

|

|

|

|

|

|

|

||

FMAX -(Z |

|

|

|

|

|

|

0/2 |

3UPPLY |

|

|||||

AS !& |

|

|

|

|

|

|

|

.234 |

||||||

|

|

|

|

|

32!-! |

|

SUPERVISION |

|||||||

|

|

|

|

|

|

|

|

|

|

2ESET |

|

|

6$$! |

|

|

|

|

|

3YSTEM |

"USUMATRIX |

|

|

|

+" |

6$$! |

)NT |

0/2/ 0$2 |

||

|

|

|

|

|

|

|

633! |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

.6)# |

|

|

|

|

|

|

2# (3 |

|

|

06$ |

|

||

|

|

'0 $-! |

|

|

|

|

|

2# ,3 |

6$$! |

|

||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

6$$ |

/3#?). |

|

|

CHANNELS |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

84!, /3# |

/3#?/54 |

||

|

|

|

|

|

|

|

|

|

|

0,, |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

-(Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2ESETS |

0#,+ |

|

)7$' |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

-(Z |

|

CLOCK |

0#,+ |

|

3TANDBY |

|

|

|

|

|

|

|

|

|

|

CONTROL |

(#,+ |

|

INTERFACE |

6"!4 6 TO 6 |

||

|

|

|

|

|

|

|

|

|

,+ |

|

|

|

||

|

%84)4 |

|

|

|

|

|

|

|

|

6"!4 |

|

|||

!& |

|

|

|

|

|

|

|

|

|

|

|

|||

7+50 |

|

|

|

|

|

|

|

|

|

/3# ?). |

||||

|

|

|

|

|

MAX |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

84!, K(Z |

|||

|

'0)/ PORTT! |

|

|

|

|

|

|

|

/3# ?/54 |

|||||

0!; = |

|

|

|

& |

|

|

|

|

|

|

||||

|

|

|

!("( |

|

|

|

|

|

"ACKUP |

|

||||

|

|

|

|

|

|

|

|

|

|

24# |

4!- 0%2 24# |

|||

0"; = |

'0)/ PORTT" |

|

|

|

|

|

|

!75 |

REGISTER |

|||||

|

|

|

|

|

|

!,!2- /54 |

||||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

"ACKUPUINTERFACE |

|

||

0#; = |

'0)/ PORTT# |

|

|

|

|

|

|

|

|

|

|

CHANNELS |

||

|

|

|

|

|

|

!(" |

|

!(" |

|

|

4)- |

|||

0$; = |

|

|

|

|

|

|

|

|

AS !& |

|||||

'0)/ PORTT$ |

|

|

|

|

|

|

|

|||||||

|

|

!0" |

|

!0" |

|

|

|

|

CHANNELS |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

4)- |

||

0%; = |

|

|

|

|

|

|

|

|

|

|

|

AS !& |

||

'0)/ PORTT% |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

(Z |

4)- |

CHANNELS |

|

CHANNELS COMPL |

|

|

|

|

|

|

|

|

|

|

|

|

AS !& |

|

CHANNELNANDE"+). |

4)- |

|

|

|

|

|

|

|

|

- |

|

|

28 48 #43 243 |

|

|

|

|

|

|

|

|

|

|

53!24 |

|||||

AS !& |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

#+ ASA!& |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CHANNEL COMPL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MAX |

53!24 |

28 48 #43 243 |

||

CHANNELNANDE"+). |

4)- |

|

|

|

|

|

|

|

|

|||||

AS !& |

|

|

|

|

|

|

|

|

|

|

& |

|

|

#+ AS !& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

!0" |

|

|

|

|

CHANNEL COMPL |

|

|

|

|

(Z |

|

|

|

|

|

30) |

-/3) 3-)3/ |

||

4)- |

|

|

|

|

|

|

|

3#+ .33 AS.!& |

||||||

CHANNELNANDE"+). |

|

|

|

|

- |

|

|

|

|

|

|

|

|

|

AS !& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

($-) #%# |

($-) #%# AS !& |

||

CHANNELS COMPL |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CHANNELS %42%AND |

4)- |

|

|

MAX |

|

|

|

|

|

|

|

|

|

|

"+). AS.!& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

) # |

3#, 3$! 3-"!3AS !& |

||

|

|

|

|

|

|

|

|

|

|

|

||||

-/3) 3-)3/ |

30) |

|

|

!0" |

|

|

|

|

|

|

) # |

|

||

3#+ .33 AS.!& |

|

|

|

|

|

77$' |

|

|

3#, 3$! 3-"!3AS !& |

|||||

28 48 #43 243 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

53!24 |

|

|

|

|

|

|

|

|

|

|

|

|

||

#+ AS !& |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4EMP SENSOR |

|

|

|

|

|

|

4)- |

|

)& |

BIT $!# |

$!# ?/545AS !& |

||

|

|

|

|

|

|

|

|

|

|

|

)& |

|

|

|

!$# CHANNELS |

BIT !$# |

)& |

|

|

|

|

|

4)- |

|

|

BIT $!# |

$!# ?/54 AS !& |

||

!$#?).X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

62%& |

|

|

|

|

|

|

|

|

|

|

|

|

6$$! |

|

62%&n |

6$$! |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AI B |

1.Peripherals not present in low-density value line devices.

2.AF = alternate function on I/O port pin.

3.TA = –40 °C to +85 °C (junction temperature up to 105 °C) or TA = –40 °C to +105 °C (junction temperature up to 125 °C).

12/86 |

Doc ID 16455 Rev 3 |

STM32F100x4, STM32F100x6, STM32F100x8, STM32F100xB |

|

|

|

|

|

Description |

|||||

Figure 2. |

Clock tree |

|

|

|

|

|

|

|

|

|

|

|

-(Z |

(3) |

|

|

|

|

|

|

|

|

|

|

(3) 2# |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(#,+ |

|

|

|

|

|

|

|

|

-(Z MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

TO !(" BUS CORE |

|||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

#LOCK |

|

|

MEMORY AND $-! |

||

|

|

|

|

|

|

%NABLE |

|

|

TO #ORTEXX3YSTEM TIMER |

||

|

0,,32# |

|

|

37 |

|

|

|

|

|||

|

0,,-5, |

|

|

|

|

|

,+ #ORTEX |

||||

|

|

|

|

|

|

|

|||||

|

|

X |

(3) |

393#,+ |

!(" |

!0" |

|

|

FREE RUNNING CLOCK |

||

|

|

|

|

|

|

|

|||||

|

|

|

-(ZZMAX |

|

0#,+ |

||||||

|

|

X X X |

0,,#,+ |

-(Z |

0RESCALER |

0RESCALER |

|

||||

|

|

|

|

|

|

TO !0" |

|||||

|

|

0,, |

|

|

|

|

|

|

|||

|

|

|

MAX |

0ERIPHERAL #LOCK |

PERIPHERALS |

||||||

|

|

|

(3% |

|

|

||||||

|

|

|

|

|

|

%NABLE |

|

|

|||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

4)- |

|

|

|

TO 4)- AND |

|

|

|

|

|

|

|

)F !0" PRESCALER |

X |

|

|||

|

|

|

|

|

|

|

4)-X#,+ |

||||

|

|

|

|

#33 |

|

|

ELSE SX |

|

|||

|

|

|

|

|

|

0ERIPHERAL #LOCK |

|||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

%NABLE |

|

|

|

|

02%$)6 |

|

|

!0" |

-(Z MAX |

|

0#,+ |

|||

|

|

|

|

|

0RESCALER |

|

|||||

/3#?/54 |

|

|

|

|

|

|

|

PERIPHERALSLTO !0" |

|||

|

|

|

|

|

|

|

|

||||

-(Z |

|

|

|

0ERIPHERAL #LOCK |

|||||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||

/3#?). |

(3%%/3# |

|

|

|

|

|

%NABLE |

TO 4)- 4)- |

|||

|

|

|

|

|

4)- TIMERS |

|

|||||

|

|

|

|

|

|

|

4)- AND 4)- |

||||

|

|

|

|

|

|

)F !0" PRESCALER |

X |

||||

|

|

|

|

|

|

4)-X#,+ |

|||||

|

|

|

|

|

|

|

ELSE X |

||||

|

|

|

|

|

|

|

|

|

0ERIPHERAL #LOCK |

||

|

|

|

|

|

!$# |

|

|

%NABLE |

|

|

|

/3# ?). |

|

|

|

TO 24# |

|

|

|

|

|

TO !$# |

|

,3% /3# |

,3% |

|

|

0RESCALER |

!$##,+ -(Z MAX |

||||||

|

|

|

|||||||||

|

K(Z |

|

24##,+ |

|

|

||||||

/3# ?/54 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24#3%,; == |

|

|

|

|

|

|

|

|

|

|

,3) 2# |

,3) |

TO INDEPENDENT WATCHDOG )7$' |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

K(Z |

|

|

)7$'#,+ |

|

|

|

|

|

|

|

|

-AIN |

|

0,,#,+ |

|

|

,EGEND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

-#// |

CLOCK OUT PUT |

|

|

|

|

(3% (IGH SPEED EXTERNAL CLOCK SIGNAL |

|||||

|

|

(3) |

|

|

(3) (IGH SPEED INTERNAL CLOCKKSIGNAL |

||||||

|

|

|

(3% |

|

|

,3) ,OW SPEED INTERNAL CLOCKKSIGNAL |

|||||

|

|

|

393#,+ |

|

|

,3%% ,OWWSPEED EXTERNAL CLOCKKSIGNAL |

|||||

|

-#/ |

|

|

|

|

|

|

|

|

AI |

|

|

|

|

|

|

|

|

|

|

|

|

|

4. To have an ADC conversion time of 1.2 µs, APB2 must be at 24 MHz.

Doc ID 16455 Rev 3 |

13/86 |