- •1 Лабораторна робота №1 вивичення схем булевих функцій двох змінних

- •1.1 Основні положення

- •1.2 Варіанти індивідуальних завдань

- •1.3 Загальні зауваження до виконання індивідуальних завдань

- •1.4 Порядок виконання роботи

- •1.5 Зміст звіту

- •1.6 Контрольні запитання

- •2 Лабораторна робота №2 комбінаційні схеми

- •2.1 Основні положення

- •2.2 Варіанти індивідуальних завдань

- •2.3 Порядок виконання роботи

- •2.4 Зміст звіту

- •2.5 Контрольні запитання

- •3.1.3 Асинхронні тригери. Тригер типуRs

- •3.1.4 Синхронні тригери, що тактуються імпульсом

- •3.1.5 Синхронний двоступінчастий jk-тригер типу ms

- •3.1.6 Синхронний d-тригер з динамічним керуванням

- •3.1.7 Jk-тригер із внутрішньою затримкою й динамічним керуванням

- •3.1.8 Приклад розгляду схем із тригерами, їхнього аналізу й застосування в ца

- •3.2 Варіанти індивідуальних завдань

- •3.2.1 Аналіз jk-тригера із внутрішньою затримкою й динамічним керуванням

- •3.2.2 Дослідження тригерних схем, побудованих на базі d- і jk- тригерів

- •3.2.3 Дослідження схеми перетворення синхропослідовності у двофазну послідовність на частоті, рівної 1/2f генератора сі

- •3.2.4 Схема формування двох послідовностей імпульсів зі зрушенням на чверть періоду відносно один одного

- •3.2.5 Синхронізатор зовнішнього одиночного імпульсу довільної тривалості

- •3.2.6 Синхронізатор зовнішнього одиночного імпульсу з додатковою функцією генерації пачки імпульсів

- •3.3 Порядок виконання роботи й зміст звіту

- •3.4 Контрольні запитання

- •Лабораторна робота № 4 регістри й лічильники на основі тригерів. Аналіз і синтез

- •4.1 Регістри. Основні положення

- •4.2 Лічильники. Основні положення

- •4.3 Індивідуальні завдання. Дослідження готових імс регістрів і лічильників в інтегральному виконанні

- •4.4 Порядок виконання роботи

- •4.5 Зміст звіту

- •4.5 Контрольні запитання

- •5 Лабораторна робота № 5 аналіз і синтез моделей цифрових автоматів

- •5.1 Основні положення

- •5.1.1 Математичні моделі цифрових автоматів

- •5.1.2 Табличний спосіб завдання ца

- •5.1.3 Канонічний метод синтезу ца

- •5.1.4 Приклад синтезу ца канонічним методом

- •5.1.5 Завдання ца графом

- •5.2 Приклад синтезу ца із «жорсткою» логікою управління

- •5.2.1 Принцип роботи мікропрограмного автомата із жорсткою логікою управління

- •5.2.2 Приклад проектування мікропрограмного автомата із жорсткою логікою управління

- •5.3 Варіанти індивідуальних завдань (із)

- •5.4 Зміст звіту

- •Література

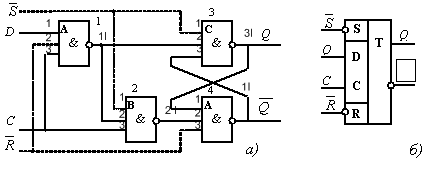

3.1.4 Синхронні тригери, що тактуються імпульсом

Із синхронних тригерів, що тактуються

імпульсом, знайшли застосування два:

RS- іD-тригери. СинхроннийRS-тригер

буде розглянутий нижче в складі

JK-тригера.D-тригер і його функціональний

опис представлені на рис. 3.5. Даний тип

синхронного тригера широко використається

в цифрових пристроях (ІС 155ТМ5, ТМ7 або

SN 7477, 7475). У літературі за цією схемою

вкоренився термінтригер-затвор.

Елементи 3 і 4 схеми утворять комірку

пам’яті (![]()

![]() -тригер),

а елементи 1 і 2 – схему керування.D-тригер сприймає вхідний керуючий

сигнал на входіDтільки при

синхросигналіC=1, переходячи в стан,

запропонованийD-входом (рис. 3.5,г).

Закон функціонування (характеристичне

рівняння) дуже просте:

-тригер),

а елементи 1 і 2 – схему керування.D-тригер сприймає вхідний керуючий

сигнал на входіDтільки при

синхросигналіC=1, переходячи в стан,

запропонованийD-входом (рис. 3.5,г).

Закон функціонування (характеристичне

рівняння) дуже просте:

Qt+1 =Dt. (3.1)

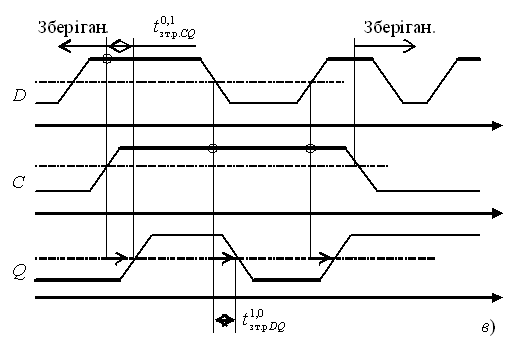

а) схема б) позначення на функціональній схемі в) часові діаграми роботи г) таблиця станів (переходів) тригера д) діаграма, що пояснює часові параметри ts і th

Рисунок 3.5 Синхронний D-тригер

Як видно з часової діаграми роботи рис.

3.5, при C=1Q-вихід повторює сигнал

на входіDіз затримкою, що знайшло

відображення в позначенні входу й типу

тригера:Delay затримка. ПриC=0 на виходах елементів

1 і 2 установлюються неактивні для![]()

![]() -тригера

сигнали (

-тригера

сигнали (![]() =

=![]() =1), обумовлюючи режим зберігання записаної

приC=1 інформації. Оскільки в режим

зберіганняD-тригер переходить за

спадомC-сигналу, є важливим виключити

збій під час цього переходу. Досягається

це тим, що всякі зміни сигналу наD-вході

повинні припинитися за якийсь час до

спадуC-сигналу, що називається часом

передвстановленняts(setup

time) і можуть знову відновитись після

зрізуC-сигналу, але не раніше, ніж

через час витримкиth(hold

time). Орієнтовноts=(1...2),

аts=0,5...1.

Вимога незмінності вхідного(их)

керуючого(их) сигналу(ів) у момент

переходу тригера в стан зберігання

відноситься й до інших типів синхронних

тригерів.

=1), обумовлюючи режим зберігання записаної

приC=1 інформації. Оскільки в режим

зберіганняD-тригер переходить за

спадомC-сигналу, є важливим виключити

збій під час цього переходу. Досягається

це тим, що всякі зміни сигналу наD-вході

повинні припинитися за якийсь час до

спадуC-сигналу, що називається часом

передвстановленняts(setup

time) і можуть знову відновитись після

зрізуC-сигналу, але не раніше, ніж

через час витримкиth(hold

time). Орієнтовноts=(1...2),

аts=0,5...1.

Вимога незмінності вхідного(их)

керуючого(их) сигналу(ів) у момент

переходу тригера в стан зберігання

відноситься й до інших типів синхронних

тригерів.

На рис. 3.5 виділеними лініями показані

також входи

![]() й

й![]() для асинхронної установки тригера в

одиничний (

для асинхронної установки тригера в

одиничний (![]() =0,

=0,![]() =1)

або нульовий (

=1)

або нульовий (![]() =1,

=1,![]() =0)

стан. Дані входи мають більш високий

пріоритет перед синхронними входами

(тобто тими входами, які контролюються

синхросигналомC), тому що блокують

вхідні вентилі 1 і 2 схеми керування.Асинхронні входи називають ще

настановними.

=0)

стан. Дані входи мають більш високий

пріоритет перед синхронними входами

(тобто тими входами, які контролюються

синхросигналомC), тому що блокують

вхідні вентилі 1 і 2 схеми керування.Асинхронні входи називають ще

настановними.

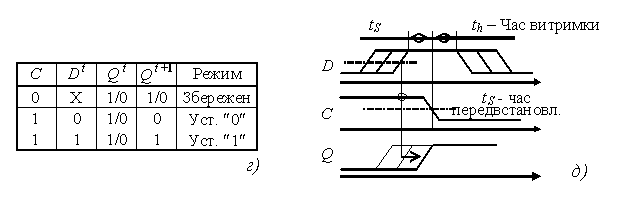

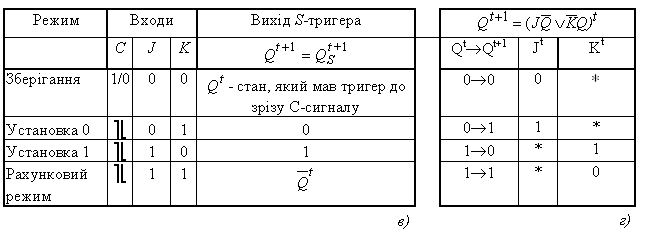

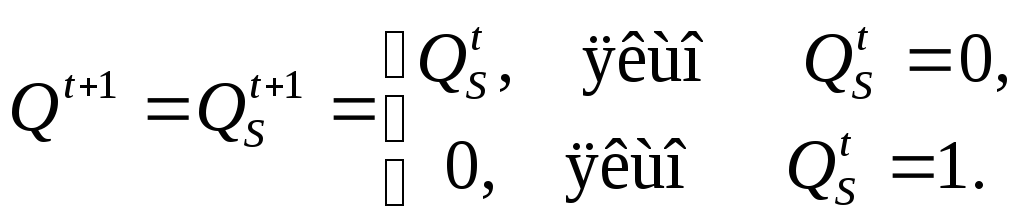

3.1.5 Синхронний двоступінчастий jk-тригер типу ms

JK-тригер типуMSіз додатковою логікою 3І наJ- іK-входах (інтегральна схема типу К155ТВ1* або SN 7472). Функціональне позначення цього тригера наведене на рис. 3.6,а, а його спрощена функціональна модель на елементах І-НІ представлена на рис. 3.6,б. Тригер даного типу складається із двох послідовно включених елементарних тригерів із протифазною синхронізацією. При цьому перший тригер єпровіднимабоM-тригером (master– хазяїн), бо виконує логічну функцію,адругийведеним абоS-тригером (Slave раб, підлеглий). Ведений тригер виконує тільки допоміжну функцію зберігання стану провідного при синхросигналіC=1. РоботуJK-тригера розглянемо за схемою його функціонального аналога рис. 3.6,бу послідовності, що відповідає рядкам таблиці рис. 3.6,в.

При J=K=0 синхросигналC=1 вхідні

елементи 1 і 2 блоковані йM-тригер

перебуває в режимі зберігання. Відзначимо,

що приC=1 (незалежно від стануJ-

іK-входів)S-тригер завжди

перебуває в режимі зберігання, тому що

вхідні кон’юнктури 5, 6 блоковані

інверсним сигналом![]() ,

що становить суть протифазної системи

синхронізації.

,

що становить суть протифазної системи

синхронізації.

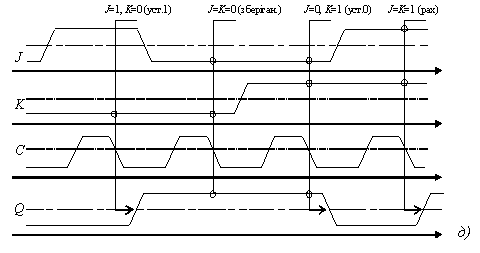

а) зображення на функціональній схемі б) функціональна модель реального JK-тригера в) таблиця функціонування JK-тригера г) таблиця керування переходами JK-тригера д) часові діаграми роботи

Рисунок 3.6 Синхронний JK-тригер типу MS і його функціональний опис

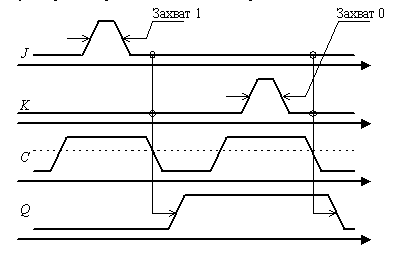

Рисунок 3.7 Діаграми помилкових спрацьовувань JK-тригера SN 7472

При J=0 іK=1 синхросигналомC=1

може бути відкритий лише 2-й елемент і

тільки за умови, що перед надходженнямC-сигналу (тобто коли сигналCдорівнював 0)S-тригер мав "1"

(Qs=1,![]() =0).

Тоді за спадомC-сигналу(C=),

перш ніжM-тригер буде блокований

від впливу вхідних сигналів поJ- іK-входах,S-тригер приймає станM-тригера й буде зберігати0-стан.

Якщо жS-тригер приC=0 був в0-стані, то він так і залишиться в

цьому стані, тому щоM-тригер буде

перебувати в режимі зберігання. Описане

вище, можна відобразити наступним

співвідношенням

=0).

Тоді за спадомC-сигналу(C=),

перш ніжM-тригер буде блокований

від впливу вхідних сигналів поJ- іK-входах,S-тригер приймає станM-тригера й буде зберігати0-стан.

Якщо жS-тригер приC=0 був в0-стані, то він так і залишиться в

цьому стані, тому щоM-тригер буде

перебувати в режимі зберігання. Описане

вище, можна відобразити наступним

співвідношенням

У силу симетрії схеми легко показати, що при J=1 іK=0 буде справедливо

Узагальнюючи розглянуті випадки для J=K=0 іJK,можна дійти висновку, щоJK-тригер поводиться як синхроннийRS-тригер, колиJ-вхід виконує функціюS-входу, аK-вхід – функціюR-входу.

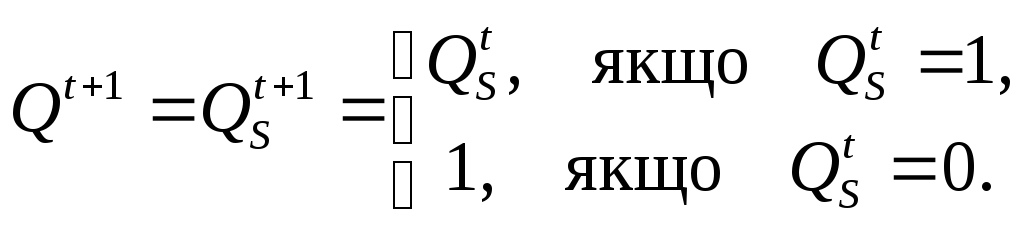

Суттєво відмінним від RS-тригера, є поводженняJK-тригера приJ=K=1. ДляRS-тригера такий стан входів заборонений. У даній же схемі при будь-якому станіS-тригера сигнали оберненого зв’язку відкривають дляC-сигналу саме той вхідний кон’юнктор, пройшовши через якийС-сигнал переведеM-тригер у стан, протилежний стану S-тригера. За спадомC-сигналу (С=)JK-тригер перемінить стан своїх виходів (тобто станS-тригера) на протилежний, реалізуючи рахунковий абоT-режим (toggle- перемикач). ФункціонуванняJK- тригера може бути описано характеристичним рівнянням

![]() , (2.2,)

, (2.2,)

якому відповідає таблиця керування переходами JK-тригера при C=Z (рис. 3.6,г). Дане рівняння може бути перетворене в характеристичне рівнянняT-тригера (приJ=K=T), для якогоT-режим є основним і єдиним:

. (2.3)

Умова J=K=T визначає спосіб перетворення схемиJK-тригера вT-тригер, що і реалізують функцію додавання поmod 2для вхідного й вихідного сигналів тригера.

Часові діаграми роботи JK-тригера, що ілюструють його перемикання при різних сполученнях сигналів на його входах, наведені на рис. 3.6,д.

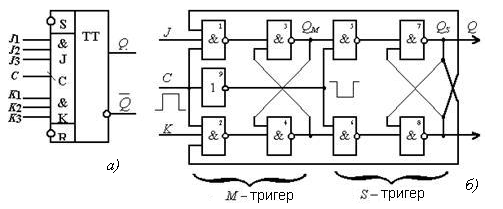

Двоступінчастий синхронний JK-тригер типуMSєнепрозоримдля вхідних сигналівJіKпри будь-якому значенні синхросигналаС.Кожна його щабель сама по собі прозора, але тому що вони включені послідовно, то яка-небудь із них при протифазній синхронізації буде замкнена.Непрозорість– позитивна властивість тригерів. Однак, на відміну відRS- іD-тригерів типуMS(у цій роботі вони не розглядаються),JK-тригер типуMSмає підступну властивість, що одержало назвупроникностідля перешкод по входуJабоK, якщоC=1. Ця властивість відображена на діаграмі рис. 3.7. Нехай тригер перебуває в стані "0" і при цьому J=K=0. У цій ситуації черговийC-сигнал (точніше його спад) не змінить стану тригера. Однак якщо приC=1 наJ-вхід тригера надійде коротка одинична перешкода, то вона, пройшовши через відкритий 1-ий кон’юнктор перемкнеM-тригер у стан "1". Потім за спадомC-сигналуM-тригер передасть свій одиничний (помилковий) стан у другий щабель, тобто на вихід. Це так званий фактзахвата 1JK-тригером. У силу симетрії схеми в ній проявляється й фактзахвата 0. Тому розроблювач, використовуючи тригери даного типу, зобов’язаний забезпечити закінчення всіх перехідних процесів у логічних схемах, що формуютьJ- іK-рівні, ще до початкуC-сигналу. Протягом усього часу, колиC=1, рівні наJ- іK-входах не повинні змінюватися.