- •1 Лабораторна робота №1 вивичення схем булевих функцій двох змінних

- •1.1 Основні положення

- •1.2 Варіанти індивідуальних завдань

- •1.3 Загальні зауваження до виконання індивідуальних завдань

- •1.4 Порядок виконання роботи

- •1.5 Зміст звіту

- •1.6 Контрольні запитання

- •2 Лабораторна робота №2 комбінаційні схеми

- •2.1 Основні положення

- •2.2 Варіанти індивідуальних завдань

- •2.3 Порядок виконання роботи

- •2.4 Зміст звіту

- •2.5 Контрольні запитання

- •3.1.3 Асинхронні тригери. Тригер типуRs

- •3.1.4 Синхронні тригери, що тактуються імпульсом

- •3.1.5 Синхронний двоступінчастий jk-тригер типу ms

- •3.1.6 Синхронний d-тригер з динамічним керуванням

- •3.1.7 Jk-тригер із внутрішньою затримкою й динамічним керуванням

- •3.1.8 Приклад розгляду схем із тригерами, їхнього аналізу й застосування в ца

- •3.2 Варіанти індивідуальних завдань

- •3.2.1 Аналіз jk-тригера із внутрішньою затримкою й динамічним керуванням

- •3.2.2 Дослідження тригерних схем, побудованих на базі d- і jk- тригерів

- •3.2.3 Дослідження схеми перетворення синхропослідовності у двофазну послідовність на частоті, рівної 1/2f генератора сі

- •3.2.4 Схема формування двох послідовностей імпульсів зі зрушенням на чверть періоду відносно один одного

- •3.2.5 Синхронізатор зовнішнього одиночного імпульсу довільної тривалості

- •3.2.6 Синхронізатор зовнішнього одиночного імпульсу з додатковою функцією генерації пачки імпульсів

- •3.3 Порядок виконання роботи й зміст звіту

- •3.4 Контрольні запитання

- •Лабораторна робота № 4 регістри й лічильники на основі тригерів. Аналіз і синтез

- •4.1 Регістри. Основні положення

- •4.2 Лічильники. Основні положення

- •4.3 Індивідуальні завдання. Дослідження готових імс регістрів і лічильників в інтегральному виконанні

- •4.4 Порядок виконання роботи

- •4.5 Зміст звіту

- •4.5 Контрольні запитання

- •5 Лабораторна робота № 5 аналіз і синтез моделей цифрових автоматів

- •5.1 Основні положення

- •5.1.1 Математичні моделі цифрових автоматів

- •5.1.2 Табличний спосіб завдання ца

- •5.1.3 Канонічний метод синтезу ца

- •5.1.4 Приклад синтезу ца канонічним методом

- •5.1.5 Завдання ца графом

- •5.2 Приклад синтезу ца із «жорсткою» логікою управління

- •5.2.1 Принцип роботи мікропрограмного автомата із жорсткою логікою управління

- •5.2.2 Приклад проектування мікропрограмного автомата із жорсткою логікою управління

- •5.3 Варіанти індивідуальних завдань (із)

- •5.4 Зміст звіту

- •Література

5.2.2 Приклад проектування мікропрограмного автомата із жорсткою логікою управління

Завдання на проектування. Розробити синхронний цифровий мікропрограмний автомат із жорсткою логікою управління й переходів станів ЦА в послідовності 0, 7, 9, 11, 13, 0 за сигналами обернених зв’язків із дешифраторів станівDC.

Мікропрограма складається з п’яти мікрокоманд (МК0, МК1, МК2, МК3, МК4), що надходять на виходи автомата у вигляді двійкових паралельних, семирозрядних кодів, що відповідають своєму стану (0 − 0000000, 7 − 0010001, 9 − 0100010, 11 − 1000100, 13 − 1111000).

Установка першої мікрокоманди МК1 здійснюється асинхронно за командою «Пуск» (надходить із зовні), установка в нульовий стан по входу Rздійснює мікрокоманда МК4.

Проектування мікропрограмного автомата почнемо з вибору достатньої кількості елементів пам’яті і їхнього типу.

Число елементів пам’яті визначаємо за розрядністю двійкового коду числа найбільшого стану. У нашому завданні це число 13, що відповідає коду 1101. Для його представлення необхідно, як мінімум, чотири двійкових розряди, що підтверджується загальним співвідношенням 2nM, деM − найбільше число станів автомату;n− найменше число необхідних двійкових розрядів.

Для забезпечення синхронності надходження на вихід мікрокоманд нормального режиму переключення елементів пам’яті (по задньому фронту синхроімпульсу С) і, одночасно, вимоги асинхронного пуску й зупинки циклу, вибираємоJK-тригер. Двоступінчата схема такого триггера (в умовній позначці тригера ставлять дві буквиТ) за своїми властивостями забезпечує виконання цих вимог.

Інформаційний вхід сигналу J=1 тригера служить для переключення його зі стану 0 у стан 1, вхідК=1 служить для установки в стан 0. Переключення по сигналахJабоKвідбувається синхронно по задньому фронту синхроімпульсуС. Інверсні асинхронні входиSіRпризначені для установки тригера поSв 1, а поRв 0 без прив’язки до синхроімпульсів.

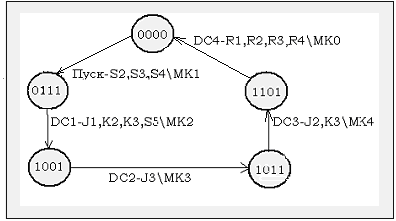

Рисунок 5.7 – Граф автомата ЖЛУ

Для реалізації комбінаційної частини дешифратора, побудуємо граф станів мікропрограмного автомата. На рисунку 5.7 представлений граф переходів мікропрограмного автомата із жорсткою логікою управління.

На дугах графа позначають найменування сигналу, за яким здійснюється перехід із попереднього стану в наступний. Через « − » записані входи елементів пам’яті, на які ці сигнали надходять, щоб зробити відповідні переключення. Через « \ » записані мікрокоманди, що надходять на вихід мікропрограмного автомата в цей момент часу.

Для синтезу дешифраторів DC, складемо таблицю відповідності, використовуючи стани графа зображеного на рисунку 4.7.

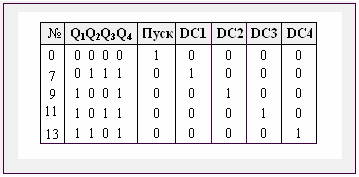

Складемо таблицю 5.8 відповідності і визначимо логічні функції для дешифраторів обернених зв’язків керування DC1,DC2,DC3,DC4.

![]() ;

;

![]() ;

;

![]() ;

;

![]() .

.

Схеми дешифраторів будуємо за ЛФ, використовуючи логічні схеми кон’юнкції на чотири входи. Виходи елементів пам’яті Qiвводимо через зв’язки 1, 2, ..., 8 у шину і потім розводимо на відповідніDC. Виходи дешифраторів вводимо через зв’язки 1, 2, 3, 4 у шину обернених зв’язків, а потім виводимо їх на входи елементів пам’яті, визначенні графом автомата. Якщо по якому-небудь входу потрібно подати кілька сигналів (у нас по входуК3), то це реалізуємо за допомогою логічних елементів АБО.

Таблиця 5.8 – Відповідність сигналів DC стану автомата

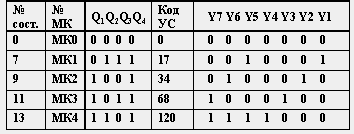

Для синтезу комбінаційної схеми шифратора, складемо таблицю відповідності його роботи, використовуючи виходи Qi елементів пам’яті й коди мікрокоманд МKi.

За таблицею 5.9 отримаємо систему логічних функцій шифратора. Проведемо мінімізацію цих функцій за допомогою карт Карно. При мінімізації будемо враховувати, що з 16 станів у даному автоматі використовують тільки 5. Інші не визначені, тобто, у цьому випадку не реалізується 11 станів. Значення функцій для цих станів можуть визначатися нами й, тому, вони можуть бути використані в картах Карно при мінімізації. З таблиці 5.9 запишемо функції виходу та проведемо мінімізацію.

Таблиця 5.9 Таблиця роботи шифратора

![]()

![]() ;

;

![]() ;

;

![]() ;

;

![]() ;

;

![]() ;

;

![]() .

.

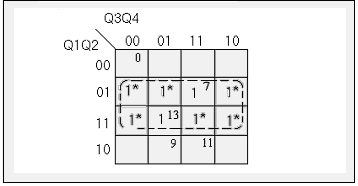

Для прикладу, мінімізуємо функцію Y5,задану на рисунку 4.8 картою Карно для чотирьох зміннихQ1Q2Q3Q4.

Рисунок 5.8 – Карта Карно функції Y5 шифратора

У верхньому правому куті кліток позначені стани, використані автоматом. Клітки позначені 1* − це невизначені стани, які використовують при мінімізації функцій.

По аналогії з прикладом рисунку 4.8 проводимо мінімізацію всіх логічних функцій автомата.

За отриманими мінімальними функціями будуємо схему мікропрограмного автомата з жорсткою логікою управління (рис. 5.6).