- •Стадии проектирования вычислительных систем

- •Определение рабочей нагрузки проектируемой системы

- •Канонический метод проектирования вс

- •1. Стадия разработки технического предложения

- •2. Стадия эскизного проекта

- •2.1. Определение базовой конфигурации вс

- •2.1.1. Типовые структуры базовых конфигураций вс

- •2.1.2. Определение параметров устройств минимальной конфигурации

- •2.1.3. Выбор центрального процессора (вычислительных элементов)

- •2.1.4. Выбор контроллеров (элементов массовой памяти — эмп)

- •2.1.5. Выбор накопителей

- •2.1.6. Выбор числа терминалов

- •2.1.7. Выбор числа линий связи для систем телеобработки и сетей

- •2.1.8. Выбор элементов для систем на транспьютерах

- •Накопители в транспьютерных системах используются стандартные, и их подбор осуществляется обычным образом.

- •2.2. Проверка выполнения ограничений на характеристики для базовой конфигурации вс

- •2.2.1. Проверка корректности ограничения на стоимость

- •2.2.2. Проверка корректности ограничения на время

- •2.3. Типовые структуры вычислительных систем на базе ibm pc и транспьютеров

- •2.3.1. Вычислительные комплексы

- •2.3.2. Системы с телекоммуникационным доступом

- •2.3.3. Локальные сети

- •3. Оценка характеристик базовой конфигурации вс

- •Модель линии связи и аппаратура передачи данных (апд) для встд и лвс

- •Модели остальных устройств вс

- •Модель вычислительной системы в целом

- •4. Оценка характеристик вычислительной системы с помощью моделей

- •4.1. Параметры модели

- •4.2. Определение характеристик вс с помощью модели

- •5. Оптимизация структуры вс

- •6. Аналитические методы синтеза вс

- •6.1. Задача синтеза соо при ограничении на стоимость

- •Где n интенсивность потока заявок на входе n ной смо;

- •6.2. Задача синтеза вс при ограничении на время ответа

- •7. Стадия технического проекта

- •Pсбойij (1pсбоя)pij .

- •Библиографический список

- •Приложение 2. Параметры рабочей нагрузки

- •Параметры задач, решаемых системой

- •Трудоемкости задач и число обращений к файлам

- •Параметры файлов

- •Оглавление

2.2.2. Проверка корректности ограничения на время

Суммарное время обслуживания средней задачи всеми устройствами системы (без учета ожидания в очередях к этим устройствам) является минимально возможным временем ответа. Оно определяется по формуле

tmin= ,

,

где tn- время обслуживания задачи устройствомn-ного типа, которое определяется так:

а) для процессора: tЦПр=vЦПр*HЦПр,

где vЦПр=0/ВЦПр,0— трудоемкость непрерывного счета,

ВЦПр — быстродействие процессора;

б) для контроллера (шины, канала): tконтр=vконтр*D;

в) для ВЗУ: tВЗУ=![]() ;

;

г) для линий связи в ВСТД и ЛВС: tЛС=vЛС*Q.

Если ограничение на время U* > tmin, то оно задано корректно. Иначе нужно либо перейти на более производительный тип базовой ЭВМ, либо увеличить значениеU*, напримерU*= (1.5 - 2) *tmin.

2.3. Типовые структуры вычислительных систем на базе ibm pc и транспьютеров

Рассмотрим возможные варианты структур вычислительных систем всех четырех типов на базе IBM PC и транспьютеров. Минимальная конфигурация предполагает использование в ВС не более двух процессоров. Поэтому все приводимые ниже структуры будут, в основном, двухпроцессорными.

2.3.1. Вычислительные комплексы

Как известно, они бывают с общей памятью (МПВК) и со смешанной памятью (ММВК). В МПВК обычно используются однотипные процессоры и модули памяти.

Персональные компьютеры, как правило, не очень приспособлены к объединению в комплексы. Но имеющиеся в них последовательные порты позволяют строить комплексы с общей внешней памятью (ММВК). Для построения МПВК необходимо изготавливать заказные микросхемы сети связи между процессорами и модулями памяти. Мы рассмотрим структуру таких комплексов на примере двух ЭВМ (процессоров). Ее можно расширить на любое количество ЭВМ (процессоров), добавляя соответствующие средства сопряжения (порты, входы микросхемы и линии).

МПВК на основе IBM PC могут иметь архитектуру, представленную на рис. 2.10. Микросхема сети связи может обеспечивать полносвязный интерфейс или иметь матричную структуру. Ее стоимость близка к стоимости процессора.

ММВК на основе IBM PC могут быть построены с использованием последовательного интерфейса между соответствующими портами. Таких портов в одном компьютере может быть до 8 штук, что позволяет получать комплекс на соответствующем числе процессоров. При этом обеспечивается доступ любого процессора к ВЗУ других компьютеров. Структура ММВК на двух IBM PC представлена на рис. 2.11.

ШИНА

1

ШИНА

n

Рис. 2.10. Многопроцессорный комплекс на IBM PC:

К - контроллеры винчестера или ГМД

Рис. 2.11. Многомашинный комплекс на IBM PC

МПВК на основе транспьютеров строятся довольно просто, с использованием традиционной транспьютерной сети. Причем, по возможности, желательно на одной плате (в одном модуле). Типовая структура МПВК на двух ВЭ будет иметь вид, представленный на рис. 2.12.

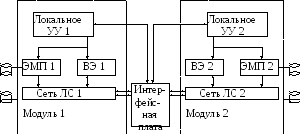

Особенностью транспьютерных систем является их принципиально однородная структура, ориентированная на построение матричных архитектур, сходных с МПВК. Будем считать, что ММВК на основе транспьютеров строятся на двух и более платах (модулях), соединенных интерфейсной платой, выполняющей функции локального резидентного контроллера. Интерфейсная плата обеспечивает обмен как в телефонной сети и работает как коммутатор (мультиплексор). Она имеет до 16 соединителей (входов) и обеспечивает скорость передачи 1.25 Мбайт/с с защитой от ошибок. Плат может быть несколько. Стоимость одной платы равна 100$. Структура ММВК на основе транспьютеров приведена на рис. 2.13.

Рис.

2.12.

Многопроцессорный комплекс на

транспьютерах

Рис. 2.13. Типовая структура ММВК на основе транспьютеров