Архангелский Справочное пособие по ПСпице и Десигн Центер 1996

.pdf

Генератор логических сигналов для цифровых схем (продолжение)

Параметр TIMESTEP=<величина> определяет величину шага (цикла) в секундах. Здесь под шагом подразумевается некоторая единица измерения времени, которая может использоваться в дальнейших операторах для записи временных соотношений. Например, TIMESTEP=10ns означает, что в дальнейшем можно измерять время в шагах (циклах), т.е. в десятках наносекунд.

Перейдем теперь к главной части оператора - к разделу <программа задания сигналов>. Основой программы являются команды вида

<время> <значение вектора сигналов> .

В этой команде <время> - момент, в который вектор сигналов принимает значение, указанное в команде. <значение вектора сигналов> записывается в соответствии с определенными ранее форматами (см. примеры). А <время> может измеряться или в секундах, или в шагах (циклах), определенных параметром TIMESTEP. Если время задается в шагах, то после числа пишется суффикс "С" (cycle). Если же время задается в секундах, то пишется суффикс "S" или масштабные суффиксы "NS", "MS" и т.п. Перед числом, обозначающим

время, может ставиться знак "+" - это означает, что задан не момент, а отрезок времени, который должен прибавляться к текущему времени. Значения времени в последовательных командах должны строго возрастать, в частности, не должно быть двух событий, относящихся к одному моменту времени.

Помимо указанной основной команды в программе могут использоваться команды:

1)<LABEL=<имя метки>>

2)<<время> GOTO <имя метки> <N> TIMES>

3)<<время> GOTO <имя метки> UNTIL GT <значение>

4)<<время> GOTO <имя метки> UNTIL GE <значение>

5)<<время> GOTO <имя метки> UNTIL LT <значение>

6)<<время> GOTO <имя метки> UNTIL LE <значение>

7)<<время> INCR BY <значение>

8)<<время> DECR BY <значение>

Первая из них задает метку точке программы, в которую можно передать управление. Команды 2 - 6 передают управление на метку. Причем команда LABEL должна быть записана до команды GOTO. Команда GOTO передает управление не на саму метку, а на оператор, следующий за меткой, причем команда, записанная в этом операторе, выполняется немедленно, независимо от указанного в ней времени.

6. Некоторые сообщения программы PSpice |

211 |

Генератор логических сигналов для цифровых схем (окончание)

Команда 2 осуществляет безусловную передачу управления N раз, после чего перестает выполняться. Таким образом, петля команд от LABEL до GOTO выполняется N+1 раз (один раз при первом проходе и N раз при возвратах). Если задано N=-1, то возвраты на метку повторяются неограниченное число раз, т.е. моделируется периодический сигнал с неограниченным числом периодов.

Команды 3 - 6 осуществляют условные передачи управления. При этом вектор выходных сигналов сравнивается с параметром <значение>. Команда 3 передает управление, если вектор сигналов > <значение>, команда 4 - если ≥, команда 5 - если <, команда 6 - если ≤.

Команда 7 осуществляет сложение вектора сигналов с параметром <значение>, а команда 8 вычитает из вектора параметр <значение>.

Теперь рассмотрим второй формат оператора. Он читает сигналы из внешнего текстового файла, выбирая из него сигналы с именами, перечисленными в списке. Формат файла следующий:

[TIMESTEP=<значение>] <список имен> пустая строка [+]<время> <значения сигналов>

В списке имен сигналы разделяются запятыми или пробелами. В строке не более 300 символов. Продолжение списка - символ “+” в строке продолжения. Перед группой из трех имен может стоять OCT - восьмеричный формат или HEX - шестнадцатиричный. Символ “+” перед временем означает, что далее следует значение не момента времени, а приращения. Приведем пример файла:

A B OCT(C3 C2 C1) HEX(D4 D3 D2 D1)

0 |

0 1 0 0 |

10n |

1 1 5 F |

+2n |

1 0 4 3 |

...................

212 |

6. Некоторые сообщения программы PSpice |

DIGIFPWR |

Подсхема источника питания |

DIGIFPWR - ПОДСХЕМА ИСТОЧНИКА ПИТАНИЯ

Пояснения

В PSpice 5 принято, что источник питания описан подсхемой с именем DIGIFPWR, и на эту подсхему автоматически делается ссылка в подсхемах аналого-цифровых интерфейсов. Текст подсхемы DIGIFPWR включается в библиотеку цифровых устройств.

Например, простая подсхема источника питания может иметь вид:

SUBCKT DIGIFPWR AGND

+OPTIONAL DPWR=$G_DPWR DGND=$G_DGND

+PARAMS V=5V VGND=0V

VP DPWR DGND {V}

VG DGND AGND {VGND} R1 DPWR AGND 10MEG R2 DGND AGND 10MEG

.ENDS DIGIFPWR

В этом описании задаются глобальные узлы питания и земли $G_DPWR и $G_DGND для цифровых элементов. AGND - узел земли аналоговой части схемы. Параметр V задает напряжение питания, а параметр VGND - разность напряжений между “аналоговой” и “цифровой” землей.

6. Некоторые сообщения программы PSpice |

213 |

ADC |

Аналого цифровой преобразователь |

ADC - АНАЛОГО ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Форма оператора

U<имя> ADC(<число разрядов>) <список узлов> <модель задержек>

+<модель входа/выхода>

+[MNTYMXDLY=<уровень>] [IO_LEVEL=<уровень>] ,

где <список узлов> для PSpice 4: <входной узел ><опорный узел> <земля>

+<узел сигнала разрешения> <узел запуска>

+<узел сигнала переполнения> <узел старшего разряда> ...

+<узел младшего разряда>

для PSpice 5: <узел питания +> <узел питания -> <входной узел>

+<опорный узел> <земля> <узел сигнала разрешения>

+<узел запуска> <узел сигнала переполнения>

+<узел старшего разряда> ... <узел младшего разряда>

Форма описания модели задержек

.MODEL <имя модели> UADC [<(параметры модели)>]

Пример

N1 ADC(4) UP UM SIG REF 0 CONV START OVRNG OUT3 OUT2 OUT1 OUT0 + ADCMDL IO_STD

.MODEL ADCMDL (TPCSTY=10ns TPSDTY=0 TPDSTY=5ns)

Пояснения

Входной аналоговый сигнал Uвх подается между узлами <входной узел> и <земля>. Входное сопротивление между этими узлами равно 1/GMIN, где GMIN определяется оператором .OPTIONS (см. в разделе 2). По умолчанию GMIN=10-12.

Между узлами <опорный узел> и <земля> подается опорное напряжение Uоп, определяющее диапазон преобразования. Выходной сигнал АЦП равен ближайшему целому от величины

UUопвх 2M ,

где M - разрядность АЦП. Если эта величина больше, чем 2M -1, то все разряды выходных данных и сигнал переполнения равны “1”. Если Uвх и Uоп не совпадают

214 |

6. Некоторые сообщения программы PSpice |

ADC |

Аналого цифровой преобразователь (окончание) |

по знаку, то все разряды выходных данных равны “0”, а сигнал переполнения равен

“1”.

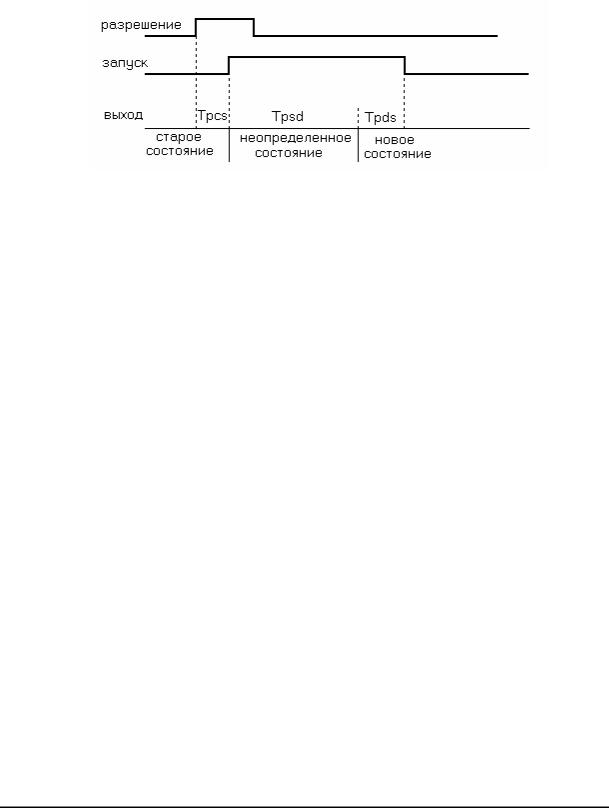

Входы разрешения и запуска являются логическими. Диаграмма сигналов имеет следующий вид :

Выборка входного напряжения производится по переднему фронту импульса разрешения. Его длительность может быть любой, в частности, и нулевой. Преобразование начинается по переднему фронту импульса запуска и длится на протяжении времени Tpsd. Время преобразования Tpsd может быть задано нулевым. В этом случае преобразование осуществляется сразу, без промежуточного неопределенного состояния. Импульс запуска должен поступать через время задержки Tpcs после импульса разрешения и длиться в течение времени Tpds после окончания преобразования.

Параметры модели задержек

имя |

параметр |

|

размерность |

умолчание |

|

|

|

|

|

TPCSMN |

задержка между передними фронтами |

с |

|

0 |

|

импульсов разрешения и запуска |

|

|

|

|

(минимальное значение) |

|

|

|

TPCSTY |

то же (типовое значение) |

с |

|

0 |

TPCSMX |

то же (максимальное значение) |

с |

|

0 |

TPSDMN |

время преобразования (минимальное |

с |

|

0 |

|

значение) |

|

|

|

TPSDTY |

то же (типовое значение) |

с |

|

0 |

TPSDMX |

то же (максимальное значение) |

с |

|

0 |

TPDSMN |

задержка между выходным сигналом и |

с |

|

0 |

|

задним фронтом запуска (минимальное |

|

|

|

|

значение) |

|

|

|

TPDSTY |

то же (типовое значение) |

с |

|

0 |

TPDSMX |

то же (максимальное значение) |

с |

|

0 |

6. Некоторые сообщения программы PSpice |

215 |

DAC |

Цифро-аналоговый преобразователь |

DAC - ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

Форма оператора

U<имя> DAC(<число разрядов>) <список узлов> <модель задержек>

+<модель входа/выхода>

+[MNTYMXDLY=<уровень>] [IO_LEVEL=<уровень>] ,

где <список узлов> для PSpice 4:

<выходной узел ><опорный узел> <земля>

+<узел старшего разряда> ... <узел младшего разряда>

для PSpice 5:

<узел питания +> <узел питания -> <выходной узел>

+<опорный узел> <земля>

+<узел старшего разряда> ... <узел младшего разряда>

Форма описания модели задержек

.MODEL <имя модели> UDAC [<(параметры модели)>]

Пример

N1 DAC(4) UP UM SIG REF 0 IN3 IN2 IN1 IN0 DACMDL IO_STD

.MODEL DACMDL (TSWTY=10ns)

Параметры модели задержек

имя |

параметр |

|

размерность |

умолчание |

|

|

|

|

|

TSWMN |

задержка переключения |

с |

|

0 |

|

(минимальное значение) |

|

|

|

|

|

|

|

|

TSWTY |

то же (типовое значение) |

с |

|

0 |

|

|

|

|

|

TSWMX |

то же (максимальное значение) |

с |

|

0 |

|

|

|

|

|

216 |

6. Некоторые сообщения программы PSpice |

DAC |

Цифро-аналоговый преобразователь (окончание) |

Пояснения

Модель ЦАП преобразует логические сигналы на входах разрядов в сигнал аналогового напряжения Uвых между узлами <выходной узел > и <земля>. Выходное сопротивление равно нулю. Между узлами <опорный узел> и <земля>

должно подключаться напряжение Uоп, определяющее масштаб преобразования. Входное сопротивление модели между этими узлами равно 1/GMIN, где GMIN определяется оператором .OPTIONS (см. в разделе 2). По умолчанию GMIN=10−12.

Выходной сигнал Uвых равен Uоп (двоичный входной сигнал)/2M . Если какиенибудь разряды входных сигналов имеют неопределенное состояние “X”, то выходной сигнал равен среднему между значением Uвых в случае, если все “X” заменить на “1”, и значением Uвых в случае, если все “X” заменить на “0”.

Переходный процесс на выходе представляет собой линейно изменяющееся во времени напряжение в течение заданной задержки переключения Tsw. Переключение начинается в момент изменения входных сигналов.

6. Некоторые сообщения программы PSpice |

217 |

Стандартные вентили

СТАНДАРТНЫЕ ВЕНТИЛИ

В данном пункте рассмотрены вентили с двумя состояниями, сборки вентилей, составные вентили.

Форма оператора

U<имя> <тип вентиля> [(<параметры>)]

+<<узел питания +> <узел питания ->>5) <узлы входов> <узлы выходов>

+<модель задержек> <модель входа/выхода>

5)- только для PSpice 5

Форма описания модели задержек

.MODEL <имя модели> UGATE [(<параметры модели>)]

Примеры

1) U5 AND(2) IN0, IN1, OUT, MDL, IO_STD 2) U2 INV 1, 2, MDL, IO_STD

3) U10 NANDA(2,4) INA1 INA0 INB1 INB0 INC1 INC0 IND1 IND0 + OUTA OUTB OUTC OUTD MDL IO_STD

.MODEL MDL UGATE (TPLHTY=10ns TPHLTY=15ns MNTYMXDLY=2)

Пояснения

Вентили представлены в двух видах: одиночные вентили и сборки (массивы) вентилей. Одиночный вентиль имеет один или несколько входов (Nвх) и один выход. Сборки вентилей состоят из одного или более (Mв) одинаковых вентилей. Соответственно сборка имеет Nвх Mв входов и Mв выходов. Использование сборок позволяет работать непосредственно со стандартными элементами интегральных схем, имеющими часто в одном корпусе несколько вентилей.

Помимо одиночных вентилей и сборок вентилей имеются еще составные элементы. Они содержат Mв вентилей первого уровня, выходы которых подключены к единственному вентилю второго уровня. Каждый из вентилей первого уровня имеет Nвх входов. Вентиль второго уровня имеет Mв входов. Выход вентиля второго уровня является единственным выходом составного вентиля.

218 |

6. Некоторые сообщения программы PSpice |

Стандартные вентили (продолжение)

Выходной сигнал вентиля имеет силу D и равен “0”, “1”, или “X”. Неопределенное состояние “X” появляется только в тех случаях, когда какие-то из входных сигналов равны “X”, причем состояние выхода при замене “X” на “0” и на “1” различно. Таким образом, наличие неопределенного состояния на входе еще не означает неопределенного состояния выхода. Например, для элемента И на два входа таблица истиности имеет вид:

|

“0” |

“1” |

“X” |

“0” |

“0” |

“0” |

“0” |

“1” |

“0” |

“1” |

“X” |

“X |

“0” |

“X” |

“X” |

” |

|

|

|

|

|

|

|

Порядок перечисления узлов в операторе описания для всех вентилей одинаков: сначала перечисляются входы, затем выходы. В случае сборок вентилей сначала перечисляются все входы первого вентиля, затем входы второго и т.д.; затем перечисляются выход первого вентиля, выход второго и т.д. Порядок перечисления узлов составных вентилей: входы первого вентиля, входы второго вентиля, ..., выход.

|

|

Типы стандартных вентилей |

|

|

|

|

|

тип |

параметры |

|

описание |

|

|

|

|

BUF |

0 |

|

Буфер |

|

|

|

|

INV |

0 |

|

Инвертор |

|

|

|

|

AND |

Nвх |

|

И |

NAND |

Nвх |

|

И-НЕ |

|

|

|

|

OR |

Nвх |

|

ИЛИ |

|

|

|

|

NOR |

Nвх |

|

ИЛИ-НЕ |

XOR |

0 |

|

Исключающее ИЛИ |

|

|

|

|

NXOR |

0 |

|

Исключающее ИЛИ-НЕ |

6. Некоторые сообщения программы PSpice |

219 |

Стандартные вентили (окончание)

Типы стандартных вентилей (окончание)

тип |

параметры |

|

описание |

|

|

||

BUFA |

Mв |

|

Сборка буферов |

|

|

|

|

|

|

|

|

|

|

|

|

INVA |

Mв |

|

Сборка инверторов |

|

|

|

|

|

|

|

|

|

|

|

|

ANDA |

Nвх, Mв |

|

Сборка элементов И |

|

|

|

|

NANDA |

Nвх, Mв |

|

Сборка элементов И-НЕ |

|

|

|

|

|

|

|

|

|

|

|

|

ORA |

Nвх, Mв |

|

Сборка элементов ИЛИ |

|

|

|

|

|

|

|

|

|

|

|

|

NORA |

Nвх, Mв |

|

Сборка элементов ИЛИ-НЕ |

|

|

||

XORA |

Mв |

|

Сборка элементов ислючающее ИЛИ |

|

|

||

|

|

|

|

|

|

|

|

NXORA |

Mв |

|

Сборка элементов исключающее ИЛИ-НЕ |

|

|||

AO |

Nвх, Mв |

|

Составной элемент И-ИЛИ |

|

|

||

OA |

Nвх, Mв |

|

Составной элемент ИЛИ-И |

|

|

||

|

|

|

|

|

|

|

|

AOI |

Nвх, Mв |

|

Составной элемент И-ИЛИ-НЕ |

|

|

||

OAI |

Nвх, Mв |

|

Составной элемент ИЛИ-И-НЕ |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Параметры модели задержек |

|

|

||

|

|

|

|

|

|

|

|

имя |

|

|

|

параметр |

размерность |

умолчание |

|

|

|

|

|

|

|

||

TPLHMN |

|

задержка переключения “0” → “1” |

с |

0 |

|

||

|

|

(минимальное значение) |

|

|

|

||

|

|

|

|

|

|

||

TPLHTY |

|

то же (типовое значение) |

с |

0 |

|

||

TPLHMX |

|

то же (максимальное значение) |

с |

0 |

|

||

|

|

|

|

|

|

||

TPHLMN |

|

задержка переключения “1” → “0” |

с |

0 |

|

||

|

|

(минимальное значение) |

|

|

|

||

|

|

|

|

|

|

||

TPHLTY |

|

то же (типовое значение) |

с |

0 |

|

||

TPHLMX |

|

то же (максимальное значение) |

с |

0 |

|

||

|

|

|

|

|

|||

MNTYMXDL |

тип задержки: 0 - умолчание, |

- |

0 |

|

|||

Y |

|

1 - мин, 2 - типовая, 3 - макс |

|

|

|

||

|

|

|

|

|

|

|

|

220 |

6. Некоторые сообщения программы PSpice |