- •ВВЕДЕНИЕ

- •Последний пример иллюстрирует применение смешанного формата, в котором сигналы узлов 1, 2 и 7 описаны в двоичном формате, а узлы 3, 4, 5, 6 - в шестнадцатеричном.

- •USTIM STIM(7,1141) 1 2 3 4 5 6 7 IO_STM

- •4.1. ОБЩИЕ СВЕДЕНИЯ

- •4.2. ДИОДЫ

- •4.3. БИПОЛЯРНЫЕ ТРАНЗИСТОРЫ

- •4.4. ПОЛЕВЫЕ ТРАНЗИСТОРЫ

- •4.5. МДП ТРАНЗИСТОРЫ

- •4.6. ОПЕРАЦИОННЫЕ УСИЛИТЕЛИ

- •4.7. КОМПАРАТОРЫ НАПРЯЖЕНИЯ

- •4.8. МОДЕЛЬ МАГНИТНОГО СЕРДЕЧНИКА

МИФИ |

|

Московский государственный инженерно-физический институт |

|

|

(технический университет) |

||

|

УЧЕБНО - МЕТОДИЧЕСКИЙ КОМПЛЕКС МЕТОДИКА АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ ИНТЕГРАЛЬНЫХ СХЕМ И ЭЛЕКТРОННОЙ АППАРАТУРЫ

НА ПЕРСОНАЛЬНЫХ КОМПЬЮТЕРАХ ЧАСТЬ 1

СХЕМОТЕХНИЧЕСКОЕ ПРОЕКТИРОВАНИЕ

АРХАНГЕЛЬСКИЙ А. Я.

PSPICE И DESIGN CENTER

ЧАСТЬ 2

МОДЕЛИ ЦИФРОВЫХ И АНАЛОГО-ЦИФРОВЫХ УСТРОЙСТВ

ИДЕНТИФИКАЦИЯ ПАРАМЕТРОВ МОДЕЛЕЙ

ГРАФИЧЕСКИЕ РЕДАКТОРЫ

2 |

ОДЕРЖАНИЕ |

ГОСУДАРСТВЕННЫЙ КОМИТЕТ РОССИЙСКОЙ ФЕДЕРАЦИИ ПО ВЫСШЕМУ ОБРАЗОВАНИЮ

__________________________________________________________________________________________

_

МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ (ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ)

_________________________________________________________

УЧЕБНО-МЕТОДИЧЕСКИЙ КОМПЛЕКС МЕТОДИКА АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ ИНТЕГРАЛЬНЫХ СХЕМ И ЭЛЕКТРОННОЙ АППАРАТУРЫ

НА ПЕРСОНАЛЬНЫХ КОМПЬЮТЕРАХ ЧАСТЬ 1

СХЕМОТЕХНИЧЕСКОЕ ПРОЕКТИРОВАНИЕ

А. Я. АРХАНГЕЛЬСКИЙ

PSpice и Design Center

Ч а с т ь 2

МОДЕЛИ ЦИФРОВЫХ И АНАЛОГО-ЦИФРОВЫХ УСТРОЙСТВ.

ИДЕНТИФИКАЦИЯ ПАРАМЕТРОВ МОДЕЛЕЙ.

ГРАФИЧЕСКИЕ РЕДАКТОРЫ

Рекомендовано к изданию редсоветом института в качестве учебного пособия

Москва 1996

УДК 621.382.82.001

А

Архангельский А.Я. PSpice и Design Center. В 2-х ч. Часть 1. Модели цифровых и аналого-цифровых устройств. Идентификация параметров моделей. Графические редакторы. Учебное пособие. М., МИФИ, 1996, 212 с.

Пособие является частью учебно-методического комплекса “Методика автоматизированного проектирования интегральных схем и электронной аппаратуры на персональных компьютерах. Часть 1. Схемотехническое проектирование” и выходит в двух частях. В учебном пособии рассмотрена методика схемотехнического моделирования с помощью пакетов программ PSpice и Design Center различных версий:

от PSpice 4 до Design Center 6.0 и 6.2.

В первой части пособия были приведены сведения о входном языке, о различных видах анализа, об основных моделях элементов. Подробно рассмотрены способы построения макромоделей аналоговых электронных устройств. Дана методика решения различных задач схемотехнического проектирования..

Во второй части пособия приведена методика моделирования цифровых и аналогоцифровых устройств. Рассмотрены графические редакторы, предназначенные для обработки результатов моделирования и для изображения принципиальных и логических схем. Изложены сведения об идентификации параметров моделей элементов. Даны различные вспомогательные программы. Изложение методики проектирования опирается на справочный материал, содержащийся в справочном пособии, входящем в комплекс.

Пособие предназначено для студентов радиотехнических и других смежных специальностей (электроника, микроэлектроника, вычислительная техника, автоматика и т.п.), связанных с разработкой электронной аппаратуры, средств автоматики и вычислительной техники. Может быть полезно также для аспирантов, инженеров и исследователей соответствующих специальностей.

Рецензент проф. МАИ, зав.каф. САПР В.Н. Ильин.

ISBN 5-7262-0010-1 |

© А.Я. Архангельский, 1996 |

||

|

|||

|

2304030000 − 012 |

|

© Московский государственный |

А |

без объявл. |

инженерно-физический институт |

|

|

1К 9(03) − 96 |

(технический университет), 1996 |

|

4 ОДЕРЖАНИЕ

|

СОДЕРЖАНИЕ |

Предисловие ..................................................................................... |

|

|

5 |

1. Моделирование цифровых схем ............................................... |

|

|

6 |

1 |

Модели цифровых элементов ................................................ |

.1. |

6 |

1 |

Задержки срабатывания элементов ....................................... |

.2. |

9 |

1 |

Сила выходных сигналов элементов ...................................... |

.3. |

12 |

1 |

Логические примитивы цифровых элементов ........................ |

.4. |

14 |

|

1.4.1. Логические вентили, их сборки и матрицы ................... |

|

14 |

|

1.4.2. Триггеры ...................................................................... |

|

20 |

|

1.4.3. Запоминающие устройства .......................................... |

|

23 |

|

1.4.4. Линии задержки и контроллеры ................................... |

|

26 |

|

1.4.5. Источники логических сигналов ................................... |

|

29 |

2. Моделирование аналого-цифровых схем ............................... |

|

|

36 |

2 |

Алгоритмы смешанного моделирования ................................ |

.1. |

36 |

2 |

Подготовка аналого-цифровой схемы к расчету ..................... |

.2. |

39 |

2 |

Аналого-цифровые интерфейсы ............................................ |

.3. |

49 |

|

2.3.1. Интерфейсный элемент ............................................... |

|

49 |

|

2.3.2. Подсхемы аналого-цифровых интерфейсов ................. |

|

55 |

2 |

Цифро-аналоговые интерфейсы ............................................ |

.4. |

58 |

|

2.4.1. Интерфейсный элемент ............................................... |

|

58 |

|

2.4.2. Подсхемы цифро-аналоговых интерфейсов ................. |

|

63 |

2 |

Цифро-аналоговые и аналого-цифровые преобразователи .... |

.5. |

66 |

3. Графический постпроцессор PROBE и графический редактор

входных сигналов STMED ........................................

3 |

Запуск PROBE на счет |

69 |

|

||

.1. |

|

69 |

3 |

Обозначения переменных и математические функции PROBE |

|

.2. |

|

71 |

3 |

Начальные меню PROBE ....................................................... |

|

.3. |

|

77 |

3 |

Построение графиков в PROBE .............................................. |

|

.4. |

|

79 |

3 |

Исследования и измерения графиков в PROBE ...................... |

|

.5. |

|

88 |

3 |

Редактор входных сигналов STMED для MS DOS ................... |

|

.6. |

|

97 |

3. Редактор STMED в Design Center 6 ....................................... |

|

|

7. |

|

106 |

4. Идентификация параметров моделей с помощью программы PARTS |

111 |

|

...................................................................... |

|

|

4 |

Общие сведения .................................................................... |

1 |

.1. |

|

11 |

4 |

Диоды |

1 |

.2. |

|

18 |

4 |

Биполярные транзисторы |

1 |

.3. |

|

23 |

4 |

Полевые транзисторы |

1 |

.4. |

|

32 |

4 |

МДП транзисторы |

1 |

.5. |

|

37 |

4 |

Операционные усилители |

1 |

.6. |

|

42 |

4 |

Компараторы напряжения |

1 |

.7. |

|

48 |

4 |

Модель магнитного сердечника ............................................. |

1 |

.8. |

|

52 |

5. Оболочка PSpice для MC DOS. Графический ввод схем с помощью |

|

|

внешних редакторов ................................................ |

1 |

|

|

|

54 |

5 |

Управляющяя оболочка PSpice .............................................. |

1 |

.1. |

|

54 |

5 |

Графический ввод схем в PSpice внешними редакторами ..... |

1 |

.2. |

|

58 |

|

5.2.1. Графический редактор PCCAPS пакета P-CAD ............. |

1 |

|

|

59 |

|

5.2.2. Графический редактор DRAFT пакета OrCAD ................ |

1 |

5 |

Включение внешних графических редакторов в оболочку |

78 |

|

||

.3. |

PSpice ................................................................................... |

1 |

|

|

80 |

6 |

ОДЕРЖАНИЕ |

|

6. Оболочка Design Center для Windows ..................................... |

1 |

|

|

|

84 |

6 |

Общее описание .................................................................... |

1 |

.1. |

|

84 |

6 Ввод принципиальных и логических схем и их расчет ............ |

1 |

|

.2. |

|

88 |

6 Разработка символов библиотечных элементов ..................... |

2 |

|

.3. |

|

00 |

Литература ........................................................................................ |

2 |

|

|

|

08 |

ВВЕДЕНИЕ

Издание “Pspice и Design Center”, посвященное широко распространенным пакетам схемотехнического проектирования, состоит из двух частей. В первой части были представлены входной язык программ моделирования, модели электронных компонентов, методика построения макромоделей аналоговых устройств. В данной второй части рассматривается методика моделирования цифровых и аналого-цифровых устройств, графические редакторы, предназначенные для обработки результатов моделирования и для изображения принципиальных и логических схем. Приводятся сведения об идентификации параметров моделей элементов. Предлагаются различные вспомогательные программы.

Рассматриваются различные версии PSpice и Design Center: от PSpice 4 до Design Center 6. Особенности последней версии Design Center 6.2 и, в частности, программы PLogic в пособии представлены не будут. Обзор некоторых возможностей Design Center 6.2 приведен в первой части пособия. А особенности PLogic будут изложены во второй части учебнометодического комплекса, посвященной логическому проектированию цифровых схем.

1. М О Д Е Л И Р О В А Н И Е Ц И Ф Р О В Ы Х С Х Е М

1.1. МОДЕЛИ ЦИФРОВЫХ ЭЛЕМЕНТОВ

PSpice и Design Center - это прежде всего программы схемотехнического моделирования. Однако, в них реализована возможность и логического моделирования не очень сложных цифровых схем. Правда, в PSpice это возможно только, если в поставленной версии имеется опция Digital Simulation, что требует наличия соответствующих файлов .OVL и библиотек.

ВDesign Center эта опция включена всегда.

ВPSpice 4 осуществляется трехзначное моделирование: логические сигналы могут принимать следующие значения:

“1” - высокий уровень; “0” - низкий уровень;

“X” - неопределенное состояние.

ВPSpice 5 и, соответственно, в Design Center алфавит расширен и в него добавлено еще 2 значения:

“R” - переход “0”→“1” (положительный фронт); “F” - переход “1”→“0” (отрицательный фронт).

Логическим сигналам может быть приписана сила. Сила сигнала используется в случаях, когда к одному узлу подключено несколько выходов логических элементов. Тогда значение сигнала в этом узле соответствует тому сигналу, который имеет большую силу. Если несколько сигналов имеют одинаковую силу, то результирующий сигнал будет неопределенным. Сила сигнала определяется выходными сопротивлениями, задаваемыми в описанных далее моделях входа/выхода.

В PSpice определены стандартные имена узлов, соответствующих постоянным уровням логических сигналов (табл. 1.1).

|

Таблица 1.1 |

|

|

Имя узла |

Уровень |

|

|

1.1. Модели цифровых элементов |

9 |

||

|

|

|

|

|

|

|

$D_HI |

|

“1” |

|

|

|

$D_LO |

|

“0” |

|

|

|

$D_X |

|

“X” |

|

|

|

$D_NC |

|

не определен |

|

|

Узлы $D_HI, $D_LO, $D_X поддерживают соответствующие уровни независимо от того, что к ним подключено. Узел $D_NC используется для подключения к нему выходов цифровых элементов, которые не используются в моделируемой схеме.

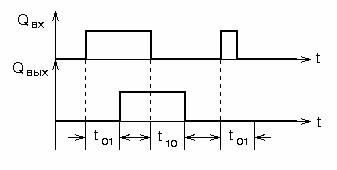

Расчет по постоянному току в цифровых схемах не проводится. В нулевой момент времени все логические сигналы считаются равными “X”. При расчете переходных процессов учитываются задержки цифровых элементов. В простейшем случае задержка - отрезок времени между появлением входного сигнала элемента и изменением его выходного сигнала. Пока не прошло время задержки, заданное

для переключения “0”→“1” или |

|

||

“1”→“0”, выходной сигнал не |

|

||

меняется (на рис. 1.1 реакция на |

|

||

длинный импульс), хотя элемент |

|

||

помнит пришедшее возбуждение. |

|

||

Если же |

длительность входного |

|

|

сигнала |

меньше |

длительности |

|

соответствующей |

задержки, то |

Рис. 1.1. Реакция цифрового элемента |

|

возбуждение гасится и сигнал на |

|||

выходе вообще не появляется (см. |

на длинный и короткий входной сигнал |

||

на рис. 1.1 реакцию на короткий импульс). Таким образом моделируется свойственная реальным логическим элементам фильтрация коротких импульсов. Наличие в схеме таких коротких импульсов обычно расценивается как логический сбой.

Задержка в цифровом элементе складывается из двух составляющих:

-внутренняя задержка самого элемента, обусловленная переходными процессами в его внутренних узлах;

-задержка в выходном каскаде, связанная с перезарядкой емкости

нагрузки Cн через выходное сопротивление элемента.

Внутренняя задержка имеет фиксированную величину для данного элемента. А задержка на выходе зависит от нагрузочной емкости, которая в свою очередь определяется тем, сколько других элементов подключено к тому же

выходному |

узлу. |

Cн |

в |

общем |

случае |

равна |

Cн = Cвых + Cм |

+ ∑Cвх. i |

+ ∑Cвых. j , |

где Cвых |

- выходная |

емкость |

|

|

i |

j |

|

|

|

|

10 |

1. Моделирование цифровых схем |

элемента, Cм - емкость межсоединений на выходе элемента, индекс i относится к цифровым элементам, входы которых подключены к выходу данного элемента (т.е. к нагрузочным элементам), а индекс j - к элементам, выходы которых включены параллельно выходу данного элемента (если таковые имеются в схеме). Таким образом, емкость Cн зависит от схемы включения элемента. Задержка в выходном каскаде считается равной Rвых Cн ln(2) 0,69 Rвых Cн, где Rвых - выходное сопротивление цифрового элемента. Суммарную емкость программа подсчитывает автоматически, исключая, конечно, емкость Cм, которая должна быть включена искусственно или в выходную емкость элемента, или как фиктивный цифровой элемент, подключенный к данному узлу.

Моделирование ведется с помощью библиотеки логических примитивов, имеющихся в программе. Каждый цифровой элемент, из которых состоит моделируемая схема, описывается оператором U, имеющим в PSpice 4 при чисто цифровом моделировании вид:

U<имя> <тип примитива> [(<параметры>)] <узлы элемента>

+<модель задержек> <модель входа/выхода>

+[MNTYMXDLY=<уровень>]

ВPSpice 5 этот оператор имеет несколько другой вид:

U<имя> <тип примитива> [(<параметры>)]

+<<узел питания +> <узел питания ->> <узлы элемента>

+<модель задержек> <модель входа/выхода>

+[MNTYMXDLY=<уровень>]

Данная форма оператора отличается от предыдущей наличием в ней узлов питания. Эти узлы имеют смысл только для смешанного моделирования аналого-цифровых устройств. А при чисто цифровом моделировании имена этих узлов могут указываться произвольными (например, UP, UM) и к ним ничего не надо подключать.

Как видно из приведенных описаний, элемент характеризуется типом используемого примитива, определяющего логическую функцию, узлами подключения, моделью задержек и моделью входа/выхода. Кроме того, для некоторых примитивов предусмотрены определенные параметры. Например, оператор

U1 AND(2) UP UM IN0 IN1 OUT MDL IO_STD

1.1. Модели цифровых элементов |

11 |

описывает элемент И с двумя входами, подключенными к узлам IN0 и IN1, с выходом, подключенным к узлу OUT, с моделью задержек по имени MDL и с моделью входа/выхода IO_STD.

Каждый тип примитива определяется ключевым словом, список которых дается в описании библиотеки в п. 1.4. Для каждого примитива в описании библиотеки приводится также смысл передаваемых в него параметров (обычно это число разрядов элемента), ключевое слово, определяющее его модель внутренних задержек, смысл и имена параметров модели задержек.

1.2.ЗАДЕРЖКИ СРАБАТЫВАНИЯ ЭЛЕМЕНТОВ

Вмодели задержек для каждой внутренней задержки могут указываться три значения: минимальное, типовое и максимальное. Таким образом, можно рассчитывать схему, учитывая разброс задержек. Задавать, какие значения внутренних задержек должны использоваться - минимальные, типовые или максимальные, можно тремя способами. Во-первых, имеется опция DIGMNTYMX, задаваемая оператором .OPTIONS и определяющая тип задержек, принимаемый по умолчанию: 1 - минимальные значения, 2 - типовые, 3 - максимальные. Если эта опция не задана, то ее значение по умолчанию равно 2, т.е. по умолчанию берутся типовые задержки. Второй способ задания типа задержек - указание параметра MNTYMXDLY в конкретной модели задержек. Этот параметр может принимать значения: 0 - умолчание (т.е. тип задержек определяется опцией DIGMNTYMX), 1 - минимальные задержки, 2 - типовые, 3 - максимальные. Таким образом, параметр MNTYMXDLY может отменять действие опциии DIGMNTYMX для данной модели задержек. И третий путь указания типа задержек - задание MNTYMXDLY в операторе U, описанном выше. При этом значения параметра MNTYMXDLY означают: 0 - используется величина MNTYMXDLY, заданная в модели задержек (это значение MNTYMXDLY принято по умолчанию), 1 - используются минимальные значения задержек, 2 - типовые, 3 - максимальные. Таким образом предоставляется возможность задать для данного элемента задержки, отличные от задержек других элементов, использующих ту же модель.

Например, описание модели задержек с именем MDL следующего вида

.MODEL MDL UGATE (TPLHMN=5ns TPHLMN=10ns TPLHTY=10ns + TPHLTY=15ns TPLHMX=15ns TPHLMX=20ns MNTYMXDLY=2)

задает для задержки переключения из “0” в “1” минимальное значение 5 нс, типовое - 10 нс, максимальное - 15 нс. Для задержки переключения из “1” в

12 |

1. Моделирование цифровых схем |

“0” соответствующие значения равны 10, 15 и 20 нс. Поскольку задан параметр MNTYMXDLY=2, то для расчета выбираются типовые значения задержек. Но если описание элемента, использующего данную модель, имеет вид

U1 AND(2) UP UM IN0, IN1, OUT, MDL, IO_STD, MNTYMXDLY=1,

то для этого элемента будут использоваться минимальные значения задержек. Если же ни в описании элемента, ни в описании модели задержек не указано значение MNTYMXDLY или задано MNTYMXDLY=0, то значения задержек будут определяться опцией DIGMNTYMX. Например, если задан оператор

.OPTIONS DIGMNTYMX=3,

то будут использоваться максимальные значения задержек. Наконец, если и этой опции не задано, то ее значение по умолчанию равно 2 и при расчетах будут использоваться средние значения задержек.

Если в модели задержек не описаны все три варианта задержек: минимальный, типовой и максимальный, то недостающие варианты рассчитываются программой самостоятельно, исходя из значений коэффициентов DIGMNTYSCALE и DIGTYMXSCALE, первый из которых равен отношению минимальной задержки к типовой, а второй - отношению максимальной задержки к типовой. Коэффициенты DIGMNTYSCALE и DIGTYMXSCALE задаются оператором .OPTIONS. По умолчанию

DIGMNTYSCALE=0.4, а DIGTYMXSCALE=1.6, т.е. по умолчанию разброс задержек равен ± 60 % от типового значения. Например, если задано только типовое значение задержки, равное 10 нс, то по умолчанию максимальное значение данной задержки будет считаться равным 16 нс, а минимальное - 4 нс. Если задано только максимальное значение задержки, равное 10 нс (обычно для цифровых элементов именно максимальные значения задержек приводятся в справочниках), то типовое значение по умолчанию будет считаться равным 6.25 нс (максимальное, деленное на DIGTYMXSCALE), а минимальное - 2.5 нс (типовое, умноженное на DIGMNTYSCALE). Исключением из этого правила является случай, когда заданы минимальное и максимальное значения, а типового не задано. В этом случае программа примет в качестве типовой задержки величину, среднюю между минимальной и максимальной.

По умолчанию все задержки считаются равными нулю. Поэтому, если в модели не указаны значения никаких задержек, проводится синхронное

1.2. Задержки срабатывания элементов |

13 |

моделирование. Такой вид моделирования позволяет оценить только правильность алгоритма функционирования схемы, но не дает возможности проверить наличие сбоев, происходящих из-за неодновременного прихода сигналов на вход какого-либо элемента.

Модели задержек для часто используемых цифровых элементов обычно заносятся в библиотеку и тогда пользователю не приходится задумываться о значениях задержек. Достаточно просто указать имя соответствующей библиотечной модели.

Модель задержек определяет внутренние задержки элемента. Задержки в выходном каскаде, как указывалось выше, зависят от числа нагрузок и от значений входных и выходных импедансов элемента, задававемых в модели входа/выхода. Оператор, определяющий модель входа/выхода имеет вид

.MODEL <имя модели> UIO [(параметры модели)].

К числу параметров модели входа/выхода, используемых при логическом моделировании, относятся:

INLD |

- |

входная емкость в фарадах (по умолчанию 0); |

|

OUTLD |

|

- |

выходная емкость в фарадах (по умолчанию 0); |

DRVH |

- выходное сопротивление высокого уровня в омах (по |

||

|

|

умолчанию 0 для PSpice 4 и 50 Ом для PSpice 5) |

|

DRVL |

- |

выходное сопротивление низкого уровня в омах (по умолчанию |

|

|

|

0 для PSpice 4 и 50 Ом для PSpice 5). |

|

Пример описания модели входа/выхода:

.MODEL IO_STD UIO (DRVH=96.4, DRVL=104, INLD=0.1pf, +OUTLD=0.5pf).

Заданные значения емкостей и сопротивлений используются программой для подсчета суммарных емкостей в узлах и для расчета задержек в выходных каскадах цифровых элементов по приведенным ранее соотношениям.

При работе с моделями серийно выпускаемых цифровых элементов возникают проблемы, связанные с тем, что в справочных данных приводятся значения полных задержек, включающих в себя как внутренние задержки, так и задержки в выходных каскадах. Решить эти проблемы можно двумя путями. Первый и наиболее простой заключается в том, что справочное значение задержки приравнивается к внутренней задержке элемента. В этом случае в модели входа/выхода следует задать INLD=OUTLD=0 (или вообще не задавать INLD и OUTLD, так как по умолчанию эти емкости равны нулю). Преимуществом такого подхода является то, что в библиотеке моделей

14 |

1. Моделирование цифровых схем |

PSpice значения задержек будут совпадать со справочными, что естественно для пользователя. Однако при этом отключается механизм учета зависимости задержки от числа нагрузок элемента, что снижает адекватность моделирования. Другой подход - выделение из справочных данных внутренней задержки. Это возможно только если известны (или хотя бы могут быть примерно оценены) значения выходных сопротивлений и входных и выходных емкостей. Тогда из справочного значения задержки tспр можно выделить внутреннюю задержку tвн, воспользовавшись соотношением

tвн=tспр-Rвых (Cвых+M Cвх) ln(2),

где M - нагрузочная способность элемента (число нагрузок, для которого приведено значение tспр).

Модели входа/выхода так же, как и модели задержек для часто используемых цифровых элементов обычно заносятся в библиотеку. Тогда пользователю не приходится задумываться о значениях задаваемых в них параметров. Достаточно просто указать имя соответствующей библиотечной модели.

1.3. СИЛА ВЫХОДНЫХ СИГНАЛОВ ЭЛЕМЕНТОВ

Задаваемые в моделях входа/выхода значения сопротивлений используются также для определения силы сигнала, которая, как указывалось выше, влияет на разрешение конфликтов при работе нескольких выходов элементов на один узел. В PSpice 4 приняты следующие силы сигналов (они перечисляются в порядке убывания силы и сопровождаются условными трактовками их смыслового значения):

F |

- |

сила внешних генераторов сигналов и источников питания; |

D |

- |

сила выходов вентилей; |

W - |

сила нагрузочных сопротивлений; |

|

Z |

- |

высокоомное состояние. |

Считается, что F > D > W > Z. Значения выходных сопротивлений DRVH и DRVL, соответствующие различным силам сигнала, определяются пороговыми функциями с порогами DIGSTRF, DIGSTRD, DIGSTRW, задаваемыми в операторе .OPTIONS. Соотношения, определяющие Rвых, приведены в табл. 1.2, а значения порогов по умолчанию - в табл. 1.3.

Таблица 1.2

Условие для Rвых |

Сила сигнала |

|

|

|

|

1.3. Сила выходных сигналов элементов |

15 |

||||

|

|

|

|

|

|

|

|

|

Rвых < DIGSTRF |

|

F |

|

|||

|

DIGSTRF ≤ Rвых < DIGSTRD |

|

D |

|

|||

|

DIGSTRD ≤ Rвых < DIGSTRW |

W |

|

||||

|

Rвых ≥ DIGSTRW |

|

Z |

|

|||

|

|

|

|

|

Таблица 1.3 |

|

|

|

|

|

|

|

|

|

|

|

|

Параметр |

|

Умолчание, Ом |

|

||

|

|

|

|

|

|

|

|

|

|

DIGSTRF |

|

10 |

|

|

|

|

|

DIGSTRD |

|

100 |

|

|

|

|

|

DIGSTRW |

|

10 000 |

|

|

|

Задавая разные значения DRVH и DRVL, можно приписать разные силы различным уровням выходного сигнала. В приведенном ранее примере заданы DRVH=96,4, DRVL=104. Тогда при значениях опций по умолчанию высокий уровень имеет силу D (DIGSTRF<DRVH<DIGSTRD), а низкий - W (DIGSTRD<DRVL<DIGSTRW). Если же задан оператор

.OPTIONS DIGSTRD=200,

то для обоих уровней сила будет равна D.

В PSpice 5 и, соответственно, в Design Center сила сигнала определяется более дробной шкалой. Считается, что сила сигналов различна, если выходные сопротивления их источников различаются по крайней мере в DIGOVRDRV раз, а величина DIGOVRDRV задается в операторе .OPTIONS. По умолчанию DIGOVRDRV=3. Таким образом, в приведенном выше примере, в котором DRVL и DRVH различались всего в 1,08 раз, сила сигналов “0” и “1” будет считаться одинаковой, если только не задать DIGOVRDRV меньшим, чем 1,08. Конечно, решение считать одинаковой силу сигналов с мало различающимися выходными сопротивлениями более оправдано, чем пороговые функции в PSpice 4. Сопротивления DRVH и DRVL могут задаваться в пределах от DIGDRVF до DIGDRVZ. Эти параметры задаются оператором .OPTIONS и по умолчанию равны DIGDRVF=2 Ом, DIGDRVZ=20 кОм. Впрочем, это ограничение действует только при смешанном моделировании аналого-цифровых схем, которое будет описано позднее.

1.4. ЛОГИЧЕСКИЕ ПРИМИТИВЫ ЦИФРОВЫХ ЭЛЕМЕНТОВ

16 |

1. Моделирование цифровых схем |

ВPSpice имеется множество встроенных примитивов цифровых элементов, из которых и набирается моделируемая схема. Использование аппарата подсхем позволяет формировать из этих примитивов описания более сложных цифровых устройств и применять такие подсхемы как элементы при описании схемы.

Полный список примитивов и их описание приведены в работе [2]. В п. 1.4 дадим только краткий обзор возможностей библиотеки логических примитивов PSpice.

1.4.1.ЛОГИЧЕСКИЕ ВЕНТИЛИ, ИХ СБОРКИ И МАТРИЦЫ

Вбиблиотеке имеется множество вентилей с двумя состояниями. Их список приведен в табл. 1.4. Вентили представлены в двух видах: одиночные вентили и сборки (массивы) вентилей. Одиночный вентиль имеет один или

несколько входов (Nвх) и один выход. Сборки вентилей состоят из одного или более (Mв) одинаковых вентилей. Соответственно сборка имеет Nвх Mв входов и Mв выходов. Использование сборок позволяет работать непосредственно со стандартными элементами интегральных схем, имеющими часто в одном корпусе несколько вентилей.

Помимо одиночных вентилей и сборок вентилей имеются еще составные элементы. Они содержат Mв вентилей первого уровня, выходы которых подключены к единственному вентилю второго уровня. Каждый из вентилей первого уровня имеет Nвх входов. Вентиль второго уровня имеет Mв входов. Выход вентиля второго уровня является единственным выходом составного вентиля.

Выходной сигнал вентиля имеет силу D и равен “0”, “1”, или “X”. Неопределенное состояние “X” появляется только в тех случаях, когда какието из входных сигналов равны “X”, причем состояние выхода при замене “X” на “0” и на “1” различно. Таким образом, наличие неопределенного состояния на входе еще не означает

|

|

|

|

|

1.4. Логические примитивы цифровых элементов |

17 |

||

|

|

|

|

|

|

Таблица 1.4 |

|

|

|

|

|

|

|

|

Типы вентилей |

|

|

|

|

|

|

|

|

|

||

|

Тип |

Параметры |

|

Описание |

|

|||

|

|

|

|

|

|

|

|

|

|

BUF |

0 |

|

|

|

Буфер |

|

|

|

INV |

0 |

|

|

|

Инвертор |

|

|

|

AND |

NВХ |

|

|

|

И |

|

|

|

NAND |

NВХ |

|

|

|

И-НЕ |

|

|

|

OR |

NВХ |

|

|

|

ИЛИ |

|

|

|

NOR |

NВХ |

|

|

|

ИЛИ-НЕ |

|

|

|

XOR |

0 |

|

|

|

Исключающее ИЛИ |

|

|

|

NXOR |

0 |

|

|

|

Исключающее ИЛИ-НЕ |

|

|

|

BUFA |

MВ |

|

|

|

Сборка буферов |

|

|

|

INVA |

MВ |

|

|

|

Сборка инверторов |

|

|

|

ANDA |

NВХ, MВ |

|

Сборка элементов И |

|

|

||

|

NANDA |

N |

, M |

В |

|

Сборка элементов И-НЕ |

|

|

|

|

ВХ |

|

|

|

|

|

|

|

ORA |

NВХ, MВ |

|

Сборка элементов ИЛИ |

|

|

||

|

NORA |

NВХ, MВ |

|

Сборка элементов ИЛИ-НЕ |

|

|

||

|

XORA |

MВ |

|

|

|

Сборка элементов исключающее ИЛИ |

|

|

|

NXORA |

MВ |

|

|

|

Сборка элементов исключающее ИЛИ-НЕ |

|

|

|

AO |

NВХ, MВ |

|

Составной элемент И-ИЛИ |

|

|

||

|

OA |

NВХ, MВ |

|

Составной элемент ИЛИ-И |

|

|

||

|

AOI |

NВХ, MВ |

|

Составной элемент И-ИЛИ-НЕ |

|

|

||

|

OAI |

NВХ, MВ |

|

Составной элемент ИЛИ-И-НЕ |

|

|

||

неопределенного состояния выхода. Например, для элемента И на два входа таблица истинности имеет вид:

“0” |

“0” |

“1” |

“X” |

“0” |

“0” |

“0” |

|

“1” |

“0” |

“1” |

“X” |

“X |

“0” |

“X” |

“X” |

” |

|

|

|

Порядок перечисления узлов в операторе описания для всех вентилей одинаков: сначала перечисляются входы, затем выходы. В случае сборок вентилей сначала перечисляются все входы первого вентиля, затем входы второго и т.д.; затем перечисляются выход первого вентиля, выход второго и

18 |

1. Моделирование цифровых схем |

т.д. Порядок перечисления узлов составных вентилей: входы первого вентиля, входы второго вентиля, ..., выход.

Тип модели задержек вентилей - UGATE. Модель содержит значения задержек переключения “0” → “1” и “1” → “0”.

Приведем примеры описания схем, состоящих из вентилей. Инвертор с входным сигналом IN и выходным OUT может иметь описание

U2 INV UP UM IN OUT MDL IO_STD .

Двухвходовой элемент 2И-НЕ может быть описана оператором

U1 NAND(2) UP UM IN1 IN2 OUT MDL IO_STD .

Микросхема 155ЛА12, состоящая из четырех двухвходовых элементов 2ИНЕ, может быть представлена следующим образом:

U1 NANDA(2, 4) UP UM INA1 INA2 INB1 INB2 INC1 INC2 IND1 IND2 + OUTA OUTB OUTC OUTD MDL IO_STD .

Элемент, состоящий из трех двухвходовых элементов 2И, объединенных по выходам элементом ИЛИ-НЕ, может быть описан оператором:

U2 AOI(2, 3) UP UM INA1 INA2 INB1 INB2 INC1 INC2 OUT + MDL IO_STD .

Помимо вентилей с двумя состояниями имеются вентили и сборки вентилей с тремя состояниями. Кроме обычных входов и выхода они имеют еще вход разрешения. Если сигнал на этом входе равен нулю, то сигнал на выходе равен “X” с силой Z и не зависит от состояния других входов. Если же сигнал разрешения равен “1” или “X”, то состояние выхода определяется логикой работы вентиля и сигналами на его входах. При этом выходной сигнал вентиля имеет силу D и равен “0”, “1” или “X”. Неопределенное состояние “X” появляется только в тех случаях, когда какие-то из входных сигналов равны “X”, причем состояние выхода при замене “X” на “0” и на “1” различно. Таким образом, наличие неопределенного состояния на входе еще не означает неопределенного состояния выхода. Например, для элемента И на два входа A и B со входом разрешения C и выходом D таблица истинности имеет вид, представленный в табл. 1.5.

|

|

1.4. Логические примитивы цифровых элементов |

19 |

||

|

|

|

|

Таблица 1.5 |

|

|

Таблица истиности элемента И на два входа с разрешением |

|

|||

|

|

|

|

|

|

|

A |

B |

C |

D (уровень/сила) |

|

|

“0” “1” “X” |

“0” |

“1” “X” |

“0” / D |

|

|

“0” |

“0” “1” “X” |

“1” “X” |

“0” / D |

|

|

“1” |

“1” |

“1” “X” |

“1” / D |

|

|

“X” |

“1” “X” |

“1” “X” |

“X” / D |

|

|

“1” “X” |

“X” |

“1” “X” |

“X” / D |

|

|

“0” “1” “X” |

“0” “1” “X” |

“0” |

“X” / Z |

|

Одиночный вентиль с тремя состояниями имеет вход разрешения, один или несколько сигнальных входов и один выход. Сборки вентилей состоят из нескольких одинаковых вентилей. При этом сборка имеет один вход разрешения, действующий на выходы сразу всех вентилей.

Порядок перечисления узлов в операторе описания для всех вентилей одинаков: сначала перечисляются сигнальные входы, после вход разрешения, затем выходы. В случае сборок вентилей сначала перечисляются все входы первого вентиля, далее входы второго и т.д.; затем указывается вход разрешения; после этого перечисляются выход первого вентиля, выход второго и т.д.

Имена вентилей и сборок с тремя состояниями те же, что приведены в табл. 1.4, но с добавлением цифры 3 после описания функции: BUF3, INV3, AND3,

... , BUF3A, INV3A, AND3A, ..., NXOR3A.

Тип модели задержек вентилей с тремя состояниями - UTGATE. Помимо задержек переключения “0” → “1” и “1” → “0” модель содержит задержки

“0” → “Z”, “Z” → “0”, “1” → “Z”, “Z” → “1”.

В PSpice 5 и, соответственно, в Design Center, помимо логических вентилей и их сборок, имеются программируемые логические матрицы ПЛМ. Оператор, описывающий ПЛМ, имеет формат:

U<имя> <тип ПЛМ> (<число входов>, <число выходов>)

+<узел питания +> <узел питания -> <узлы входов> <узлы выходов>

+<модель задержек> <модель входа/выхода>

+[FILE=<имя файла>]

+[DATA=<символ системы счисления>$<данные программы>$]

+[MNTYMXDLY=<уровень>]

Допустимые типы ПЛМ приведены в табл. 1.6.

ПЛМ представляют собой матрицы логических элементов одного типа и имеют ряд входов, составляющих столбцы матрицы, и ряд выходов, образующих строки. К каждому выходу подключен выход одного

20 |

1. Моделирование цифровых схем |

логического элемента. Управляющие сигналы определяют программу работы ПЛМ, т.е. какие входы соединяются с логическими элементами.

В операторе, описывающем ПЛМ, программа может быть задана двумя способами: или спецификацией FILE, определяющей имя файла, содержащего программу в формате JEDEC, или спецификацией DATA, после которой следует программа.

Если используется спецификация FILE, то <имя файла> задается или текстовой константой, заключенной в кавычки “ ”, или текстовым выражением, заключенным в вертикальные черточки ||. Например,

UD2X4 PLANDC(2,4) UP UM X1 X2 Q1 Q2 Q3 Q4 PLD_MDL IO_STD + FILE=“D2X4.JED”

При наличии спецификации FILE спецификация DATA игнорируется, даже если она присутствует в операторе.

Если отсутствует спецификация FILE, то программа задается спецификацией DATA. После ключевого слова DATA указывается <символ системы счисления>: B - двоичная, O - восьмеричная, X - шестнадцатеричная. Затем между знаками $ записывается программа. Она может писаться слитно или разделяться в любых местах пробелами для удобства понимания и контроля. Программа начинается с символа соединения первого входа с элементом, управляющим первым выходом. Символ “0” означает, что вход не подключен к элементу, а символ “1” - что подключен. Далее для матриц без входов дополнительного кода следует описание соединения второго входа с первым элементом и т.д. Для матриц со входами прямого и дополнительного кода входы перебираются попарно: первый вход прямого кода, первый вход дополнительного кода, второй вход прямого кода и т.д. После того, как все входы перебраны, аналогичным образом программируется соединение входов со вторым элементом и т.д.

|

|

1.4. Логические примитивы цифровых элементов |

21 |

|

|

|

Таблица 1.6 |

|

|

|

|

Типы ПЛМ |

|

|

|

|

|

|

|

|

Тип |

Описание матрицы |

|

|

|

|

|

|

|

|

PLAND |

И |

|

|

|

PLOR |

ИЛИ |

|

|

|

PLXOR |

исключающее ИЛИ |

|

|

|

PLNAND |

И-НЕ |

|

|

|

PLNOR |

ИЛИ-НЕ |

|

|

|

PLNXOR |

исключающее ИЛИ-НЕ |

|

|

|

PLANDC |

И со входами прямого и дополнительного кода |

|

|

|

PLORC |

ИЛИ со входами прямого и дополнительного кода |

|

|

|

PLXORC |

исключающее ИЛИ |

|

|

|

|

со входами прямого и дополнительного кода |

|

|

|

PLNAND |

И-НЕ со входами прямого и дополнительного кода |

|

|

|

C |

|

|

|

|

PLNORC |

ИЛИ-НЕ |

|

|

|

|

со входами прямого и дополнительного кода |

|

|

|

PLNXORC |

исключающее ИЛИ-НЕ |

|

|

|

|

со входами прямого и дополнительного кода |

|

|

В качестве примера опишем дешифратор 2х4. Он имеет два входа X1, X2 и четыре выхода Q1, Q2, Q3, Q4. Если входные сигналы равны (“0”,”0”), то Q1=“1”; если входные сигналы равны (“1”,”0”), то Q2=“1” и т.д. Для описания дешифратора удобно использовать матрицу элементов И со входами прямого и дополнительного кода. Описание может иметь вид

UD2X4 PLANDC(2,4) UP UM X1 X2 Q1 Q2 Q3 Q4

+PLD_MDL IO_STD

+DATA=B$

+01 01

+10 01

+01 10

+10 10

$

Матрица содержит четыре двухвходовых элемента. Каждая строчка описания соответствует одному элементу, а пары чисел - его входам прямого и обратного кода. Так, в первой после DATA строке первая пара чисел указывает, что к первому входу первого элемента подключено инверсное значение сигнала X1, а ко второму его входу подключено инверсное значение

22 |

1. Моделирование цифровых схем |

сигнала X2 (значит, Q1=“1” только при X1=X2=“0”). Во второй строке первая пара чисел указывает, что к первому входу второго элемента подключен сигнал X1, а ко второму его входу подключено инверсное значение сигнала X2 (значит, Q2=“1” только при X1=“1” и X2=“0”). Третья и четвертая строки аналогично описывают подключение элементов Q3 и Q4.

Тип модели задержек ПЛМ - UPLD. Модель содержит задержки переключения “0” → “1” и “1” → “0”.

1.4.2.ТРИГГЕРЫ

Вбиблиотеке логических примитивов имеется ряд триггеров. Начнем с рассмотрения JK и D триггеров с динамическим управлением. Описываются они оператором:

U<имя> <тип триггера> (<число триггеров в корпусе>) +<<узел питания +> <узел питания ->>5)

+ <узел сигнала установки> <узел сигнала сброса> +<узел синхронизации> <узлы информационных входных сигналов>

+<узлы прямых выходов> <узлы инверсных выходов>

+<модель задержек> <модель входа/выхода>

5)- только для PSpice 5

Типы триггеров: JKFF - JK триггер, DFF - D триггер. Тип модели задержек - UEFF.

Триггеры изменяют свое состояние при изменении синхронизирующего импульса. JK триггер срабатывает на срез синхроимпульса, а D триггер - на фронт синхроимпульса.

Триггеры имеют управляющие входы установки S, сброса R и синхронизации - C. Для входов S и R активным является сигнал “0”, т.е. на эти входы надо подавать инверсные сигналы S и R. Кроме указанных управляющих входов JK триггер имеет по одному входу J и K, а D триггер имеет вход D. Все триггеры имеют прямой Q и инверсный Q выходы.

В одном элементе может быть несколько одинаковых триггеров, имеющих общие входы установки, сброса и синхронизации. Это позволяет непосредственно моделировать интегральные схемы, имеющие часто по несколько триггеров в одном корпусе.

При описании элемента сначала указываются узел установки, узел сброса, узел синхронизации. Затем для JK триггера указываются узлы J и K, а для D триггера - узел D. Если в элементе несколько триггеров, то указываются эти узлы сначала для первого триггера, затем для второго и т.д. В конце

1.4. Логические примитивы цифровых элементов |

23 |

указывается узел (или узлы, если триггеров несколько) прямого выхода, а затем - инверсного.

Примеры описания триггеров:

U5 JKFF(1) UP UM S R C J K Q NQ MDL IO_STD

U2 DFF(2) UP UM S R C D0 D1 Q0 Q1 NQ0 NQ1 MDL IO_STD

Логика работы триггеров обычная, дополненная учетом неопределенного состояния “X”. Реакция на неопределенное состояние следующая: если какой-то вход имеет состояние “X” и при замене “X” на “1” и “0” состояние выходов триггера различно, то выходным сигналам присваивается значение “X”. Например, если сигнал установки S=“X” и Q=“0”, то Q переключается в “X”. Однако при том же неопределенном состоянии сигнала установки и при Q=“1” выходной сигнал Q так и остается равным “1”.

Вчисле временных параметров триггеров фигурируют:

♦задержки переключения “0” → “1” и “1” → “0” со входов S и R на выходы Q и Q;

♦минимальная длительность сигнала “0” на входах S и R;

♦задержки переключения “0” → “1” и “1” → “0” от фронта или среза импульса синхронизации (C / C) на выходы Q и Q;

♦минимальные длительности сигналов “0” и “1” импульса синхронизации;

♦минимальное время установки J/K/D, т.е. минимальный сдвиг по времени между сигналами на входах J, K, D и последующим фронтом или срезом импульса синхронизации, переключающим выходы;

♦минимальное время установки S/R, т.е. минимальный сдвиг по времени между сигналами “1” на входах S, R и последующим фронтом или срезом импульса синхронизации, переключающим выходы;

♦минимальное время удержания J/K/D, т.е. минимальная длительность сигналов на входах J, K, D после действия фронта или среза импульса синхронизации.

Помимо триггеров с динамическим управлением в PSpice имеются примитивы RS и D триггеров-защелки с потенциальным управлением. Они описываются оператором

U<имя> <тип триггера> (<число триггеров в корпусе>)

+<<узел питания +> <узел питания ->>5)

+<узел сигнала установки> <узел сигнала сброса> +<узел сигнала защелки>

+<узлы информационных входных сигналов>

24 |

1. Моделирование цифровых схем |

+<узлы прямых выходов> <узлы инверсных выходов>

+<модель задержек> <модель входа/выхода>

5)- только для PSpice 5

Типы триггеров: SRFF - RS триггер, DLTCH - D триггер. Тип модели задержек - UGFF.

Состояние RS и D триггеров-защелок с потенциальным управлением определяется информационными входными сигналами при уровне “1” на входе сигнала защелки G (сигнала синхронизации). При G=“0” триггер сохраняет ранее принятое состояние независимо от значений входных сигналов.

Помимо входа G триггеры имеют управляющие входы предустановки S и сброса R. Для входов S и R активным является сигнал “0”, т.е. на эти входы надо подавать инверсные сигналы S и R.

В одном элементе может быть несколько одинаковых триггеров, имеющих общие входы сигнала защелки G, установки S и сброса R. Это позволяет непосредственно моделировать интегральные схемы, имеющие часто по несколько триггеров в одном корпусе.

Кроме указанных управляющих входов RS триггеры имеют информационные входы S и R (отдельные для каждого триггера), а D триггеры имеют входы D. Все триггеры имеют прямой Q и инверсный Q выходы.

При описании элемента сначала указываются общий узел установки, общий узел сброса, узел сигнала защелки. Затем для RS-триггера указываются его узлы S и R, а для D триггера - узел D. Если в элементе несколько триггеров, то указываются эти узлы сначала для первого триггера, затем для второго и т.д. В конце указывается узел (или узлы, если триггеров несколько) прямого выхода, а затем - инверсного.

Примеры описания:

U5 SRFF(1) UP UM S R G S1 R1 Q NQ MDL IO_STD

U2 DLTCH(2) UP UM S R G D0 D1 Q0 Q1 NQ0 NQ1 MDL IO_STD

Логика работы триггеров обычная, дополненная учетом неопределенного состояния “X” так же, как было описано ранее для триггеров с динамическим управлением.

Вчисле временных параметров триггеров фигурируют:

♦задержки переключения “0” → “1” и “1” → “0” с общих входов S и R на выходы Q и Q;

♦минимальная длительность сигнала “0” на общих входах S и R;

1.4. Логические примитивы цифровых элементов |

25 |

♦задержки переключения “0” → “1” и “1” → “0” от сигнала защелки на выходы Q и Q;

♦задержки переключения “0” → “1” и “1” → “0” от информационных входов S, R, D на выходы Q и Q;

♦минимальная длительность уровня “1” сигнала защелки;

♦минимальное время установки S/R/D, т.е. минимальный сдвиг по времени между сигналами на информационных входах S, R, D и последующим фронтом сигнала защелки, переключающим выходы;

♦минимальное время установки общих входов S/R, т.е. минимальный сдвиг по времени между сигналами “1” на общих входах S, R и последующим фронтом сигнала защелки, переключающим выходы;

♦минимальное время удержания S/R/D, т.е. минимальная длительность сигналов на входах S, R, D после переключения сигнала защелки.

1.4.3.ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

Вчисло примитивов PSpice включены запоминающие устройства: постоянное (ПЗУ, ROM) и оперативное (ОЗУ, RAM).

Описание ПЗУ дается оператором:

U<имя> ROM (<число адресных входов>,

+<число разрядов (выходов)>) <узел питания +> <узел питания ->

+<вход разрешения чтения> <старший разряд адреса> ...

+<младший разряд адреса> <старший разряд выхода> ...

+<младший разряд выхода> <модель задержек>

+<модель входа/выхода>

+[FILE=<имя файла>]

+[DATA=<символ системы счисления>$<данные программы>$]

+[MNTYMXDLY=<уровень>]

Тип модели задержек ПЗУ - UROM.

В постоянное запоминающее устройство загружены данные (программа), которые можно читать при сигнале, равном “1” на входе разрешения чтения. Число ячеек ПЗУ определяет <число адресных входов> Nвх как 2Nвх. Разрядность данных определяет <число разрядов (выходов)>.

При отсутствии сигнала “1” на входе разрешения чтения выходы находятся в высокоомном состоянии “Z”. При подаче сигнала разрешения они переключаются в состояние, определяемое содержимым выбранной ячейки. Если при сигнале разрешения, равном “1”, переключаются сигналы на адресных входах, то выходы переключаются с некоторой задержкой.

26 |

1. Моделирование цифровых схем |

В операторе, описывающем ПЗУ, загружаемые данные могут быть заданы двумя способами: или спецификацией FILE, определяющей имя файла, содержащего данные в формате INTEL HEX, или спецификацией DATA, после которой следуют данные.

Если используется спецификация FILE, то <имя файла> задается или текстовой константой, заключенной в кавычки “”, или текстовым выражением, заключенным в вертикальные черточки ||. При наличии спецификации FILE, спецификация DATA игнорируется, даже если она присутствует в операторе. Пример описания:

UROM16X8 ROM(4,8) UP UM ENABLE

+A3 A2 A1 A0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

+ROM_MDL

+FILE=“ROM16X8.INT”

Впримере описана память на шестнадцать 8-разрядных чисел с 4-мя адресными входами A3, A2, A1, A0 и 8-ю выходами Q7, Q6, .., Q0. Вход разрешения чтения ENABLE. Программа, записанная в ПЗУ, содержится во внешнем файле ROM16X8.INT.

Если отсутствует спецификация FILE, то загружаемые данные задаются спецификацией DATA. После ключевого слова DATA указывается <символ системы счисления>: B - двоичная, O - восьмеричная, X - шестнадцатеричная. Затем между знаками $ записываются данные. Они могут писаться слитно или разделяться в любых местах пробелами для удобства понимания и контроля. Данные записываются начиная с первого бита числа, лежащего по нулевому адресу, затем следует его второй бит и т.д. После записи всех бит этого числа аналогично указываются биты числа по первому адресу и т.д. Между символом системы счисления и первым знаком $ не должно быть пробела.

Вприведенном ниже примере описано то же ПЗУ, что и ранее, но с программой, записанной спецификацией DATA в ёЁ еричном виде:

UROM16X8 ROM(4,8) UP UM ENABLE

+A3 A2 A1 A0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

+ROM_MDL

+DATA=X$

+F1 0A 00 14

+00 01 50 3E

+0B C1 D6 90

+BF 1C AD E0

1.4. Логические примитивы цифровых элементов |

27 |

$

В числе временных параметров триггеров фигурируют задержки выборки адреса при разрешении чтения и переключениях выходов “0” → “1” и “1” → “0”, а также задержки по входу разрешения при переключениях выходов “Z”

→ “1”, “Z” → “0”, “1” → “Z”, “0” → “Z”.

Модель оперативного запоминающего устройства во многом похожа на модель ПЗУ. Отличие заключается только в наличии входа разрешения записи. Описание ОЗУ дается оператором:

U<имя> RAM (<число адресных входов>,

+<число разрядов (выходов)>) <узел питания +>

+<узел питания -> <вход разрешения чтения>

+<вход разрешения записи>

+<старший разряд адреса> ... <младший разряд адреса>

+<старший разряд входа данных> ...

+<младший разряд входа данных> <старший разряд выхода> ...

+<младший разряд выхода> <модель задержек>

+<модель входа/выхода> [FILE=<имя файла>]

+[DATA=<символ системы счисления>$<данные программы>$]

+[MNTYMXDLY=<уровень>]

ВОЗУ начальное состояние всех ячеек по умолчанию неопределенное. Однако в операторе описания ОЗУ можно задать начальные данные, загружаемые в память. В процессе расчета схемы данные в память могут записываться (при подаче на <вход разрешения записи> сигнала “1”) и считываться (при подаче на <вход разрешения чтения> сигнала “1”).

При записи в ОЗУ сначала надо подать сигналы на адресные входы и входы данных и поддерживать их в течение соответствующих длительностей установления. Затем на вход разрешения записи подается сигнал “1” длительностью не менее некоторой минимальной величины. Сигналы на адресных входах и входах данных не должны изменяться, пока сохраняется “1” на входе разрешения записи, и удерживаться в прежнем состоянии еще в течение некоторого времени удержания.

При отсутствии сигнала “1” на входе разрешения чтения выходы ОЗУ находятся в высокоомном состоянии “Z”. При подаче сигнала разрешения чтения они переключаются в состояние, определяемое содержимым выбранной ячейки. Если при сигнале разрешения чтения, равном “1”, переключаются сигналы на адресных входах, то с некоторой задержкой происходит переключение выходов.

28 |

1. Моделирование цифровых схем |

Вмодели ОЗУ не запрещено одновременное наличие сигналов “1” на входах разрешения записи и чтения. В этом случае считанные данные передаются на выходы после перехода сигнала разрешения записи из состояния “1” в состояние “0”.

Воператоре, описывающем ОЗУ, начальная загрузка данных может быть задана теми же способами, что и для ПЗУ.

Вмодели задержек, помимо аналогичных модели ПЗУ задержек выборки адреса и задержек по входу разрешения чтения, задаются еще:

♦время установления данных относительно переднего фронта разрешения записи;

♦время установления адреса относительно переднего фронта разрешения записи;

♦минимальные длительности сигнала разрешения записи при записи “0” и “1”;

♦времена удержания данных и адреса относительно заднего фронта сигнала разрешения записи.

1.4.4.ЛИНИИ ЗАДЕРЖКИ И КОНТРОЛЛЕРЫ

Квспомогательным цифровым примитивам можно отнести линию задержки цифровых сигналов и контроллеры. Линия задержки имеет один вход и один выход. Ее выходной сигнал повторяет ее входной сигнал с заданной в модели задержкой. Через линию задержки могут передаваться сигналы любой длительности. Этим она отличается от других логических элементов, например, от буфера, поскольку все логические элементы не реагируют на сигналы, длительность которых меньше задержки распространения. Линия задержки может использоваться для моделирования передачи логических сигналов по длинным линиям связи, например кабелям. Тип линии задержки - DLYLINE, тип модели задержек - UDLY. Оператор описания имеет стандартную форму. Пример описания:

U5 DLYLINE UP UM IN OUT MDL IO_STD.

Контроллеры являются вспомогательными элементами, которые можно использовать для контроля правильности временных диаграмм моделируемой схемы и фиксации возможных сбоев. Первый вид контроллера - контроллер длительности состояний “1” и “0”. Он может использоваться для контроля длительности сигналов синхронизации и защелки в триггерах, а также для фиксаций сбоев в любых точках схемы, вызванных появлением недопустимо коротких сигналов. Оператор описания контроллера имеет вид:

1.4. Логические примитивы цифровых элементов |

29 |

U<имя> WDTHCK (<число контроллеров>)

+<<узел питания +> <узел питания ->>5) <узлы входов>

+<узлы выходов высокого уровня> <узлы выходов низкого уровня>

+<модель задержек> <модель входа/выхода>

5)- только для PSpice 5

Тип модели задержек контроллера - UWDTH.

Один элемент может содержать несколько контроллеров. Каждый из них имеет один вход и два выхода. На выходе высокого уровня HOUT устанавливается уровень “1”, если во входном сигнале длительность состояния “1” меньше заданной величины. Установление HOUT=“1” происходит по срезу входного сигнала, следующему после недостаточно долгого состояния “1” на входе; при очередном фронте входного сигнала HOUT сбрасывается в “0”. На выходе низкого уровня LOUT устанавливается уровень “1”, если во входном сигнале длительность состояния “0” меньше заданной величины. Установление LOUT=“1” происходит по фронту входного сигнала, следующему после недостаточно долгого состояния “0” на входе; при очередном срезе входного сигнала LOUT сбрасывается в “0”.

Порядок перечисления узлов в описании элемента: входные узлы всех контроллеров, узлы HOUT, узлы LOUT. Например:

U5 WDTHCK(2) UP UM IN1 IN2 HOUT1 HOUT2 LOUT1 LOUT2 MDL

+IO_STD

Вкачестве параметров модели задержек задаются минимальные длительности состояний “0” и “1”, выявляемые контроллером.

Другой вид контроллера - контроллер длительностей установления, удержания и сдвигов между сигналами. Оператор его описания имеет вид:

U<имя> SUHDCK (<число контроллеров>)

+<<узел питания +> <узел питания ->>5) <узел синхронизации>

+<узлы входов> <узлы контроля установления>

+<узлы контроля удержания>

+<модель задержек> <модель входа/выхода>

5)- только для PSpice 5

Тип модели задержек - USUHD.

Один элемент может содержать несколько контроллеров. Все контроллеры имеют один общий вход сигнала синхронизации CLOCK. Кроме того,

30 |

1. Моделирование цифровых схем |

каждый контроллер имеет один вход IN и два выхода: выход контроля времени установления - SOUT и выход контроля времени удержания - HOUT. Под временем установления подразумевается интервал времени между изменением сигнала IN и фронтом импульса CLOCK, фиксирующим состояние, в которое пришла контролируемая схема под воздействием сигнала IN. На выходе контроля длительности установления SOUT устанавливается уровень “1”, если задержка фронта сигнала CLOCK по отношению к изменению входного сигнала IN меньше заданного минимального времени установления. Установление SOUT=“1” происходит по фронту импульса CLOCK, при котором нарушено ограничение на время установления; сброс SOUT в “0” происходит по следующему фронту CLOCK (если, конечно, не произошло нового нарушения ограничения).

Под временем удержания подразумевается интервал времени между фронтом импульса CLOCK и изменением входного сигнала IN, т.е. это - время, в течение которого сигнал IN должен сохранять свое значение, чтобы после фронта импульса CLOCK контролируемая схема успела его зафиксировать. На выходе контроля длительности удержания HOUT устанавливается уровень “1”, если задержка изменения входного сигнала IN по отношению к фронту сигнала CLOCK меньше заданного минимального времени удержания. Установление HOUT=“1” происходит в момент изменения сигнала IN, вызвавшего нарушение заданного времени удержания; сброс HOUT в “0” происходит по следующему фронту CLOCK.

Контроллер может использоваться для оценки правильности временных соотношений сигналов в триггерах, а также для фиксации недопустимо малых сдвигов между сигналами в любых точках схемы. В последнем случае на вход CLOCK можно подавать любой интересующий сигнал, а не обязательно сигнал синхронизации.

Порядок перечисления узлов в описании элемента: узел сигнала синхронизации, входные узлы всех контроллеров, узлы SOUT, узлы HOUT. Например:

U5 SUHDCK(2) UP UM CLK IN1 IN2 SETUP1 SETUP2 HOLD1 HOLD2

+MDL IO_STD

Впараметрах модели задержек задаются минимальные времена установления и удержания, контролируемые контроллером.

1.4.5.ИСТОЧНИКИ ЛОГИЧЕСКИХ СИГНАЛОВ

1.4. Логические примитивы цифровых элементов |

31 |

Источниками постоянных логических уровней, как уже указывалось в п. 1.1, являются глобальные узлы: $D_HI - источник сигнала “1”, $D_LO - сигнал “0”, $D_X - сигнал “X”. Эти узлы поддерживают соответствующие уровни независимо от того, что к ним подключено. Кроме того, имеется глобальный узел $D_NC, применяемый для подключения к нему выходов цифровых элементов, которые не используются в моделируемой схеме.

Если требуется иметь источник постоянного логического сигнала с некоторой заданной силой, то для него используются специальные примитивы источников постоянных уровней логических сигналов “1” и “0”, которые описываются операторами вида:

U<имя> <тип источника> (<число выходов>)

+<<узел питания +> <узел питания ->>5) <узлы выходов>

+<модель входа/выхода>

5)- только для PSpice 5

Тип источника “0” - PULLDN, источника “1” - PULLUP. Модель задержки в этих элементах не используется. А модель входа/выхода определяет силу сигнала. Примеры описания источников:

U5 PULLUP(1) 10 R1K

U2 PULLDN(4) BUS3, BUS2, BUS1, BUS0, R500

Генератор входных логических сигналов для цифровой схемы описывается как цифровой элемент оператором:

U<имя> STIM(<число выходов> <форматы>)

+<<узел питания +> <узел питания ->>5) <узлы>

+<модель входа/выхода>

+[TIMESTEP=<величина>] <программа задания сигналов>

5)- только для PSpice 5

Параметр <число выходов> определяет число генерируемых сигналов. Узлы подключения этих сигналов перечисляются в списке <узлы>.

Параметр <форматы> указывает, в каком виде (двоичном, восьмеричном или шестнадцатеричном) будут представляться в дальнейших операторах значения сигналов. Соответственно, формат указывается равным числу разрядов: 1, 3 или 4 для двоичного, восьмеричного или шестнадцатеричного представления соответственно. Сумма разрядов, указанных в параметре <форматы>, должна совпадать с числом сигналов, указанных в параметре

32 |

1. Моделирование цифровых схем |

<число выходов>. Например, пусть <число выходов> равно четырем. Тогда параметр <форматы> может быть записан в виде 1111. Это означает, что вектор значений всех сигналов в дальнейшем будет записываться в двоичном виде, например 1010. Однако при четырех сигналах параметр <форматы> может быть записан в виде 4. Это означает, что вектор значений сигналов в дальнейшем будет записываться в виде одной шестнадцатеричной цифры, т.е. не 1010, а A. Наконец, при четырех сигналах параметр <форматы> может быть записан в виде 13 или 31. Это значит, что значения сигналов в дальнейшем будет записываться в виде одной двоичной и одной восьмеричной цифры (т.е. не 1010, а 12) или, наоборот, одной восьмеричной и одной двоичной цифры (т.е. не 1010, а 50).

Параметр <модель входа/выхода> определяет, как и обычно, нагрузочную способность генератора, в частности дополнительные задержки на выходе. Параметр TIMESTEP=<величина> определяет величину шага (цикла) в секундах. Здесь под шагом подразумевается некоторая единица измерения времени, которая может использоваться в дальнейших операторах для записи временных соотношений. Например, TIMESTEP=10ns означает, что в дальнейшем можно измерять время в шагах (циклах), т.е. в десятках наносекунд.

Перейдем теперь к главной части оператора - к разделу <программа задания сигналов>. Основой программы являются команды вида

<время> <значение вектора сигналов>.

В этой команде <время> - момент, в который вектор сигналов принимает значение, указанное в команде; <значение вектора сигналов> записывается в соответствие с определенными ранее форматами. А <время> может измеряться или в секундах, или в шагах (циклах), определенных параметром TIMESTEP. Если время задается в шагах, то после числа пишется суффикс "С" (cycle). Если же время задается в секундах, то пишется суффикс "S" или масштабные суффиксы "NS", "MS" и т.п.

Например, при формате 11 команда 10ns 01 означает, что в момент 10 нс значение первого выхода генератора равно “0”, а второго - “1”. Если был определен параметр TIMESTEP=10ns, то команда 5c 01 означает, что выходы примут это значение в 50 нс (5 циклов по 10 нс).

Пусть требуется описать источник сигнала OUT0, находящийся в нулевой момент в состоянии “0”, в 20 нс переключающийся в “1”, а в 40 нс возвращающийся в “0”. Описание может иметь вид

|

|

|

1.4. Логические примитивы цифровых элементов |

33 |

UCLOCK STIM(1,1) UP UM OUT0 IO_STM |

|

|||

+ |

0s |

0 |

; в нулевой момент OUT0=“0” |

|

+ 20ns 1 |

; в 20 нс OUT0=“1” |

|

||

+ 40ns 0 |

; в 40 нс OUT0=“0” |

|

||

Воспользовавшись параметром TIMESTEP, то же описание можно |

||||

представить в виде |

|

|

||

UCLOCK STIM(1,1) UP UM OUT0 IO_STM TIMESTEP=20ns |

|

|||

+ |

0s |

0 |

; в нулевой момент OUT0=“0” |

|

+ 1c 1 |

|

; в 20 нс OUT0=“1” |

|

|

+ 2c 0 |

|

; в 40 нс OUT0=“0” |

|

|

Значения времени в последовательных командах должны строго возрастать. В частности, не должно быть двух событий, относящихся к одному моменту времени. Перед числом, обозначающим время, может ставиться знак "+" - это означает, что задан не момент, а отрезок времени, который должен прибавляться к текущему времени. Например, команда +5ns 10 означает, что заданные в ней значения сигналов появятся через 5 нс при отсчете от момента, которому соответствует данная команда. Таким образом, приведенный выше пример может быть записан в виде:

UCLOCK STIM(1,1) UP UM OUT0 IO_STM TIMESTEP=20ns

+ |

0s |

0 |

; в нулевой момент OUT0=“0” |

+ +1c |

1 |

; в 20 нс OUT0=“1” |

|

+ |

+1c |

0 |

; в 40 нс OUT0=“0” |

Помимо указанной основной команды в программе могут использоваться команды:

1)<LABEL=<имя метки>>

2)<<время> GOTO <имя метки> <N> TIMES>

3)<<время> GOTO <имя метки> UNTIL GT <значение>

4)<<время> GOTO <имя метки> UNTIL GE <значение>

5)<<время> GOTO <имя метки> UNTIL LT <значение>

6)<<время> GOTO <имя метки> UNTIL LE <значение>

7)<<время> INCR BY <значение>

8)<<время> DECR BY <значение>

Первая из них задает метку точке программы, в которую можно передать управление. Команды 2 - 6 передают управление на метку. Причем команда

34 |

1. Моделирование цифровых схем |

LABEL должна быть записана до команды GOTO. Команда GOTO передает управление не на саму метку, а на оператор, следующий за меткой, причем команда, записанная в этом операторе, выполняется немедленно, независимо от указанного в ней времени.

Команда 2 осуществляет безусловную передачу управления N раз, после чего перестает выполняться. Таким образом, петля команд от LABEL до GOTO выполняется N+1 раз (один раз при первом проходе и N раз при возвратах). Если задано N=-1, то возвраты на метку повторяются неограниченное число раз, т.е. моделируется периодический сигнал с неограниченным числом периодов.

Команды 3 - 6 осуществляют условные передачи управления. При этом вектор выходных сигналов сравнивается с параметром <значение>. Команда 3 передает управление, если вектор сигналов > <значение>; команда 4 - если ≥; команда 5 - если <; команда 6 - если≤

Команда 7 осуществляет сложение вектора сигналов с параметром <значение>, а команда 8 вычитает из вектора параметр <значение>.

Рассмотрим примеры описания генераторов сигналов, использующие эти команды. Пусть требуется описать источник периодического сигнала OUT1, в нулевой момент времени находящегося в состоянии “0”, а затем неограниченное число раз переключающийся из “0” в “1” и обратно каждые 5 нс. Описание может иметь следующий вид

1.4. Логические примитивы цифровых элементов |

35 |

|

UCLOCK STIM(1,1) UP UM OUT1 IO_STM |

|

|

+ 0s 0 |

; в нулевой момент OUT1=“0” |

|

+ LABEL=STARTLOOP |

|

|

+ +5ns 1 |

; через 5 нс OUT1=“1” |

|

+ +5ns 0 |

; еще через 5нс OUT1=“0” |

|

+ +5ns GOTO STARTLOOP -1 |

; через 5 нс уход на |

|

TIMES |

STARTLOOP |

|

После ухода на метку STARTLOOP выполняется первый оператор цикла без ожидания указанных в нем пяти наносекунд. Задание -1 TIMES вызывает бесконечное повторение цикла.

Второй пример иллюстрирует генератор двух сигналов OUT1 и OUT2, первый из которых переключается с полупериодом 10 нс, а второй - 20 нс. Таким образом, полный цикл переключений составляет 40 нс и требуется описать три таких цикла. Подобные сигналы, каждый последующий с удвоенным периодом по отношению к предыдущему, позволяют перебрать все возможные сочетания входных сигналов схемы. Описание может иметь вид

US1 STIM (2,11) OUT1 OUT2 IO_STM TIMESTEP=10ns

+0c 00

+LABEL=STARTLOOP

++1c 01

++1c 10

++1c 11

+4c GOTO STARTLOOP 2 TIMES

Вмомент 40 нс происходит переход на метку STARTLOOP и выполняется без задержки первый оператор цикла. Поскольку задано 2 TIMES, в следующий раз будет осуществлен повторный уход на начало цикла. Таким образом, цикл будет повторен 3 раза.

Следующий пример иллюстрирует шестнадцатеричный формат описания:

U1 STIM(4,4) IN1 IN2 IN3 IN4 IO_STM TIMESTEP=1ns