- •1 Цель работы

- •2 Порядок выполнения работы

- •Выполнение арифметических операций компьютере

- •Особенности выполнения операций над числами с плавающей запятой

- •4. Методические указания

- •2 Порядок выполнения работы

- •3. Оформите отчет, который должен содержать:

- •4. Методические указания

- •3. Методические указания 1

- •3. Методические указания 1.

- •9.3.1. ПримерЗ

- •9.3.3. Содержание отчета

- •3. Методические указания

- •9.7.4. Контрольные вопросы

- •9.8.4. Контрольные вопросы

- •1 Цель работы

- •2 Порядок выполнения работы

- •3. Методические указания

- •Invoke GetModuleHandle,0

- •Заполнение данными.

2 Порядок выполнения работы

Прочитать МЕТОДИЧЕСКИЕ УКАЗАНИЯ

Нарисовать в тетради обозначения схемных элементов

Ответить на контрольные вопросы

3. Оформите отчет, который должен содержать:

титульный лист (см. приложение);

цель работы;

порядок выполнения работы;

4. Методические указания

Начало исследований в области формальной логики было положено работами Аристотеля в IV в. до нашей эры. Однако строго формализованный подход к проблеме впервые был предложен Дж. Булем. В честь него алгебру высказывания называют булевой (булевской) алгеброй, а логические значения — булевыми (булевскими). Основу математической логики составляет алгебра высказываний. Алгебра логики используется при построении основных узлов ЭВМ (дешифратор, сумматор, шифратор).

Алгебра логики оперирует с высказываниями. Под высказыванием понимают повествовательное предложение, относительно которого можно утверждать, истинно оно или ложно. Например, выражение «Расстояние от Москвы до Киева больше, чем от Москвы до Тулы» истинно, а выражение «5 < 2» — ложно.

Высказывания (логические переменные) принято обозначать буквами латинского алфавита (иногда — с индексами): А, В, С, ..., X, Y, а, Ь, с, ..., х, у, z, (х1, х2, ..., хi, ...) и т. д. Если высказывание С истинно, это обозначается как С= 1 (С= t, true), а если оно ложно, то С= 0 (С = f, false).

Логические операции и базовые элементы компьютера

В алгебре высказываний над высказываниями можно производить определенные логические операции, в результате которых получаются новые высказывания. Истинность результирующих высказываний зависит от истинности исходных и использованных для их преобразования логических операций. „

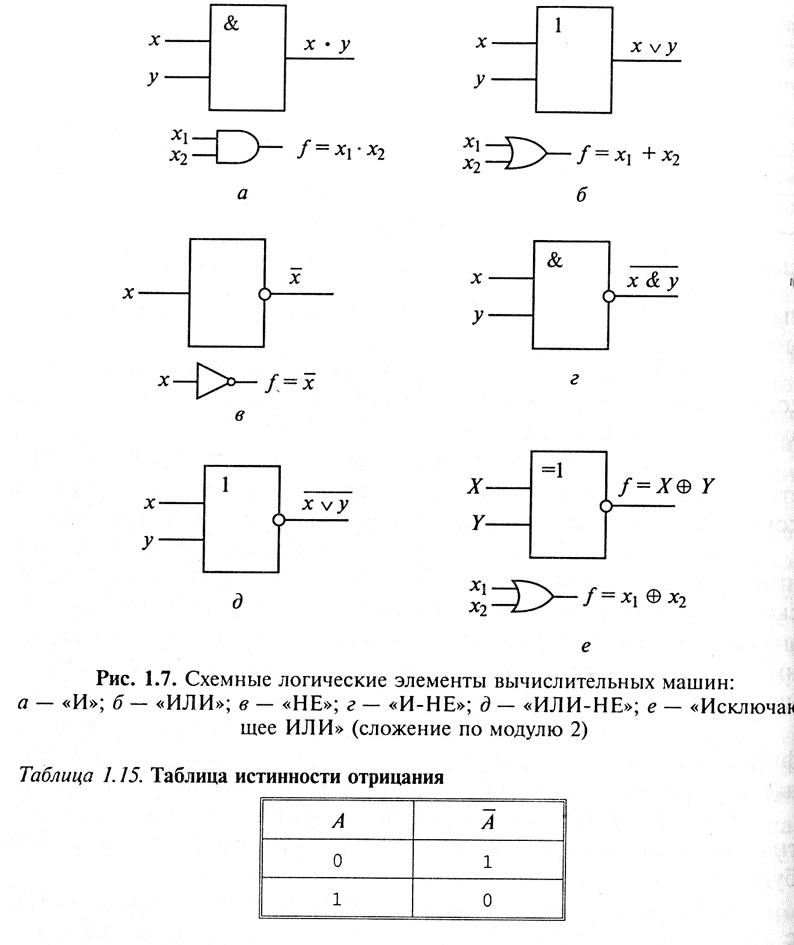

Схемные элементы ЭВМ. Преобразование информации в ЭВМ осуществляется элементами (схемами) двух классов:

комбинационными;

последовательностными (схемами с памятью).

Состояние выходов комбинационных схем однозначно определяется состояниями входов в данный момент времени.

Состояние выходов в последовательных схемах определяется не только состоянием входов, но и внутренними состояниями, имевшими место в предыдущие моменты времени.

Комбинационные схемы являются техническим аналогом булевых функций. Подобно тому, как сложная булева функция может быть получена суперпозицией более простых функций, так и комбинационная схема может строиться из более простых схем.

Существует следующее определение — систему логических элементов, с помощью которых путем суперпозиции можно представить любую сколь угодно сложную комбинационную схему, называют функционально полной. Известны различные функционально полные системы элементов, но наибольшее распространение получили системы, использующие логические операции, выражаемые предлогами НЕ, и, или.

Логический элемент компьютера — это часть электронной схемы, которая реализует элементарную логическую функцию. Логическими элементами компьютеров являются электронные схемы «И», «ИЛИ», «НЕ», «И-НЕ», «ИЛИ-НЕ» или другие (называемые также вентилями), а также триггер. Можно показать, что с помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Работу логических элементов описывают с помощью таблиц истинности.

Рассмотрим логические операции и соответствующие им элементы логических схем.

Конъюнкция. Соединение двух (или нескольких) высказываний в одно с помощью союза и (or) называется операцией логического умножения, или конъюнкцией. Эту операцию принято обозначать знаками «^, &» или знаком умножения «х». Сложное высказывание А ^ В истинно только в том случае, когда истинны оба входящих в него высказывания. Истинность такого высказывания задается табл.

|

Коньюнкция |

Дизъюнкция | |||||

|

A |

B |

A&B |

A |

B |

AvB |

AxorB(исключающее или) |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Логическая схема «И» реализует конъюнкцию двух или более логических значений. Условное обозначение на структурных диаграммах схемы «И» с двумя входами представлено на рис.

Единица на выходе схемы «И» будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет нуль, на выходе также будет нуль.

Связь между выходом z этой схемы и входами х и у описывается соотношением z = x&y (читается как «х и у»). Операция конъюнкции на структурных схемах обозначается знаком «&».

Дизъюнкция. Объединение двух (или нескольких) высказываний с помощью союза или (OR) называется операцией логического сложения, или дизъюнкцией. Эту операцию обозначают знаками «I, v» или знаком сложения «+». Сложное высказывание A v В истинно, если истинно хотя бы одно из входящих в него высказываний (см. табл. 1.14).

В последнем столбце табл. 1.14 размещены результаты модифицированной операции ИЛИ — Исключающее или (XOR). Отличается от обычного или последней строкой (см. также рис. 1.7, е).

Схема «ИЛИ» реализует дизъюнкцию двух или более логических значений. Когда хотя бы на одном входе схемы «ИЛИ» будет единица, на ее выходе также будет единица.

Условное обозначение на структурных схемах схемы «ИЛИ» с двумя входами представлено на рис. 1.7, б. Знак «1» на схеме происходит от классического обозначения дизъюнкции как «>=» (т. е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами х и у описывается соотношением z = x v у (читается как «х или у»).

Инверсия.

Присоединение

частицы НЕ (not)

к некоторому

высказыванию_

называется операцией отрицания (инверсии)

и обозначается

А

(или

А).

Если

высказывание А

истинно,

то В

ложно,

и наоборот (табл. 1.15)

Схема «НЕ» (инвертор) реализует операцию отрицания. Связь между входом х этой схемы и выходом z можно записать соотношением z = х, где х читается как «не х» или «Инверсия х».

Если на входе схемы «О», то на выходе «1», и наоборот. Условное обозначение на структурных схемах инвертора — на рис. 1.7, в.

Вентили. Кроме схемных элементов, соответствующих перечисленным логическим операторам, в состав логических схем ходят комбинированные связки, именуемые вентилями, например, следующие.

Схема

«И-НЕ» состоит

из элемента «И» и инвертора и осуществляет

отрицание результата схемы «И» (табл.

1.16). Связь между

выходом z

и

входами х и у

схемы

записывают как

,

или

«Инверсия х

и

у». Условное обозначение на структурных

схемах схемы «И-НЕ» с двумя входами

приведено на рис. 1.7, г.

,

или

«Инверсия х

и

у». Условное обозначение на структурных

схемах схемы «И-НЕ» с двумя входами

приведено на рис. 1.7, г.

Таблица 1.16. Таблица истинности схем «И-НЕ», «ИЛИ-НЕ»

|

Инверсия х и у |

Инверсия x или у | |||||

|

x |

y |

|

x |

y |

| |

|

0 |

0 |

1 |

0 |

0 |

1 | |

|

0 |

1 |

1 |

0 |

1 |

0 | |

|

1 |

0 |

1 |

1 |

0 |

0 | |

|

1 |

1 |

0 |

1 |

1 |

0 | |

Схема «ИЛИ-НЕ» состоит из элемента «ИЛИ» и инвертора и осуществляет отрицание результата схемы «ИЛИ» (табл. 1.16). Связь между выходом z и входами хну схемы записывают как х v у, или «Инверсия х или у». Условное обозначение на структурных схемах схемы «ИЛИ-НЕ» с двумя входами представлено на рис. 1.7, д.

Схема «Исключающее ИЛИ» (рис. 1.7, е) соответствует «сложению по модулю два» (см. также табл. 1.14).

Следует отметить, что помимо операций и, или, не в алгебре высказываний существует ряд и других операций. Например, операция эквивалентности (эквиваленции)

А ~ В (А = В, или A eqv В) (табл. 1.17).

Таблица 1.17. Таблицы истинности операций эквивалентности и импликации

|

Эквивалентность |

Импликация | |||||

|

А |

В |

А~В |

А |

В |

А | |

|

0 |

0 |

1 |

0 |

0 |

1 | |

|

0 |

1 |

0 |

0 |

1 |

1 | |

|

1 |

0

|

0 |

1 |

0 |

0 | |

|

1 |

1 |

1 |

1 |

1 |

1 | |

Другим примером может служить логическая операция импликации или логического следования (А —> В, A IMP В)у иначе говоря, «если А, то В» (табл. 1.17).

Высказывания,

образованные с помощью логических

операций,

называются сложными. Истинность сложных

высказываний

можно установить, используя таблицы

истинности. Например,

истинность сложного высказывания ( ^

^ )

определяется

табл.

1.18.

)

определяется

табл.

1.18.

Таблица

1.18. Таблица

истинности высказывания (A&B)v( &

& )

)

|

А |

В |

|

|

|

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

Высказывания, у которых таблицы истинности совпадают, называются равносильными. Для обозначения равносильных высказываний используют знак «=» (А = В). Рассмотрим сложное высказывание

(А

^

В)

v

( ^

^ )

—

табл. 1.19.

)

—

табл. 1.19.

Таблица

1.19. Таблица

истинности выражения (А&

В)

v

( &

& )

)

|

А |

|

B |

|

А&В |

|

(А & В) v (А &B) |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

Если сравнить эту таблицу с таблицей истинности операции эквивалентности высказываний A v В (см. табл. 1.17), то можно увидеть, что высказывания (А ^ В) v (А ^ В) и А ~ В тождественны, т. е. (А ~ В) = (А л В) v (А л В).

В алгебре высказываний можно проводить тождественные преобразования, заменяя одни высказывания равносильными им другими высказываниями.

Свойства операций. Исходя из определений дизъюнкции, конъюнкции и отрицания, устанавливаются свойства этих операций и взаимные распределительные свойства. Приведем примеры некоторых из этих свойств:

Высказывания, образованные с помощью нескольких операций логического сложения, умножения и отрицания, называются сложными. Истинность всякого сложного высказывания устанавливается с помощью таблиц истинности. Сложные высказывания, истинные (true) для любых значений истинности входящих в них простых высказываний, называются тождественно-истинными. Наоборот, тождественно-ложными являются формулы, принимающие значение false для любых значений входящих в него простых высказываний.

В табл. 1.20 приведено доказательство истинности дистрибутивного закона. Аналогичным образом могут быть доказаны и другие тождества.

|

Таблица 1.20. Доказательство истинности |

| |||||||

|

А |

B |

C |

BvC |

A^(BvC) |

А^B |

А^C |

(A ^B)v(A ^С) | |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 | |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 | |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 | |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 | |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 | |

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 | |

|

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 | |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 | |

Доказательство таблицы истинности дистрибутивного закона

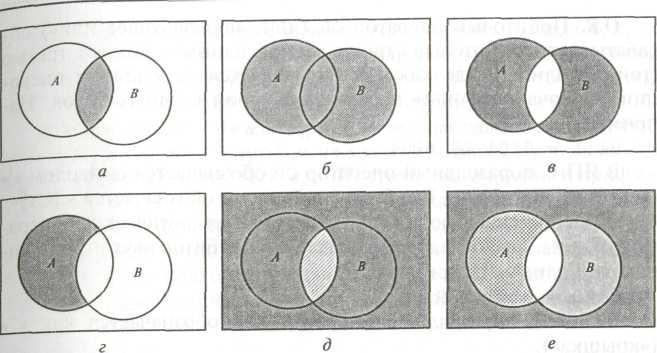

На рис. 1.8, а—е приведены иллюстрации к основным логическим операциям и их композициям (так называемые диаграммы Эйлера — Венна) — области истинности каждого из высказываний и их объединения (дизъюнкции), пересечения (конъюнкции) и других операций. «Первый» из законов де Моргана иллюстрируется рис. 1.8, д, е.

Операции

над битовыми строками.

В

некоторых современных ЯП

реализованы операции и/или функции

обработки битовых строк

(машинных слов, их частей или групп,

которые могут содержать

числовые, символьные, мультимедийные

и пр. данные). Наиболее

распространенными являются побитовые

операции, прямо

вытекающие из рассмотренных ранее

операций над логическими

данными (табл. 1.21).

Рис. 1.8. Некоторые примеры диаграмм Эйлера — Венна:

а — конъюнкция высказываний А и В (AND); б — дизъюнкция высказываний А и В

(or); в — исключающая дизъюнкция (xor); г — разность высказываний (А — В);

д — иллюстрация к законам де Моргана (дополнение пересечения высказываний);

е — иллюстрация к законам де Моргана (объединение дополнений)

Таблица 1.21. Операнды и результаты некоторых побитовых операций

|

X |

У |

х & у |

X v у |

X IMP y |

.x EQV y |

х XOR y |

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Логические операции.

NOT. Поразрядный оператор not (he), или дополнение, является одноместной операцией, которая выполняет логическое отрицание на каждом бите, формируя дополнение данного бинарного значения. Биты, содержавшие бывшие «0», устанавливаются в «1»; и наоборот. Например:

1000 = NOT 0111

Во многих языках программирования (включая С), поразрядный оператор not обозначается как «~» (тильда). Этот оператор не следует путать с «логическим отрицанием» («!» — восклицательный знак), который обрабатывает все значение как отдельное булевское.

OR. Побитовый оператор OR (или, «включающее или») обрабатывает две битовые строки равной длины и создает третью (той же длины), где каждый бит является результатом операции «включающее или» над каждой парой входных битов. Например:

0111 = 0101 OR 0011

В ЯП С поразрядный оператор OR обозначается символом «|» (вертикальная черта). Его булевский аналог обозначается как «||».

XOR («исключающее или») выполняет логическую операцию XOR на каждой паре соответствующих битов двух строк одинаковой длины. Например:

0110 = 0101 XOR 0011

В ЯП С поразрядный оператор XOR обозначается как «^» («крышка»).

Ассемблерные программисты иногда используют операцию XOR как краткую команду обнуления значения регистра. Выполнение XOR над двумя одинаковыми значениями всегда дает нуль в результате, и во многих архитектурах эта операция требует меньшего количества циклов центрального процессора, чем последовательность операций, которые загружают нулевое значение в регистр.

AND. Поразрядный and (и) выполняет логическую операцию AND на каждой паре соответствующих битов двух битовых строк. Например:

0001 = 0101 AND ООН

В ЯП С поразрядный оператор and обозначается как «&» (амперсанд). Булевский аналог записывается как «&&» (два ам-персанда).

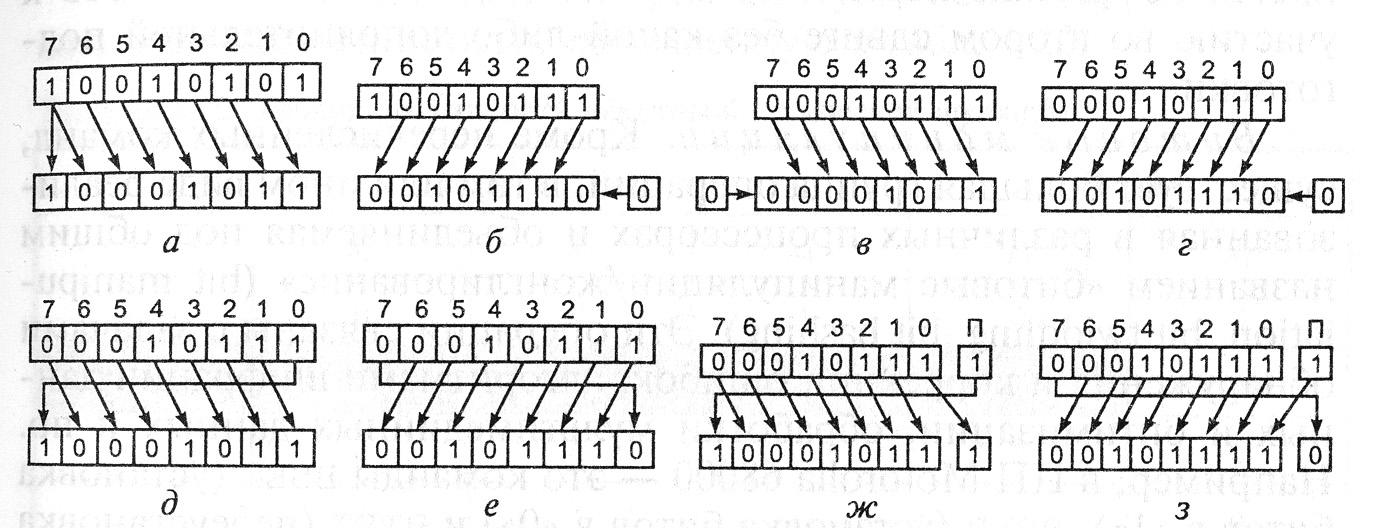

Битовые сдвиги (bit shifts). Эти операции также осуществляются на битовом уровне и являются унарными. В этих операциях биты сдвигаются в регистре (влево или вправо). Поскольку регистры компьютера имеют ограниченный размер, некоторые биты будут «выдвинуты из регистра» с одной из его сторон, и аналогичное число бит должно быть «вдвинуто в регистр» с другой. Основное различие в операциях битовых сдвигов заключается в том, как именно они обрабатывают эти «вдвиги/вы-двиги».

Арифметический сдвиг. При арифметическом сдвиге аннулируются биты, которые сдвинуты из любого конца регистра. Однако при арифметическом сдвиге влево с правой стороны вдвигаются нули, а при сдвиге вправо знаковый разряд остается в крайнем правом разряде, сохраняя знак операнда (рис. 1.9, а, б). Арифметический сдвиг влево на п разрядов эквивалентен умножению на 2" (если не происходит переполнения), в то время как арифметический сдвиг вправо на п эквивалентен делению на 2".

Логический

сдвиг. При

логическом сдвиге аннулируются

биты, которые сдвинуты, и их место

занимают нули (в любом конце регистра)

— рис. 1.9, в,

г. Поэтому,

логический и арифметический сдвиги

влево оказываются тождественными.

Однако логический

сдвиг вправо вставляет биты со значением

«0» вместо

копии знакового разряда. Следовательно,

логический сдвиг является

более подходящим для двоичных чисел

без знака, в то время как арифметический

сдвиг — для двоичных со знаком

Рис. 1.9. Битовые сдвиги:

а — арифметический сдвиг вправо; б — арифметический сдвиг влево; в — логический сдвиг вправо; г — логический сдвиг влево; д — правый циклический сдвиг (вращение); е — левый циклический сдвиг; ж — правый циклический сдвиг через перенос; з — левый циклический сдвиг через перенос

Циклический сдвиг или разрядное вращение. В этой операции биты, «выдвигаемые» из регистра в любую сторону, «вдвигаются» в регистр с другой его стороны (рис. 1.9, д, е). Эта операция используется, если необходимо сохранить все существующие биты, и часто применяется в цифровой криптографии.

Циклический сдвиг «через перенос». В отличие от обычного сдвига (или сдвига «не через перенос») здесь считается, что два конца регистра отделены флажком переноса («п» на Рис. J.9, ж, з). Бит, который «вдвинут» (с любой стороны регистра), — старое значение флажка переноса, а бит, который «выдвинут» (с противоположной стороны) становится новым значением флажка переноса. Единичный сдвиг через перенос может моделировать логический или арифметический сдвиг позиции, устанавливая флажок переноса заранее. Например, если флажок переноса содержит «О», то правый сдвиг через перенос соответствует логическому сдвигу вправо, а если флажок переноса содержит копию знакового разряда, то это арифметический сдвиг. Поэтому некоторые микроконтроллеры имеют только команды циклического сдвига. Циклический сдвиг через перенос особенно полезен, если операция осуществляется над числами, большими разрядности процессора (двойной или более длины). Если число хранится в двух регистрах, то бит, который «выдвинут» из первого регистра, должен быть «вдвинут» во второй. В данном случает этот бит сохраняется во флажке переноса в течение первого сдвига и готов к участию во втором сдвиге без какой-либо дополнительной подготовки.

Битовые манипуляции. Кроме перечисленных команд, существует большая группа операций, в том или ином виде реализованная в различных процессорах и объединяемая под общим названием «битовые манипуляции/жонглирование» (bit manipulation, bit twiddling, bit bashing). Эти операции связаны с задачами обнаружения и коррекции ошибок, алгоритмами шифрации данных и оптимизации, обработки мультимедийных данных и пр. Например, в ЦП Motorolla 68000 — это команды bset (установка битов в «1»), BCLR (установка битов в «0») и btst (переустановка нулевых битов); в системе команд SSE4 — это popcnt («Population Count» — подсчет количества битов, например установленных в «1») и т. д.

В процессорах архитектуры К10 (AMD) добавлен функциональный (исполнительный) блок расширенных битовых манипуляций — Advanced Bit Manipulation (ABM) — см. рис. 3.33.

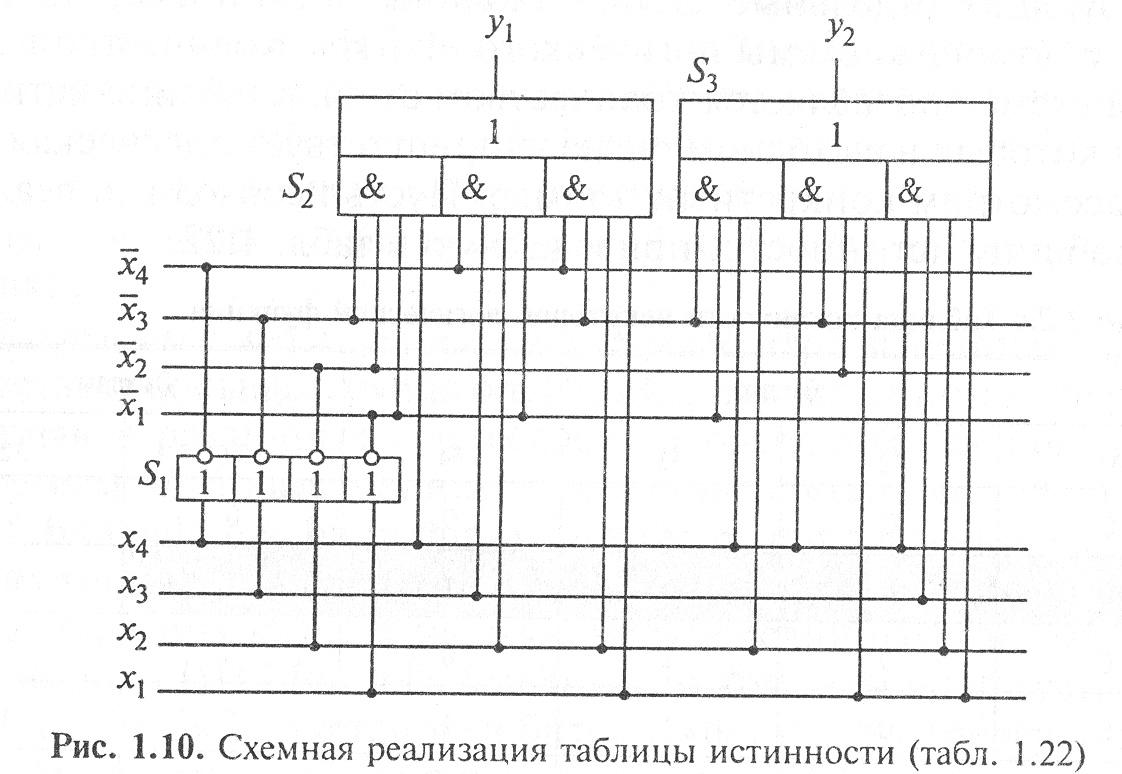

Синтез и оптимизация схем

При построении схемы, реализующей произвольную таблицу истинности, каждый выход анализируется (и строится схема) отдельно. Для реализации таблицы истинности с помощью логических элементов «И» достаточно рассмотреть только те строки таблицы истинности, которые содержат логические «1» в выходном сигнале. Строки, содержащие в выходном сигнале логический «0», в построении схемы не участвуют. Каждая строка, содержащая в выходном сигнале логическую «1», реализуется схемой логического «И» с количеством входов, совпадающим с количеством входных сигналов в таблице истинности. Входные сигналы, описанные в таблице истинности логической «1», подаются на вход этой схемы непосредственно, а входные сигналы, описанные в таблице истинности логическим «0», подаются на вход через инверторы. Объединение сигналов с выходов схем, реализующих отдельные строки таблицы истинности, производится с помощью схемы логического «ИЛИ». Количество входов в этой схеме определяется количеством строк в таблице истинности, в которых в выходном сигнале присутствует логическая «1». Рассмотрим конкретный пример. Пусть необходимо реализовать таблицу истинности, приведенную в табл. 1.22.

Для

построения схемы, реализующей сигнал

у1,

достаточно

рассмотреть

строки, выделенные светлой штриховкой.

Эти строки

реализуются сборкой (микросхемой) S2

на

рис. 1.10. Каждая строка

реализуется своей схемой «И», затем

выходы этих схем объединяются.

Для построения схемы, реализующей сигнал

у2,

достаточно

рассмотреть строки, выделенные более

темной штриховкой.

Эти строки реализуются сборкой S3.

Инвертирование входов

схемы осуществляется сборкой S1.

Преобразования логических формул. Равносильные преобразования логических формул имеют то же назначение, что и преобразования формул в обычной алгебре. Они служат для упрощения формул или приведения их к определенному виду путем использования основных законов алгебры логики.

Под упрощением формулы, не содержащей операций импликации и эквиваленции, понимают равносильное преобразование, приводящее к формуле, которая по сравнению с исходной либо содержит меньшее число операций конъюнкции и дизъюнкции и не содержит отрицаний неэлементарных формул, либо содержит меньшее число вхождений переменных.

Некоторые преобразования логических формул похожи на преобразования формул в обычной алгебре (вынесение общего множителя за скобки, использование переместительного и сочетательного законов и т. п.), тогда как другие преобразования основаны на свойствах, которыми не обладают операции обычной алгебры (использование распределительного закона для конъюнкции, свойств поглощения и склеивания, законов де Моргана и др.).

Практическая работа 6 -7-8. Регистры процессора. Память.

ЦЕЛЬ РАБОТЫ

Приобретение навыков работы с регистрами процессора. и памятью.

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

Прочитать методические указания 1, 2

Разобрать приведенные примеры 1, 2

Выполнить задания к работе 1 и 2

Ответить на контрольные вопросы 1, 2

Оформите отчет, который должен содержать:

- титульный лист (см. приложение);

постановку задачи;

формулировка варианта задания.

размещение данных в ОЗУ.

программа в форме таблицы

последовательность состояний регистров ЭВМ при выполнении программы в режиме Шаг для одного значения аргумента.

результаты выполнения программы для нескольких значений аргумента, выбранных самостоятельно.

В

В

&

&

&

&