Метод_вк_КП

.pdf

I. Завдання. Розробити синхронний тригер за M-S схемою на елементах АБО-НІ та за схемою трьох тригерів на елементах І-НІ зі встановлювальними входами для реалізації функції, що задана таблицями переходів. Провести логічне моделювання в системі MicroCAP або за допомогою інших програм, отримати часові діаграми в контрольних вузлах. Визначити повний час перемикання тригера, мінімальну довжину та максимальну тактову частоту сигналів.

Методика виконання завдання

1. Нехай задано таблицю переходів тригера на два вхідних сигнали

Таблиця 9 |

|

|

|

|

(табл.9). |

|

|

||

|

t-1 |

|

|

t |

2. Вибирається базова струк- |

||||

|

|

|

|

|

|

тура |

тригера, |

на |

основі якої |

|

x1 |

x2 |

Qt |

||||||

|

буде |

синтезовано СК заданого |

|||||||

|

0 |

0 |

0 |

|

тригера. За таку структуру для |

||||

0 |

1 |

|

|

t-1 |

схеми M-S можна вибирати |

||||

|

Q |

||||||||

1 |

0 |

1 |

|

схему RS-тригера з інвертором, |

|||||

1 |

1 |

Х |

яку |

виконано |

на |

елементах |

|||

АБО-НІ (як вказано в завданні) або схему, яку виконано за

структурою трьох тригерів на елементах І-НІ.

3. Визначити, при яких значеннях функції f1 та f2 ЗЕ, виходи якого є

виходами Q та Q тригера, здійснюються певні переходи з одного стану в інший в момент спрацьовування тригера.

Оскільки у вибраній схемі як ЗЕ використовується асинхронний RSтригер на елементах АБО-НІ, його порядок переходів має такий вигляд:

з0 в 0 при f1 = X; f2 = 0;

з0 в 1 при f1 = 0; f2 = 1;

з1 в 0 при f1 = 1; f2 = 0;

з1 в 1 при f1 = 0; f2 = X.

Усхемі тригера, який побудовано на трьох тригерах, як ЗЕ використовується асинхронний RS-тригер на елементах І-НІ, порядок функціонування якого задано співвідношеннями:

з0 в 0 при f1 = 1; f2 = Х;

з0 в 1 при f1 = 0; f2 = 1;

з1 в 0 при f1 = 1; f2 = 0;

з1 в 1 при f1 = Х; f2 = 1.

4.Побудувати повну таблицю переходів заданого тригера згідно з даними свого варіанта з урахуванням структури і типу логічних елементів

та на основі визначеного в п.3 порядку переходів ЗЕ заповнити в цій таблиці графи для f1 та f2 , аналізуючи переходи Q(t) та Q(t+1) у кожному рядку таблиці.

Для нашого прикладу використовуються табл. 10 та 11, які відрізняються тим, що таблиця 10 побудована на основі таблиці 9 з урахуванням того, що базову структуру MSтригера виконано на логічних елементах АБО-НІ і працює вона в системі інверсних змінних, а базову структуру тригера на трьох тригерах виконана на схемах логічних елементів І-НІ і працює вона в системах прямих змінних.

Таблиця 10 Таблиця 11

|

|

t-1 |

|

|

|

|

|

C |

x1 |

x2 |

|

Qt-1 |

Qt |

f1 |

f2 |

0 |

0 |

0 |

|

0 |

Х |

Х |

Х |

0 |

0 |

0 |

|

1 |

Х |

Х |

Х |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

Х |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

0 |

0 |

Х |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

Х |

1 |

0 |

0 |

|

1 |

1 |

Х |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

Х |

1 |

0 |

1 |

|

1 |

1 |

Х |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

Х |

1 |

1 |

0 |

|

1 |

1 |

Х |

0 |

1 |

1 |

1 |

|

0 |

0 |

0 |

Х |

1 |

1 |

1 |

|

1 |

1 |

Х |

0 |

|

|

t-1 |

|

|

|

|

|

C |

x1 |

x2 |

|

Qt-1 |

Qt |

f1 |

f2 |

0 |

0 |

0 |

|

0 |

0 |

1 |

Х |

0 |

0 |

0 |

|

1 |

1 |

Х |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

Х |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

Х |

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

Х |

0 |

1 |

1 |

|

1 |

1 |

Х |

1 |

1 |

0 |

0 |

|

0 |

0 |

1 |

Х |

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

Х |

1 |

1 |

1 |

1 |

|

0 |

Х |

Х |

Х |

1 |

1 |

1 |

|

1 |

Х |

Х |

Х |

5. За допомогою діаграм Вейча (наприклад, як на рис.9, а та б) знайти мінімальну форму функцій f1 та f2 у базисі АБО-НІ та І-НІ, використовуючи для цього правило де Моргана.

Для MS-тригера, об'єднуючи за нулями, маємо: f1 =C+Qt−1 +X1 X2;

f 2 = C + X 1 + Q t −1 ,

а для тригера за схемою трьох тригерів, об'єднуючи за одиницями:

f1 =C+Qt−1 +X1 X2;

f 2 = C + X 1 + Q t −1 .

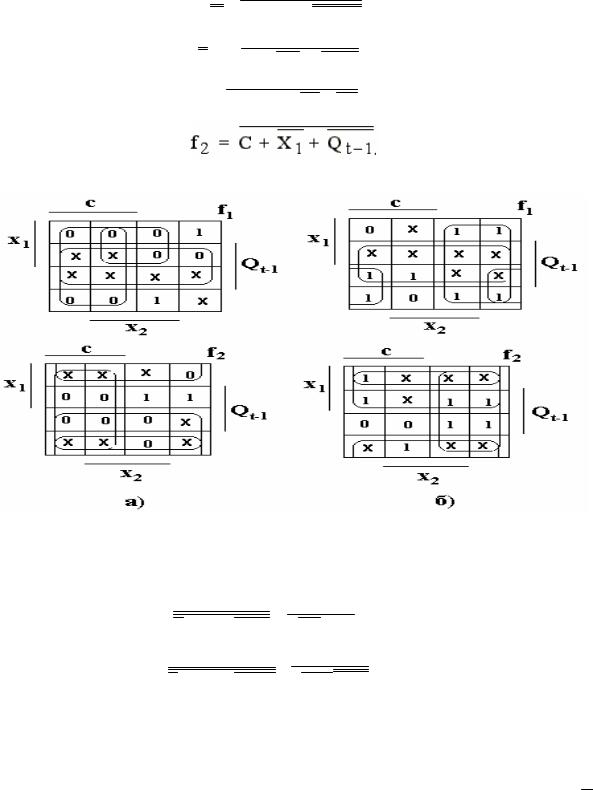

6. Доведіть отримані функції до вигляду, зручного для реалізації на

елементах АБО-НІ і І-НІ. Відповідно, для: МSтригера:

f1 =C+Qt−1 +X1 X2;

f 2 = C + X 1 + Q t −1 ;

f1 =C+Qt−1 +X1 +X2;

Рисунок 9 – Діаграми Вейча

Для тригера за схемою трьох тригерів:

f2 = C + X 1+Q t−1 = CX 1Q t−1;

f1 =C +Q t−1+X 1X 2 =CQ t−1X1X2

7. Згідно з отриманими рівняннями для функцій f1 та f2 і базовими схемами MSтригера та тригера за схемою трьох тригерів з урахуванням заданої елементної бази (елементи АБО - НІ та І – НІ, відповідно,) побудувати схеми тригерів (рис.10). Зверніть увагу на те, що для тригерів

(рис.10), що виконані на логічних схемах АБО - НІ, виходи Q та Q міняються місцями.

8. Згідно із завданням тригери, які синтезуються, повинні мати встановлювальні входи, тому їх необхідно зобразити на схемі.

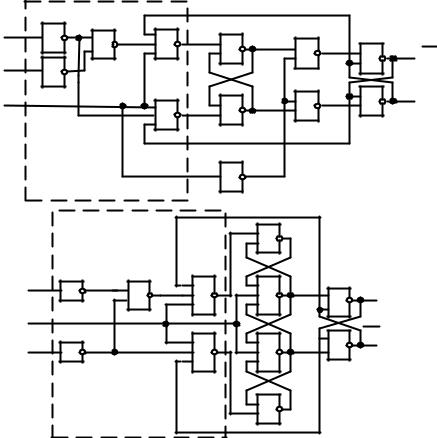

9. Проектування тригерних пристроїв складається з вибору елемента

пам’яті і синтезу схеми керування в заданному елементному базисі. Логічне моделювання цифрових пристроїв виконується в системі

MicroCAP. Результати моделювання зображуються у вигляді часових діаграм, за якими аналізується робота пристрою.

X1 |

1 |

1 |

|

D1.1 |

|

X2 |

1 |

D2.1 |

|

||

|

D1.2 |

|

C

CK

1 |

f1 |

1 |

||

D4.1 |

|

|

||

|

|

D2.2 |

||

|

|

|

||

1 |

|

|

1 |

|

f |

|

D2.3 |

||

D4.2 |

2 |

|||

|

||||

|

|

|

||

|

|

|

1 |

|

|

|

|

D1.3 |

|

1 |

1 |

Q |

|

D2.4 |

|||

D5.1 |

|||

1 |

1 |

Q |

|

D5.2 |

|||

D3.1 |

|

|

a)

X2 |

1 |

&& |

|

||

C |

|

|

|

1 |

|

X1 |

|

|

CK

|

|

& |

& |

f1 |

& |

& |

|

& |

|

f2 |

|

|

|

& |

&

&

&

Q

Q

б)

Рисунок 10 - Схема тригерів, що синтезувалися: а) тригер за M-S схемою на елементах АБО-НІ; б)тригер за схемою трьох тригерів на елементах І-НІ

Результатом даного етапу є часова діаграма сигналів у контрольних вузлах. На вимогу викладача студент повинен продемонструвати процес отримання часової діаграми.

10.Проведіть аналіз отриманих часових діаграм.

11. Згідно з розробленими схемами рисунка 10 визначте повний час

перемикання тригера tзΣ , мінімальну довжину tTmin та максимальну частоту fTmax тактувальних сигналів.

Повний час перемикання схеми (рис.10, а), складають сума часової затримки tз елементів тригера та тривалість тактового імпульсу tT

tзΣ = 8 tз + tT.

Мінімальна тривалість тактового імпульсу у схемі (рисунок 10, а) визначається кінцем перехідних процесів в СУ та тригера RS, який керується при перемиканні С з 1 в 0, та дорівнює сумі часу затримки елементів тригера та складає

tTmin = 5tз.

Максимальна частота тактувального сигналу дорівнює fTmax = 1 / (tTmin - 2 tз)

4.3 Час попереднього установлення та затримки

З синхронизацією (тактуванням) тригера пов'язані два важливих параметри — час попереднього установлення tSU (Set-Up Time) і час затримки tH (Hold Time). Важливість цих параметрів обумовлена ще й тим, що вони притаманні не лише тригерам, а й іншим пристроям. Час tSU

—це інтервал до надходження синхросигналу, під час якого

інформаційний сигнал має залишатися незмінним. Час затримки tH — це час після надходження синхросигналу, під час якого інформаційний сигнал має залишатись незмінним. Дотримання часу попереднього установлення та затримки забезпечує правильне сприйняття тригером вхідної інформації.

Ряд інших часових параметрів тригерів безпосередньо пов'язано із затримками сигналу при проходженні через тригер і не потребує спеціальних пояснень.

II. Завдання. Нехай задана таблиця переходів на три вхідних сигнали (табл.12).

Дану тригерну комірку потрібно реалізувати за допомогою асинхронного тригера в базисі АБО-НІ.

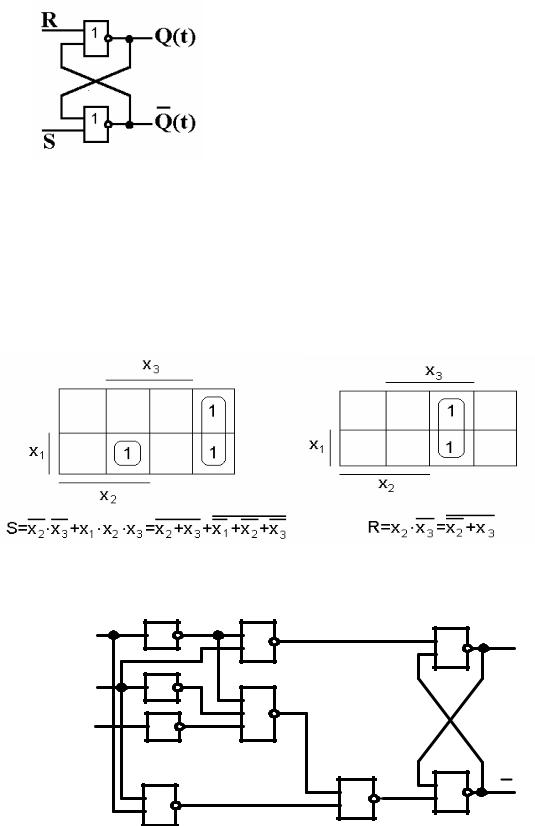

В базисі АБО-НІ схема тригера асинхронного типу має вигляд, показаний на рисунку 8. Логічне функціонування описується таблицею переходів (таблиця 13).

Таблиця 12 |

Таблиця 13 |

х1(t) |

х2(t) |

х3(t) |

Q(t+1) |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

Q(t) |

0 |

1 |

1 |

Q(t) |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

Q(t) |

1 |

1 |

1 |

1 |

|

|

|

|

х1(t) |

х2(t) |

х3(t) |

Q(t+1) |

R |

S |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

Q(t) |

0 |

0 |

0 |

1 |

1 |

Q(t) |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

Q(t) |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

Таблиця 14

R |

S |

Q(t+1) |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

Q(t) |

1 |

1 |

Х |

Рисунок 11Схема асинхронного тригера

Тоді, враховуючи, яким повинен бути стан тригерної комірки залежно від комбінації вхідних сигналів, (за таблицею переходів) перетворюємо таблицю переходів таким чином (таблиця 14).

За допомогою діаграм Вейча |

мінімізуємо функції S та R в базисі |

АБО-НІ, використовуючи для |

цього правило де Моргана. |

для функції S: |

для функції R: |

Рисунок 12 - Діаграми Вейча В результаті логічного синтезу схема тригерної комірки буде

виглядати таким чином (рис.13).

X 1 |

1 |

1 |

|

1 |

Q |

|

|

|

|

||

X 2 |

1 |

1 |

|

|

|

|

|

|

|

|

|

X 3 |

1 |

|

|

|

|

|

1 |

|

1 |

1 |

Q |

|

|

|

|||

|

|

|

|

|

Рисунок 13 – Схема синтезованого тригера

4.4 Синтез стандартного D-тригера на основі нестандартної тригерної комірки

Для цього перетворимо нестандартну тригерну комірку у стандартну, вважаючи доцільним використати тригер D-типу в данній серії елементів. Таблиця 14 є таблицею переходів для D-тригера. Виходячи із таблиці 12 та таблиці 14 можна отримати таблицю 15, з якої видно, що якщо на вході Х1 підтримувати постійно високу напругу (для цього можна використовувати шину живлення), а на вході Х2 підтримувати низьку напругу (використовувати шину „земля”), то вхід Х3 можна використовувати як D- вхід.

Таблиця 14

D |

Q(t+1) |

0 |

0 |

1 |

1 |

Таблиця 15

D |

Q(t+1) |

x1 |

x2 |

x3 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

Стандартна тригерна комірка на структурній схемі буде мати вигляд, як показано на рисунку 14.

X3 D |

|

|

|

|

f |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|||||||

|

1КОм |

|

|

|

|

s |

|

|

|

|

|

Q |

||

|

|

КС |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

RS |

|

|

|

||||

X1 |

|

|

|

fR |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

Q |

|||||

|

|

|

|

|

|

|

|

|

|

|||||

X2 |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 14 – Структурна схема стандартного тригера

4.5. Про деякі типові ситуації при побудові вузлів та пристроїв на основі стандартних ІС

Коефіцієнт об'єднання за входом (Коб) ЛЕ, коефіцієнт розгалуження за виходом (Кроз) ЛЕ та середній час затримки розповсюдження сигналу

ЛЕ (tзат.роз.сер.) вибираються згідно з варіантом з таблиці 4.

Згідно з даними таблиць вибирається принципова базова схема ЛЕ та її схемотехнічне виконання. Залежно від вимог можна використовувати різні серії мікросхем. При цьому необхідно вказати призначення елементів схеми, описати її функціонування.

Напругу джерел живлення, робочі струми, а також інші характеристики схеми логічного елемента, які не вказано в завданні, вибирає та обґрунтовує студент.

Вибрана принципова схема базового ЛЕ являє собою деяку сукупність певним чином з'єднаних компонентів. Компоненти, які входять до складу інтегральних схем, - це всі різновиди транзисторів, діодів,

конденсаторів та резисторів. Тому, залежно від типу ЛЕ, застосовують ті або інші активні компоненти, які необхідні. В курсовому проекті треба коротко описати їх функціонування та навести еквівалентну схему заміщення. При цьому необхідно вказати призначення елементів схеми, коротко описати її функціонування

Розроблена проектувальником функціонально-логічна схема підлягає далі реалізації на наборі стандартних ІС тієї чи іншої серії або бібліотечних елементів тієї чи іншої ВІС/СВІС з програмованою структурою. В обох випадках можливі незбігання елементів схеми, що підлягають реалізації, і тих, що наявні для реалізації. Типовими ситуаціями є присутність у наявних елементів "зайвих" (тих, що в даному випадку не використовуються,) входів, наявність в корпусах ІС зайвих елементів або, навпаки, нестача в наявних елементах числа входів чи навантажувальної здатності.

4.6 Режими входів, що не використовуються

Питання про режим "зайвих" входів розв'язується з урахуванням конкретного типу схемотехнології. Нехай, наприклад, потрібно отримати кон'юнкцію (або її інверсію) п'яти змінних. У стандартних серіях немає відповідних елементів з п'ятьма входами, тому доведеться взяти елемент з вісьмома входами, у якого виявиться три "зайвих" входи. Принципово це можливо зробити таким чином: не звертати уваги на "зайві" входи (тобто залишити їх розімкнутими), з'єднати їх із задіяними входами або подавати на них певні константи. З точки зору логічних операцій всі три можливості правомірні (рис. 7, а). Якщо ж врахувати особливості тієї чи іншої схемотехнології, то вибір варіанта дій стає визначеним.

Для ЕЗЛ розв'язок такий: входи, що не використовуються, залишаються розімкнутими. Це пояснюється тим, що в схемах самих елементів вже передбачено спеціальні резистори, що пов'язані з джерелом живлення, які забезпечують необхідні умови "зайвим" входам.

Для КМОН та ТТЛШ входи, що не використовуються, розімкнутими не залишають. Для КМОН це сувора рекомендація, оскільки в них дуже великі вхідні опори, і, внаслідок цього, на розімкнені входи легко наводяться паразитні потенціали, що можуть змінювати роботу схеми або пошкодити її. Для ТТЛШ суворої заборони на те, щоб залишити розімкнутими входи, немає, але так робити недоцільно, оскільки внаслідок цього постраждають параметри швидкодії елемента. З'єднання "зайвих" входів з задіяними для КМОН і ТТЛШ принципово можливо, але небажано, оскільки призводить до збільшення навантаження на джерело сигналу, що також супроводжується зменшенням швидкодії.

Таким чином, для КМОН і ТТЛШ режим входів, що не використовуються, - під'єдання їх до констант (логічних одиниць або

нулів), не змінюючи роботу схеми для задіяних входів. При цьому рівні напруг U1 та U0 для КМОН збігаються з рівнями Uдж та "землі", до яких і під'єднують входи, що не використовуються. У елементів ТТЛШ рівень U1 на 1,5..2 В нижче за рівень Uдж, тому для запобігання пробою входи, що не

використовуються, підключають до джерела живлення Uдж через резистори R (типова рекомендація R = 1 кОм), причому до одного резистора дозволяється під'єднувати до 20 входів.

Рисунок 15 – Принципово можливі (а) та рекомендовані (б) режими вмикання невикористаних входів

Приклади, що ілюструють перелічені способи підключення входів ІС, що не використовуються, показано на рисунку 15,б. Сигнали логічної одиниці можна отримувати від спеціального елемента, причому, якщо це потужний елемент, то він може мати коефіцієнт розгалуження до 30.

4.7 Режими елементів, що не використовуються

Якщо не всі елементи, що є в корпусі ІС, використані в схемі, то ті, що не використовуються, також підключені до напруги живлення, що є загальною для всього корпусу. Якщо ж потужності, які використовують елементи в станах нуля та одиниці, не однакові, то існує сенс поставити "зайвий" елемент в стан мінімальної потужності, подаючи на його вхід відповідну константу.

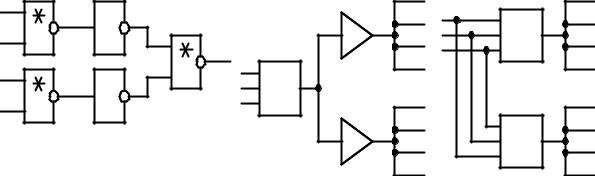

4.8 Нарощування числа входів

Для елементів І та АБО це не викликає труднощів. Для отримання

потрібного числа входів береться декілька елементів, виходи яких об'єднуються далі елементом того ж типу. Нарощування числа входів для операції І-НІ, АБО-НІ, загалом, відбувається аналогічним методом, але в схемі з'являються додаткові інвертори (рис. 16, а). На даному рисунку зірочка позначає операцію Шеффера або Пірса.

1 |

1 |

ЛЕ |

ЛЕ |

ЛЕ |

а) б) в) Рисунок 16 – Схема нарощування числа входів (а), та зниження

навантаження на виходах логічних елементів (б,в)

4.9 Зниження навантажень на виходах логічних елементів

Це може знадобитися, якщо навантаження перевищують задані значення, а також для підвищення швидкодії схем, на яку навантаження елементів мають безпосередній вплив. Чим більше число навантажень у елемента - джерела сигналу (або нестандартне зовнішнє навантаження), тим більший час витрачається на досягнення вихідним сигналом порогового рівня при перемиканні, тобто, на зміну його логічного стану. Для запобігання втрат швидкодії через навантаження на виходах перевантажених елементів застосовують буферизацію або розподіл навантаження (рисунок 13, б, в).

Уведення буферних каскадів прискорює роботу джерела сигналу, але вносить власну затримку у тракт передавання сигналу. Чи буде при цьому ефект прискорення, визначається конкретним розрахунком.

4.10 Аномальні стани тригерів

Під час використання тригерів доводиться стикатися з проблемою аномальних станів. Тригер швидко набуває одного із своїх стійких станів при визначеній дії на нього. Щоб запобігти невизначеності, для синхронних тригерів вводяться заборонені зони, в яких інформаційні сигнали не повинні змінюватись, - час попереднього установлення та затримки. Ясно, що при прийнятті по інформаційних входах асинхронних сигналів, що з'являються в довільні моменти часу, дотримуватися вимог до часу попереднього установлення та затримки неможливо, і тригер може потрапити під невизначені дії. Наприклад, тригер D може отримати сигнал