Зміст 1 покоління елементів комп’ютерної схемотехніки - 2ст

2 класифікація цифрових елементів -2ст

3 кодування двійкових цифр 2-3ст

4 функціонально та технічно повна система логічних елементів 3ст.

5 коефіцієнт обєднання та розгалуження. швидкодія елементів 3ст.

6 завадостійкість і надійність елементів 4ст.

7 логічні елементи НІ АБО І АБО-НІ І-НІ 4ст

8 прості та реверсивні лічильники 4ст

9 основні параметри лічильників 4ст

10 основні параметри лічильників. десяткові лічильники 5ст.

11 лічильники з одиничним кодуванням. основні області застосування лічильників в цифрових пристроях 5ст

12 дешифратори. загальна характеристика дешифраторів 6ст.

13 лінійні пірамідальні матричні багатоступеневі дешифратори 7-8ст

14 каскадування дешифраторів використання дешифраторів в комп’ютерах 9ст.

15 шифратори. загальна характеристика шифраторів 9ст

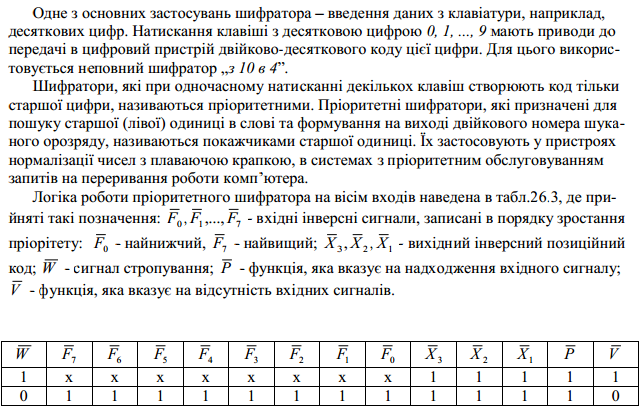

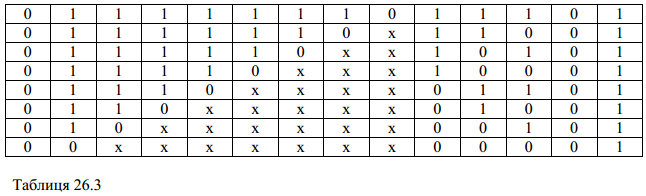

16 шифратори клавіатури пріоритетні шифратори 10ст

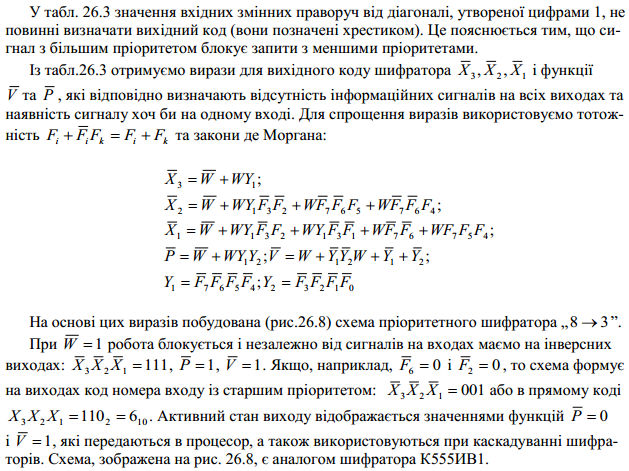

17каскадування шифраторів використання шифраторів у комп’ютерах 11ст

18 оперативно запам’ятовуючі пристрої 11ст

19 статичні ОЗП 12ст

20 динамічні ОЗП 12ст

21 організація елементів памяті та її параметри 13ст

22 регістри загальна характеристика регістрів 13ст

23 регістри фіксатори 14 ст

24способи запису інформації в регістрах 14ст

25 послідовні паралельні регістри 15ст

26 способи запису інформації в регістрах 15ст

27 реалізація арифметичних логічних циклічних зсувів 15ст

28 логічні операції в регістрах основні області застосування регістрів в комп’ютерах 16ст

49 Мультиплексори демультиплексор 17ст

50 загальна характеристика демльтиплексорів каскадування мультиплексорів 18ст.

51мультиплексори шин використання мультиплексорів у комп. 19

52загальна характеристика демультиплексорів каскадування демультиплексорів 19

53демультиплексори шин використання демультиплексорів у комп’ютерах 20

1

По типу фізичних пристроїв розрізняють такі покоління елементів еом:

|

1. (50 рр.) Електронною базою ЕОМ першого покоління були вакуумні лампи. Тисячі ламп розмішувалися в металевих шафах, які займали великі приміщення. Важила така машина декілька тон. Для її роботи потрібна була невелика електростанція. Для охолодження машини використовувались потужні вентилятори. Програмування здійснювалося в машинних кодах. Швидкодія становила декілька тисяч операцій за секунду. Ці машини мали невелику оперативну пам'ять. 2. (60 рр.) Електронною базою ЕОМ були транзистори, які замінили електронні лампи. Транзистори менше за лампи споживали енергію. Розміри ЕОМ зменшилися. З'явилися можливості програмування за рахунок мов програмування високого рівня та програмного забезпечення. До програмного забезпечення входили заздалегідь розроблені програми. Швидкодія машини досягала сотень тисяч операцій за секунду. Значно збільшилась оперативна пам'ять. Найбільш поширеними були такі: '"Еліот" (Англія), "Сіменс" (ФРГ), "Стренч", "СДС" (США) серія "Мінськ", "Урал". 3. (70 рр.) Електронною базою ЕОМ стали інтегральні схеми. Інтегральна схема формувалася на невеликій пластинці з чистого кременю, на яку наносилися у потрібній комбінації плівки різних призначень. Залежно від комбінації речей утворювалися елементи, які працювали як конденсатори опори. Таких елементів могло бути до декількох тисяч на квадратний сантиметр. Значно зросла швидкодія ЕОМ та обсяг оперативної пам'яті. Розвинуте програмне забезпечення та зручність у використанні забезпечували відкритий широкий доступ до ЕОМ. Така машина могла працювати з декількома програмами одночасно. Для зберігання інформації почали використовувати магнітні стрічки та магнітні диски. Почався перехід до баз популярної інформатики, 4. (80 рр.) Елементарною базою ЕОМ 4-го покоління є великі інтегральні схеми. На одному кристалі кременю стало можливим розмістити схему, яка відтворює роботу процесора ЕОМ. Такі однокристальні процесори називаються мікропроцесорами. Зросла швидкодія до міліарда операцій за секунду, обсяг оперативної пам'яті, зручність у використанні. Найпотужніший процесор 4-го покоління - "Ельбрус". На рівні 4-го покоління відбувся поділ на великі обчислювальні машини та персональні комп'ютери. 5. (90 рр) Елементарною базою ЕОМ 5-го покоління є підвищені інтегральні схеми, які містять до сотні тисяч елементів на квадратний сантиметр. 5 покоління - це не тільки нова елементарна база це прогрес та досягнення нових якісних зрушень у всіх галузях. У 1980 році Сенонський уряд оголосив десятирічну програму створення комп’ютерної системи 5-го покоління, яка базувалась би на використанні штучного інтелекту, експертного мислення та природної мови спілкування. 2 Набір цифрових мікросхем із спільними конструктційно-технологічними і схемотехнічними ознаками утворює серію ІМС. У комп'ютерній схемотехніці широко застосовуються цифрові напівпровідникові корпусні ІМС на основі кремнію і арсеніду галію. У напівпровідникових ІМС усі компоненти і з'єднання між ними виконані в об’ємі і на поверхні кристала площею від 4 до 100 мм2. У гібридних ІМС навісні компоненти кріпляться на поверхні діелектричної підкладки. У плівкових ІМС усі компоненти і з'єднання між ними виконані у виді тонких плівок на діелектричній підкладці.

|

|

|

3 |

|

Правила побудови ддк

Оскільки

всього існує 10 десяткових цифр, а одна

тетрада (4 біта) може визначати 24

= 16 різних комбінацій, то очевидно, що

існує більше ніж один можливий варіант

побудови ДДК. Кількість можливих

комбінацій дорівнює

![]() .

Більшість цих можливих комбінацій

подібні, тому для стандартизації був

вибраний спеціальний алгоритм генерації

ДДК. Кожному розряду ДДК ставиться якась

фіксована вага. Умови побудови коду:

.

Більшість цих можливих комбінацій

подібні, тому для стандартизації був

вибраний спеціальний алгоритм генерації

ДДК. Кожному розряду ДДК ставиться якась

фіксована вага. Умови побудови коду:

-

Ваги розрядів розміщуються у порядку зростання (від молодшого розряду до старшого)

-

Вага найменшого розряду q0 дорівнює 1

-

Вага наступного розряду q1 дорівнює 1 або 2

-

Ваги інших 2 розрядів підбираються так, щоб їхня сума була більша або рівна 6 (якщо q1 = 2) або 7 (якщо q1 = 1)

-

q3 <= q2 + q1 + q0 + 1

По таким правилам можлива побудова 17 різних кодів: 8-4-2-1, 7-4-2-1, 6-4-2-1, 5-4-2-1, 4-4-2-1, 7-3-2-1, 6-3-2-1, 5-3-2-1, 4-3-2-1, 3-3-2-1, 6-2-2-1, 5-2-2-1, 4-2-2-1, 6-3-1-1, 5-3-1-1, 4-3-1-1, 5-2-1-1

Кодування Для перетворення десяткової цифри у ДДК потрібно визначити, ваги яких розрядів утворюють у сумі дану цифру і поставити на їх місце одинички, а інші розряди заповнити нулями. Так, при кодування цифри 5 за допомогою 5221-ДДК видно, що q3 = 5, а отже 510 = 10005221-ДДК. Разом з тим, у даного коду є неоднозначність кодування, абсолютно коректним кодуванням буде 510 = 01115221-ДДК, оскільки q2 + q1 + q0 = 5. Неоднозначність кодування присутня у всіх кодах окрім 8421-ДДК. Декодування Декодування тетради ДДК відбувається як сумування ваг розрядів, навпроти яких записана 1 у двійковому представлені. Напркилад, 10106321-ДДК = 6·1 + 3·0 + 2·1 + 1·0 = 6 + 2 = 810. На відміну від кодування, декодування завжди однозначне.

4

Функціонально повна система логічних елементів дозволяє побудувати будь-яку складну логічну схему. Такі системи утворюються такими наборами логічних елементів: 1) ЧИ, НЕ; 2) І, НЕ; 3) НЕ ЧИ; 4) НЕ І та іншими. У технічно повній системі елементів забезпечується значення електричних параметрів двійкових сигналів, для цього використовуються допоміжні елементи – підсилювачі, повторювачі, формувачі та ін. З урахуванням вищевикладеного можна сказати, що система елементів являє собою функціонально і технічно повний набір елементів, який використовує однакові способи представлення інформації, а також має спільні конструктивно-технологічні характеристики.

5

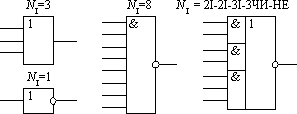

Коефіцієнт об'єднання за входом NI характеризує число логічних входів логічного елемента – зазвичай 1, 2, 3, 4 або 8 (рис.1.6).

Рис.

1.6. Приклади значень коефіцієнта NI

Коефіцієнт об'єднання за виходом N0 характеризує допустиму кількість з’єднаних між собою виходів логічних елементів з метою утворення нових функцій. Рис. 1.6. Приклади значень коефіцієнта NI

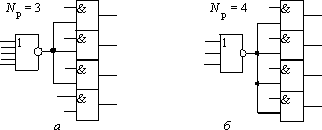

Коефіцієнт розгалуження за виходом Nр характеризує навантажувальну спроможність логічного елемента, тобто максимальне число входів ідентичних схем, яке може бути одночасно залучене до виходу даного елемента без порушення його працездатності (рис. 1.7). До складу серій ІМС зазвичай входять елементи з малою навантажувальною спроможністю (Nр = 3...15) та з великою (Nр = = 30...50).

Рис.

1.7. Підключення навантаження: а – Np

= 3; б – Np

= 4

Рис.

1.7. Підключення навантаження: а – Np

= 3; б – Np

= 4

6

Завадостійкість. Статична завадостійкість оцінюється за передавальним характеристикам логічного елемента як мінімальна різниця між значеннями вихідного і вхідного сигналів щодо порогового значення з врахуванням розкиду параметрів в діапазоні робочих температур:

U-ПОМ = U1вых.min – UПОР U+ПОМ = UПОР – U0вых.min У довідкових даних зазвичай наводиться одне допустиме значення перешкоди, яка не перемикає ЛЕ при допустимих умовах експлуатації.

Надійність є складною властивістю, і формується такими складовими, як безвідмовність, довговічність, відновлюваність і збереженість. Основним тут є властивість безвідмовності - здатність елемента безупинно зберігати працездатний стан протягом часу.

7

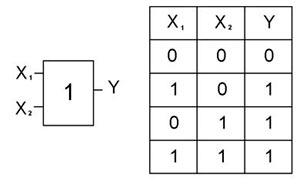

Схема «І» реалізує кон’юнкцію (логічне множення) двох або більш логічних значень. Одиниця на виході схеми «І» буде тоді і тільки тоді, коли на всіх входах будуть одиниці. Коли хоча б на одному вході буде нуль, на виході також буде нуль.

Операція кон’юнкції на функціональних схемах позначається знаком & (читається як «амперсэнд»), є скороченим записом англійського слова «and».

Схема «АБО» реалізовує диз’юнкцію (логічне складання) двох або більш логічних значень. Коли хоча б на одному вході схеми «АБО» буде одиниця, на її виході також буде одиниця. На схемі операція диз’юнкції позначається знаком «1».

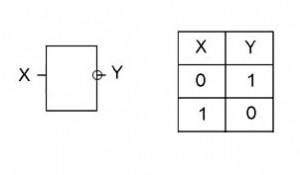

Схема

«НІ»

(інвертування) реалізує операцію

заперечення. Якщо на вході схеми 0, то

на виході 1. Коли на вході 1 на виході 0.

Для того щоб побачити різницю між простою

схемою і схемою заперечення слід

подивитись на позначення її виходу. На

початку виходу присутній притаманний

їй кружечок.

8

Лічи́льник (counter) — пристрій для підрахунку кількості сигналів, які надходять на його вхід.

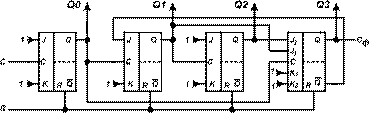

Двійкові лічильники реалізують лічбу вхідних імпульсів у двійковій системі числення.

Число розрядів n двійкового підсумовуючого лічильника для заданого модуля М знаходять із виразу n = log2М. Значення поточного числа N+ вхідних імпульсів n-розрядного підсумовуючого лічильника при відліку з нульового початкового стану визначають за формулою:

N+= Qi=2n-1 Qn+2n-2 Qn-1+...+20 Q1,

де 2i–1 – i-тий розряд; QiÎ{0,1} – логічне значення прямого виходу тригера i-го розряду. Розряди двійкового лічильника будуються на двоступеневих Т-тригерах або D-тригерах з динамічним керуванням по фронту синхросигналу (в лічильному режимі).

У двійковому підсумовуючому лічильнику перенесення Pi в сусідній старший розряд Qi+1 виникає в тому випадку, коли в момент надходження чергового лічильного імпульсу U+ всі молодші розряди находяться в одиничному стані, тобто Pi=U+QiQi–1...Q1=1. Після вироблення перенесення старший розряд перемикається в стан «1», а всі молодші розряди – в стан «0».

Асинхронні підсумовуючі лічильники на двоступеневих Т-тригерах будуються так, щоб вхідні імпульси U+ надходили на лічильний вхід тільки першого (молодшого) розряду. Сигнали перенесення передаються асинхронно (послідовно в часі) з прямих виходів молодших розрядів на Т-входи сусідніх старших.

9

Двійкові реверсивні лічильники мають переходи у двох напрямках: в прямому (при лічбі підсумовуючих сигналів U+) і в зворотному (при переліку віднімальних сигналів U–). Поточне значення різниці підрахованих імпульсів визначається із співвідношення åU+ – åU- = N – Nп де N – значення коду на прямих виходах тригерів лічильника; Nп – попередньо записане в лічильник початкове число. Розрізняють одноканальні та двоканальні реверсивні лічильники. В одноканальних реверсивних лічильниках підсумовуючі U+ і віднімальні U– сигнали почергово надходять на спільний лічильний вхід, а напрямок лічби задається напрямком кіл міжрозрядних перенесень або позик. Для перемикання міжрозрядних зв’язків у одноканальному реверсивному лічильнику потрібні додаткові керуючі сигнали.

Двоканальні реверсивні лічильники мають два лічильних входи: один для підсумовуючих імпульсів U+, другий – для віднімальних U–. Перемикання ланцюгів міжрозрядних зв’язків здійснюється автоматично лічильними сигналами: для переносів – імпульсами U+, для позики – імпульсами U–. Для задання напрямку лічбі використовують додатковий RS-тригер: з його прямого виходу знімається сигнал керування додаванням YД (вмикає кола перенесення), а з інверсного виходу – сигнал керування відніманням YВ (вмикає кола позики).

10

Основним статичним параметром лічильника є модуль рахунку М, який характеризує максимальну кількість імпульсів, після надходження яких лічильник встановлюється у початковий стан.Основним динамічним параметром, що визначає швидкодію лічильника, є час встановлення вихідного коду tk, який характеризує інтервал часу між моментом надходження вхідного сигналу і моментом встановлення нового коду на виході.

Двійково-десяткові лічильники реалізують лічбу імпульсів у десятковій системі числення, причому кожна десяткова цифра від нуля до дев’яти кодується чотирирозрядним двійковим кодом (тетрадою). Ці лічильники часто називають десятковими або декадними, оскільки вони працюють з модулем лічби, кратним десяти (10, 100, 1000 і т.д.).

Декада будується на основі чотирирозрядного двійкового лічильника, в якому вилучається надлишкове число станів. Вилучення зайвих шести станів у декаді досягається багатьма способами:попереднім записуванням числа 6 (двійковий код 0110); після лічби дев’ятого імпульсу вихідний код дорівнює 1111 і десятковий сигнал повертає лічильник у початковий стан 0110, отже, тут результат лічби фіксується двійковим кодом з надлишком блокування переносів: лічба імпульсів до дев’яти здійснюється у двійковому коді, після чого вмикаються логічні зв’язки блокування перенесень; з надходженням десятого імпульсу лічильник закінчує цикл роботи і повертається в початковий нульовий стан; введенням обернених зв’язків, які забезпечують лічбу в двійковому коді й примусовим перемиканням лічильника в нульовий початковий стан після надходження десятого імпульсу.

11

Лічильником називається послідовнісний пристрій, призначений для рахування вхідних імпульсів та фіксації їх числа в двійковому коді. Основним статичним параметром лічильника є модуль рахунку М, який характеризує максимальну кількість імпульсів, після надходження яких лічильник встановлюється у початковий стан. Основним динамічним параметром, що визначає швидкодію лічильника, є час встановлення вихідного коду tk, який характеризує інтервал часу між моментом надходження вхідного сигналу і моментом встановлення нового коду на виході.

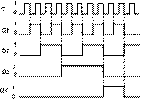

Десяткові лічильники Для створення лічильників, у яких ДоСЧ = 10, в двійкові лічильники вводять додаткові логічні зв'язки (прямі та оборотні). Таким способом одержують широко розповсюджені десяткові (декадні) лічильники з КЗЧ = 10, що мають 10 композицій вихідних сигналів. Такі лічильники працюють у відповідному двійковій-десятковому коді. Його відносять до числа зважених, так як кожен розряд має свою вагу.

а)

б)

Рис. 66. Тимчасова діаграма

десяткового асинхронного лічильника

(а);

схема лічильника (б)

а)

б)

Рис. 66. Тимчасова діаграма

десяткового асинхронного лічильника

(а);

схема лічильника (б)

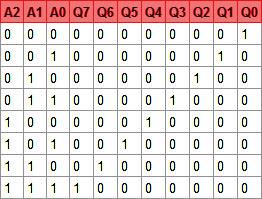

Число, записане в цих кодах, можна представити у вигляді суми N = a4 • Q4 + a3 • Q3 + a2 • Q2 + a1 • Q1, де а1 - а4 - ваги відповідних розрядів; Q1 - Q4 одиниця або нуль залежно від стану тригерів відповідного розряду. Більш часто застосовують двійково-десятковий код 8 - 4 - 2 - 1. Цифри в заголовку коду характеризують вагу тригерів лічильника, починаючи з останнього. При роботі схеми вживають синхронний чотирирозрядний двійковий лічильник, представлений на рис. 66, а. Схема робить рахунок у натуральному коді, але має обмежену ємність 10. Виходить так іменований десятковий (декадний) лічильник Binary Code Digital - BCD. Іменується так тому, що відлічує 10 станів, закодованих в двійковій формі з питомою вагою розрядів 1, 2, 4, 8. Щоб перетворити цей лічильник в декадний, працюючий в коді 8421, необхідно ввести оборотну зв'язок, який забезпечує його повернення в початковий стан при надходженні десятого імпульсу. Для цього вихід Q3 з'єднується з одним з J-входу Q1, і в результаті виходить схема, показана на рис. 66, а. Асинхронний лічильник працює так само, як і синхронний двійковий лічильник. У декадних лічильнику в коді 8421 тригер Q3 повинен перемикатися в «1» один раз.

12

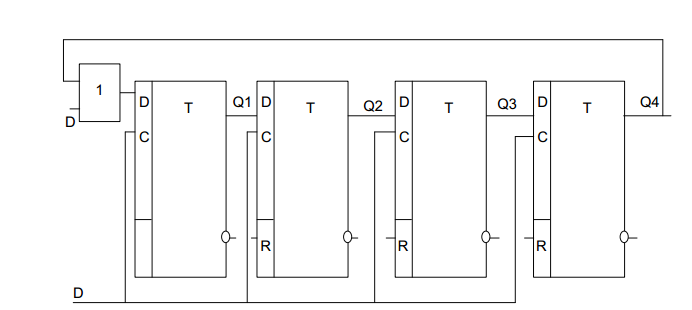

При

одиничному (унітарному) кодуванні стани

n-розрядного лічильника розрізняються

лише місцеположенням однієї одиниці,

яка називається маркуючим кодом; в інших

розрядах записані нулі. В окремих

випадках маркуючий код складається з

двох одиниць і називається парно-одиничним.

Лічильник з одиничним кодуванням – це

ланцюг тригерів, в якому забезпечується

зсув попередньо записаного маркуючого

коду по „кільцю” в напрямку старших

розрядів (прямий підрахунок) або молодших

(обернений підрахунок). Такі лічильники

часто називають кільцевими (за аналогією

з кільцевими регістрами зсуву). Лічильник

з одиничним кодуванням характеризується

модулем KСЧ = n і ємністю лічби Nmax = n -1.

Таким чином, число станів кільцевого

лічильника дорівнює його розрядності

і є значно меншим порівняно з іншими

типами лічильників. В кільцевих

лічильниках кожний розряд має вагу, яка

дорівнює номеру стану 0,1,2,...,(n-1). Із стану

(n-1) після надходження чергового імпульсу

лічильник утворює на виході сигнал

закінчення циклу (переповнення) і

повертається в початковий стан за

допомогою кола оберненого зв’язку з

виходу старшого розряду Qn на вхід

молодшого розряду Q1. Схема чотири

розрядного кільцевого лічильника

показана на рис.23.13а. Перед початком

роботи по входу D схеми АБО в молодший

розряд лічильника записується одиниця

і встановлюється початковий код Q4Q3Q2Q1=

0001. З надходженням кожного лічильного

імпульсу по входу синхронізації одиничний

код послідовно зсувається в бік старших

розрядів; при цьому молодші розряди,

виконані на D-тригерах з динамічним

керуванням, обнуляються. Після надходження

четвертого імпульсу лічильник повертається

в початковий стан за допомогою сигналу

з виходу Q4на вхід схеми АБО.

Лічильник є одним з основних функціональних вузлів комп’ютера, а також різних цифрових керуючих та інформаційно-вимірювальних систем. Основне застосування лічильників: - утворення послідовності адрес команд програми (лічильник команд або програмний лічильник); - підрахунок числа циклів при виконанні операцій ділення, множення, зсуву (лічильник циклів); - одержання сигналів мікро операцій і синхронізації; аналого-цифрові перетворення і побудова електронних таймерів (годинників реального часу).

12

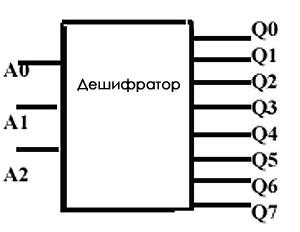

Дешифратор – це логічний пристрій який перетворює код числа, яке поступило на його вхід, в сигнал на одному з його виходів. Дешифратор досить важливий пристрій для електроніки цього часу, тому, що він являється складовою мікросхемотехніки і займає в ній своє місце. Дешифратор виконує зворотню функцію до шифратора і перетворює двійковий код на сигнал який виходить від одного з контактів. Наприклад вам потрібно відправити код 101 який передається по трьох контактах і для цього підійде дешифратор, який перетворить цей двійкових код на сигнал. Якщо до зворотньої сторони дешифратора підключити шифратор, то можна відновлювати потрібний двійковий код після його передачі на великі відстані. Всі цифрові пристрої які передають інформацію на великі відстані мають в собі дешифратор і шифратор, тому це краще та економічно вигідніше ніж збільшувати число проводів в кабелі. Число входів дешифратора зазвичай більше ніж число виходів. В природі трапляються такі види дешифраторів:

-

дешифратор 2 в 4; дешифратор 3 в 8; дешифратор 4 в 8;

-

дешифратор двійково-десяткового коду в двійковий;

-

дешифратор двійкового коду в код для 7-ми сегментного індикатора.

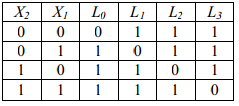

13

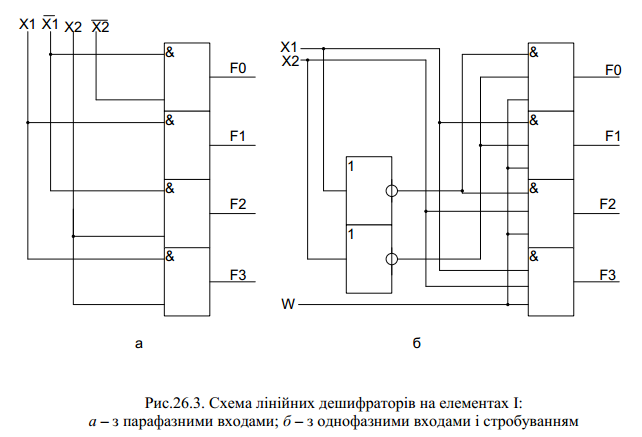

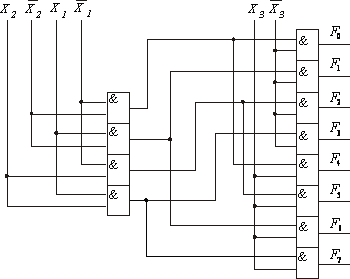

Лінійні

У

лінійному дешифраторі „з n в m” кожна

вихідна функція Fi реалізується повністю

окремим n-вхідним логічним елементом

при використанні парафазного вхідного

коду. Логіка роботи повних дешифраторів

на два входи X1, X2 і чо-тири прямих виходи

F0, F1, F2, F3 і чотири інверсних виходи L0,

L1, L2, L3 наведена в табл. 26.1 і 26.2 відповідно:

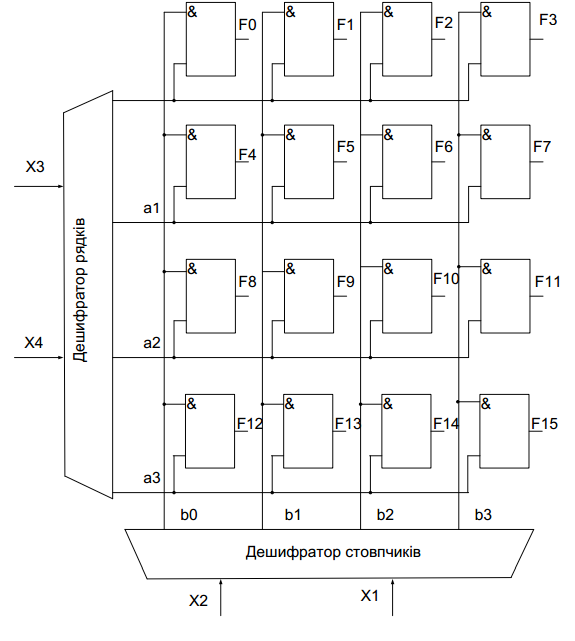

ПрямокутніПрямокутний

дешифратор будується за двоступеневою

схемою. При цьому вхідний код розбивається

на дві групи по n/2 розрядів при парному

n; при непарній розрядності групи вміщують

нерівне число змінних. Дві групи змінних

декодуються на першому ступені двома

повними лінійними дешифраторами, а на

другому ступені формуються вихідні

функції. Умовно вважають, що один з

дешифраторів першого ступеня формує

адреси матриці, а другий – адреси

стовпчиків матриці. На перетині ліній

рядків і стовпчиків підключається

двовходових схем збігу, які утворюють

другий, вихідний ступінь дешифратора.

При парному n матриця вентилів квадратна,

при непарному n – прямокутна. Тому такі

дешифратори

називають матричними, або прямокутними.

двовходових схем збігу, які утворюють

другий, вихідний ступінь дешифратора.

При парному n матриця вентилів квадратна,

при непарному n – прямокутна. Тому такі

дешифратори

називають матричними, або прямокутними.

Пірамідальні

У пірамідальному

дешифраторі число ступенів на одиницю

менше розрядності вхідного коду, тобто

K=n–1. В усіх ступенях використовуються

тільки двовходові логічні елементи. На

першому ступені використовуються

лінійні дешифратори на два входи і

чотири виходи. Число логічних елементів

у кожному ступені дорівнює Mi=2i+1, де i=1,

2, ..., k. Це означає, що кожен подальший

ступінь має в два рази більше елементів,

ніж попередній. Вихід елемента i-го

ступеня підключається до входів тільки

двох елементів (i+1)-го ступеня.

Пірамідальна

структура для реалізації повного

дешифратора "з 3 в 8" описується

системою мінтермів виду:

![]() Схема

пірамідального дешифратора з парафазним

вхідним кодом на три входи і вісім

виходів показана на рис.6.5.

На першому

ступені дешифруються змінні X2 і X1, на

другому ступені добавляється розряд

X3. При більшому числі розрядів дешифрованого

коду, наприклад, n>10, дешифратор в n/4

економічніше лінійного.

Схема

пірамідального дешифратора з парафазним

вхідним кодом на три входи і вісім

виходів показана на рис.6.5.

На першому

ступені дешифруються змінні X2 і X1, на

другому ступені добавляється розряд

X3. При більшому числі розрядів дешифрованого

коду, наприклад, n>10, дешифратор в n/4

економічніше лінійного.

Рис.

6.5. Схема пірамідального дешифратора

на три входи і вісім виходів

Рис.

6.5. Схема пірамідального дешифратора

на три входи і вісім виходів

Основним недоліком пірамідального дешифратора є велике число ступенів, що суттєво збільшує час дешифрації коду.

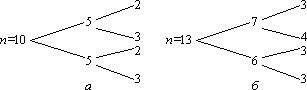

Багатоступеневі

Принцип

побудови багатоступеневих дешифраторів

полягає у послідовному розбитті вхідного

багаторозрядного коду до отримання у

кожній групі двох - трьох розрядів. Як

приклад на рис. 4.7 показано розбиття

коду, який дешифрується для n=10 и n=13.

Після цього багатоступенева схема

дешифратора зображується у вигляді

з’єднання ряду лінійних схем.

Рис.

6.7. Розбиття вхідного коду, який

дешифрується на групи: а – при n=10; б –

при n=13

Рис.

6.7. Розбиття вхідного коду, який

дешифрується на групи: а – при n=10; б –

при n=13

14

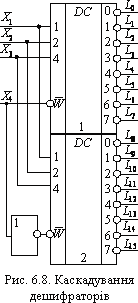

Під

каскадуванням (нарощуванням) розуміють

спосіб з’єднання дешифраторів у вигляді

мікросхем середнього ступеня інтеграції

для одержання більшої розрядності

вхідного коду. З’єднання двох трирозрядних

дешифраторів типу K555ІД3 для декодування

чотирирозрядного коду показано на рис.

4.8.

Вхідні

змінні X1, X2 і X3 подаються паралельно на

входи обох дешифраторів: змінна X4

подається безпосередньо на вхід

стробування ![]() першого

дешифратора, через інвертор – на вхід

стробування другого дешифратора. Ця

каскадна схема працює так. Якщо значення

старшого розряду вхідного коду X4 = 0, то

в роботу включається перший дешифратор

з інверсними вісьмома виходами

L0,..., L7, при цьому другий дешифратор

блокований (вимкнений) і на його виходах

L8,..., L15 встановлюються високі рівні. При

X4=1 блокується перший дешифратор і

включається в роботу друга мікросхема.

Таким

чином, через наявність стробуючого

входу два трирозрядних дешифратори

утворюють схему дешифрації чотирирозрядного

коду.

першого

дешифратора, через інвертор – на вхід

стробування другого дешифратора. Ця

каскадна схема працює так. Якщо значення

старшого розряду вхідного коду X4 = 0, то

в роботу включається перший дешифратор

з інверсними вісьмома виходами

L0,..., L7, при цьому другий дешифратор

блокований (вимкнений) і на його виходах

L8,..., L15 встановлюються високі рівні. При

X4=1 блокується перший дешифратор і

включається в роботу друга мікросхема.

Таким

чином, через наявність стробуючого

входу два трирозрядних дешифратори

утворюють схему дешифрації чотирирозрядного

коду.

15

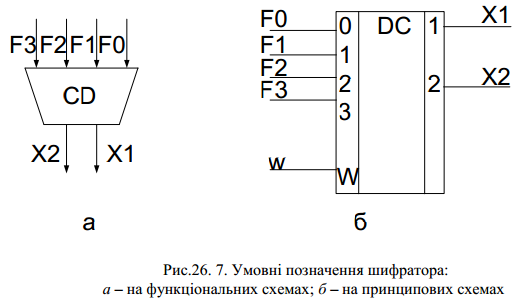

Шифратором називається функціональний вузол комп’ютера, призначений для перетворення вхідного m – розрядного унітарного коду у вихідний n – розрядний двійковий позиційний код. Двійкові шифратори виконують функцію, обернену функції дешифратора. При активізації однієї з вхідних ліній дешифратора на його виходах формується код, який відображає номер активного входу. Умовні графічні позначення шифраторів на схемах показані на рис. 26.7

Функція шифратора позначається буквами CD (coder). Входи шифратора нумеруються послідовними десятковими цифрами 0, 1, ..., m-1, а позначки виходів відображають ваги вихідних двійкових змінних 1, ..., 2n-1. У цифрових пристроях шифратори використовуються для таких операцій: перетворення унітарного вхідного коду у вихідний двійковий позиційний код; введення десяткових даних з клавіатури; показання старшої одиниці в слові; передачі інформації між різними пристроями при обмеженому числі ліній з’вязку.

16

17

Каскадування

шифраторів використовується для

збільшення розрядності вхідного слова.

Схема каскадування двох восьмивходових

шифраторів К555ИВ1 для пріоритетного

обслуговування 16-розрядного слова

.Розряди

.Розряди

старшого байта вхідного слова вступають

на перший шифратор CD1, а розряди

старшого байта вхідного слова вступають

на перший шифратор CD1, а розряди

молодшого байта подаються на другий

шифратор CD2.Вхід

молодшого байта подаються на другий

шифратор CD2.Вхід

має

найвищий пріоритет,

має

найвищий пріоритет,

- найнижчий. Інформаційні виходи обох

шифраторів об'єднуються за допомогою

логічних елементів АБО, утворюючи

трьохрозрядний інверсний код

- найнижчий. Інформаційні виходи обох

шифраторів об'єднуються за допомогою

логічних елементів АБО, утворюючи

трьохрозрядний інверсний код

,

Значення старшого розряду

,

Значення старшого розряду

забезпечується безпосередньо

сигналом

забезпечується безпосередньо

сигналом .Інформація

з виходів перший шифратора подається

на входи елементів АБО за допомогою

схем збігу ЛІ1 при

.Інформація

з виходів перший шифратора подається

на входи елементів АБО за допомогою

схем збігу ЛІ1 при

(мікросхема CD1 сприймає вхідні дані, a

CD2 - заблокована). Інформація з виходів

другого шифратора подається на входи

елементів АБО за допомогою схем збігу

ЛІ2 при

(мікросхема CD1 сприймає вхідні дані, a

CD2 - заблокована). Інформація з виходів

другого шифратора подається на входи

елементів АБО за допомогою схем збігу

ЛІ2 при

(мікросхема CD2 сприймає вхідні дані, CD1

- блокується).Схема працює в такий спосіб:

коли на вході є активний сигнал зі

старшого байта вхідного слова, наприклад,

(мікросхема CD2 сприймає вхідні дані, CD1

- блокується).Схема працює в такий спосіб:

коли на вході є активний сигнал зі

старшого байта вхідного слова, наприклад,

(

(

),

то працює шифратор CD1 і на виходах

елементів АБО формується інверсний код

),

то працює шифратор CD1 і на виходах

елементів АБО формується інверсний код

,

що відповідає прямому значенню

,

що відповідає прямому значенню

.

Якщо активний вхідний сигнал відноситься

до молодшому байту слова, наприклад,

.

Якщо активний вхідний сигнал відноситься

до молодшому байту слова, наприклад,

,

то працює шифратор CD2 (

,

то працює шифратор CD2 (

)

і на інверсних виходах формується код

)

і на інверсних виходах формується код

,

що відповідає прямому числа

,

що відповідає прямому числа

Шифратором називається функціональний вузол комп’ютера, призначений для перетворення вхідного m – розрядного унітарного коду у вихідний n – розрядний двійковий позиційний код.

18

Операти́вна па́м'ять (англ. Random Access Memory, дослівно — пам'ять з довільним доступом, первинна пам'ять) — пам'ять ЕОМ, призначена для зберігання коду та даних програм під час їх виконання. У сучасних комп'ютерах оперативна пам'ять переважно представлена динамічною пам'яттю з довільним доступом DRAM.

Протилежністю до пам'яті з довільним доступом є пам'ять з послідовним доступом. При довільному доступі, пам'ять організована таким чином, що в будь-яку мить можна отримати значення, записане в будь-якій комірці пам'яті, не переглядаючи інші комірки. При пам'яті з послідовним доступом, яка реалізується, наприклад, на магнітній стрічці, для доступу до певного елемента пам'яті потрібно прокрутити стрічку, зчитуючи інші елементи.

Види ЗПДД (запам'ятовуючий пристрій з довільним доступом) :

Напівпровідникова статична (SRAM) — комірками є напівпровідникові тригери. Переваги — невелике енергоспоживання, висока швидкодія. Відсутність необхідності проводити «регенерацію». Недоліки — малий обсяг, висока вартість. Нині широко використовується як кеш-пам'ять процесорів у комп'ютерах.

Напівпровідникова динамічна (DRAM) — кожна комірка є конденсатором на основі переходу КМОН-транзистора. Переваги — низька вартість, великий обсяг. Недоліки — необхідність періодичного прочитування і перезапису кожної комірки — т.з. «регенерації», і, як наслідок, зниження швидкодії, велике енергоспоживання. Процес регенерації реалізується спеціальним контролером, встановленим на материнській платі або в центральному процесорі. DRAM зазвичай використовується як оперативна пам'ять (ОЗП) комп'ютерів.

Феромагнітна — є матрицею з провідників, на перетині яких знаходяться кільця або біакси, виготовлені з феромагнітних матеріалів. Переваги — стійкість до радіації, збереження інформації при виключенні живлення; недоліки — мала ємність, велика вага, стирання інформації при кожному читанні. В наш час[Коли?] в такому, зібраному з дискретних компонентів вигляді, не застосовується.

Проте до 2003 року з'явилася магнітна пам'ять MRAM в інтегральному виконанні. Поєднуючи швидкість SRAM і можливість зберігання інформації при відімкненому живленні, MRAM є перспективною заміною типам ROM і RAM. Проте вона приблизно удвічі дорожча за мікросхеми SRAM (при тій же ємності і габаритах).

19

Статична оперативна пам'ять з довільним доступом ( SRAM , static random access memory ) - напівпровідникова оперативна пам'ять , в якій кожен двійковий або трійчастий розряд зберігається в схемі з позитивним зворотним зв'язком , що дозволяє підтримувати стан без регенерації , необхідної в динамічної пам'яті ( DRAM) . Тим не менш, зберігати дані без перезапису SRAM може тільки поки є живлення , тобто SRAM залишається енергозалежною типом пам'яті . Довільний доступ ( RAM - random access memory ) - можливість вибирати для запису / читання будь-який з бітів ( тритій ) ( частіше байтів ( Трайтен ) , залежить від особливостей конструкції) , на відміну від пам'яті з послідовним доступом ( SAM - sequential access memory ) .

20

Динамі́чна операти́вна па́м'ять або DRAM (Dynamic Random Access Memory) — один із видів комп'ютерної пам'яті із довільним доступом (RAM), найчастіше використовується в якості ОЗП сучасних комп'ютерів.

Основна перевага пам'яті цього типу полягає в тому, що її комірки упаковані дуже щільно, тобто в невелику мікросхему можна упакувати багато бітів, а значить, на їх основі можна побудувати пам'ять великої ємкості.

В сучасних комп'ютерах фізично DRAM-пам'ять представляє собою плату — модуль, на якому розміщуються мікросхеми пам'яті зі спеціалізованим з'єднувачем для підключення до материнської плати. Роль «комірок» відіграють конденсатори та транзистори, які розташовані всередині мікросхем пам'яті. Конденсатори заряджеються у випадку, коли в комірку заноситься одиничний біт, або розряжається у випадку, якщо в комірку заноситься нульовий біт. Транзистори потрібні для утримання заряду всередині конденсатора. За відсутності подачі електроенергії до оперативної пам'яті відбувається розряження конденсаторів і пам'ять спустошується. Ця динамічна зміна заряду конденсатора і є основним принципом роботи пам'яті типу DRAM. Елементом пам'яті такого типу є чутливий підсилювач (англ.sense amp), який підключений до кожного із стовпців «прямокутника». Він реагує на слабкий потік електронів, які рухаються через відкриті транзистори із обкладинок конденсаторів, і зчитує цілком всю сторінку. Саме сторінки і є мінімальною порцією обміну із динамічною пам'яттю, тому що обмін даними із окремо взятою коміркою нереальний.

21

Динамічна оперативна пам'ять або DRAM (Dynamic Random Access Memory) — один із видів комп'ютерної пам'яті із довільним доступом (RAM), найчастіше використовується в якості ОЗП сучасних комп'ютерів.Основна перевага пам'яті цього типу полягає в тому, що її комірки упаковані дуже щільно, тобто в невелику мікросхему можна упакувати багато бітів, а значить, на їх основі можна побудувати пам'ять великої ємкості.Принцип роботиВ сучасних комп'ютерах фізично DRAM-пам'ять представляє собою плату — модуль, на якому розміщуються мікросхеми пам'яті зі спеціалізованим з'єднувачем для підключення до материнської плати. Роль «комірок» відіграють конденсатори та транзистори, які розташовані всередині мікросхем пам'яті. Конденсатори заряджеються у випадку, коли в комірку заноситься одиничний біт, або розряжається у випадку, якщо в комірку заноситься нульовий біт. Транзистори потрібні для утримання заряду всередині конденсатора. За відсутності подачі електроенергії до оперативної пам'яті відбувається розряження конденсаторів і пам'ять спустошується. Ця динамічна зміна заряду конденсатора і є основним принципом роботи пам'яті типу DRAM. Елементом пам'яті такого типу є чутливий підсилювач (англ.sense amp), який підключений до кожного із стовпців «прямокутника». Він реагує на слабкий потік електронів, які рухаються через відкриті транзистори із обкладинок конденсаторів, і зчитує цілком всю сторінку. Саме сторінки і є мінімальною порцією обміну із динамічною пам'яттю, тому що обмін даними із окремо взятою коміркою нереальний.Характеристики пам'яті DRAMОсновними характеристиками DRAM є таймінги та робоча частота. Для звернення до комірок контролер задає номер банку, номер сторінкив ньому, номер стрічки та номер стовпчика. На ці всі запити використовується час. Крім того доволі великий період йде на відкриття та закриття самого банку після виконання операції. На кожну дію вимагається час, який називається таймінгом. Основними таймінгами DRAM є: затримка між подачею номеру стрічки і номера стовпчика, називається часом повного доступу (англ. RAS to CAS delay), затримка між подачею номеру стовпчика і отримання вмісту комірки, називається часом робочого циклу (англ. CAS delay), затримка між читанням останньої комірки та подачою номеру наступної стрічки (англ. RAS precharge). Таймінги вимірюються в наносекундах, і чим менша величина цих таймінгів, тим швидше працює оперативна пам'ять. Робоча частота вимірюється в мегагерцах, і збільшення робочої частоти пам'яті призводить до збільшення її швидкодії.Типи DRAMАсинхронна DRAMVideo RAMСторінкова пам'ятьШвидка сторінкова пам'ятьПам'ять із вдосконаленим виходом Синхрона DRAM Пакетна EDO RAMDDR SDRAM Direct RDRAM, або Direct Rambus DRAM DDR2 SDRAM

21

Організація взаємодії між процесором і пам'яттю визначає основні характеристики обчислювальної системи , інші елементи забезпечують зв'язок цієї ланки з зовнішніми пристроями із зовнішнім світом. Пам'ять з'єднується з керуючим пам'яттю контролером ( пристроєм управління пам'яттю ) по шині адреси , шині даних і шині керування . Розрядність шини даних визначає скільки двійкових розрядів одночасно ( паралельно) може бути лічено з пам'яті. Кожен двійковий розряд ( 1 біт ) зберігається елементом пам'яті. Елементи для пам'яті різного типу будуються на основі різних фізичних принципів запису і зберігання інформації. Елементи пам'яті об'єднуються в осередки пам'яті. При цьому всі елементи осередку адресуються одночасно , однаково і організовані так , що одночасно можуть видавати дані на шину даних. Такі об'єднані клітинки утворюють слово . Кількість розрядів даних , зчитувальних з пам'яті одночасно , називають довжиною вибірки . Для зберігання 1 байта використовується 8 елементів пам'яті , восьмибітних комірки пам'яті організовані з використанням шини даних шириною 8 ліній.З мікросхем пам'яті ( чипів ) створюються модулі пам'яті , які встановлюються в спеціальні слоти (роз'єми ) обчислювальної системи . Зараз найбільш поширені DIMM модулі - модулі пам'яті з двома рядами контактів.Розрядність адресної шини визначає адресний простір , тобто кількість елементів пам'яті , які можуть адресуватися безпосередньо . Якщо розрядність адресної шини - n , то кількість всіх можливих двійкових комбінацій ( кількість адрес ) визначиться як N = 2n.Характеристики пам'ятіПам'ять характеризується такими параметрами , як ємність , питома ємність , щільність запису , час доступу до пам'яті , пропускна здатність , надійність , вартість одиниці інформації. Вартість пам'яті визначається вартістю одного біта інформації.

22

Регістр — послідовний або паралельний логічний пристрій, який виконує функцію приймання, запам'ятовування і передавання інформації.

Інформація в регістрі зберігається за видом числа (слова), зображеного комбінацією сигналів 0 і 1. Кожному розряду числа, що записаний в регістр, відповідає свій розряд, побудований, як правило, на базі тригерів RS-, D- або JK- типу.

Класифікація регістрів

За способом запису і зчитування двійкової інформації

Послідовні

В послідовних регістрах запис і зчитування інформації здійснюється послідовно за часом, тобто почергово. Вони мають послідовні виходи. Інформація записується шляхом послідовного зсуву числа синхроімпульсами. Тому регістри послідовного типу носять назву регістрів зсуву.

Паралельні

В паралельних регістрах, які мають паралельні входи та виходи, запис інформації виконуються одночасно в усіх розрядах за один такт керування. Такі регістри називають регістрами пам'яті.

Паралельно-послідовні

Паралельно-послідовні регістри мають або паралельний вхід та послідовний вихід, або послідовний вхід та паралельний вихід. В перших регістрах інформація записується одночасно по паралельних входах, а зчитується почергово, в других — записується почергово, а зчитується одночасно. Паралельно-послідовні регістри можуть бути як регістрами зсуву, так і регістрами пам'яті.

За способом приймання та передавання інформації

-

Регістри типу SISO - з послідовним входом та послідовним виходом;

-

Регістри типу SIPO - з послідовним входом та паралельним виходом;

-

Регістри типу PISO - з паралельним входом та послідовним виходом;

-

Регістри типу PIPO - з паралельними входом та виходоми.

23

Регістр фіксації переривань Регістр фіксації переривань ( РФП ) - четирехбітних регістр , призначений для прийому запитів на переривання. Після виконання кожної команди і перед початком наступної Мікрооперацій РФПД : = РФП вміст регістра передається в додатковий регістр ( РФПД ) , на виході якого зібрана схема присвоєння пріоритету . Найбільш високий пріоритет у даній схемі має запит на програмне переривання ( РФПД = 1), потім запити на переривання від виклику супервізора ( РФПД = 2) , на зовнішні переривання ( РФПД = 3) і переривання від вводу-виводу ( РФПД = 4). Таким чином , за наявності одночасно декількох запитів в першу чергу виконується мікропрограма обслуговування програмних переривань ( яка полягає у зміні ССП програмного переривання ) , а в останню чергу - мікропрограма обслуговування переривань від введення-виведення . Підпрограми обслуговування переривань виконуються у зворотній послідовності , тобто починаючи з переривання , для якого зміна ССП виконана останньої. Біт 1 РФП призначений для прийому запитів на програмне переривання . Якщо переривання викликається відразу після появи порушень , біт встановлюється в одиницю Мікрооперацій РФП [1 ]: = 1 , якщо порушення аналізуються тільки наприкінці команди , то біт встановлюється в одиницю Мікрооперацій РФП [1 ]: = 1 (при РОЦ ≠ 0) , при якій аналізується наявність одиниці в одному з біт 1-3 , 7-15 РОЦ . При виконанні мікропрограми обслуговування програмних переривань біт 1 РФП скидається Мікрооперацій РФП [1]: = 0.

Біт 2 служить для прийому запитів на переривання за викликом супервізора . Біт встановлюється в одиницю Мікрооперацій РФП [2 ]: = 1 при виконанні команди ЗВЕРНЕННЯ ДО супервізори і скидається мікрокомандою РФП [2 ]: = 0 при виконанні мікропрограми обслуговування переривання за викликом супервізора .

Біт 3 призначений для прийому запиту на зовнішнє переривання . Біт встановлюється в одиницю синхросигналом С1 при появі одиниці в будь-якому бите регістру зовнішніх ліній 3 ( РВЛЗ ) або одиничному стані тригера переривання пульта управління ( ТППУ ) або тригера аварійного рахунки часу ( ТАСВ ) . Біт 3 скидається Мікрооперацій РФП [3 ]: = 0 при виконанні мікропрограми обслуговування зовнішніх переривань.

Біт 4 призначений для прийому запитів на переривання від введення-виведення . Сигналом від загального каналу біт встановлюється в одиницю і скидається Мікрооперацій РФП [4 ]: = 0 при виконанні мікропрограми обслуговування переривань вводу- виводу.

Біти 1-4 РФП скидаються по сигналу « Скидання » при виконанні скидання системи за допомогою відповідних кнопок на пульті управління.

24

Регістр — послідовний або паралельний логічний пристрій, який виконує функцію приймання, запам'ятовування і передавання інформації.

Інформація в регістрі зберігається за видом числа (слова), зображеного комбінацією сигналів 0 і 1. Кожному розряду числа, що записаний в регістр, відповідає свій розряд, побудований, як правило, на базі тригерів RS-, D- або JK- типу.

Класифікація регістрів

За способом запису і зчитування двійкової інформації

Послідовні

В послідовних регістрах запис і зчитування інформації здійснюється послідовно за часом, тобто почергово. Вони мають послідовні виходи. Інформація записується шляхом послідовного зсуву числа синхроімпульсами. Тому регістри послідовного типу носять назву регістрів зсуву.

Паралельні

В паралельних регістрах, які мають паралельні входи та виходи, запис інформації виконуються одночасно в усіх розрядах за один такт керування. Такі регістри називають регістрами пам'яті.

Паралельно-послідовні

Паралельно-послідовні регістри мають або паралельний вхід та послідовний вихід, або послідовний вхід та паралельний вихід. В перших регістрах інформація записується одночасно по паралельних входах, а зчитується почергово, в других — записується почергово, а зчитується одночасно. Паралельно-послідовні регістри можуть бути як регістрами зсуву, так і регістрами пам'яті.

За способом приймання та передавання інформації

-

Регістри типу SISO - з послідовним входом та послідовним виходом;

-

Регістри типу SIPO - з послідовним входом та паралельним виходом;

-

Регістри типу PISO - з паралельним входом та послідовним виходом;

-

Регістри типу PIPO - з паралельними входом та виходоми.

25.

За способом запису і зчитування двійкової інформації[ В послідовних регістрах запис і зчитування інформації здійснюється послідовно за часом, тобто почергово. Вони мають послідовні виходи. Інформація записується шляхом послідовного зсуву числа синхроімпульсами. Тому регістри послідовного типу носять назву регістрів зсуву.

В паралельних регістрах, які мають паралельні входи та виходи, запис інформації виконуються одночасно в усіх розрядах за один такт керування. Такі регістри називають регістрами пам'яті.

Паралельно-послідовні регістри мають або паралельний вхід та послідовний вихід, або послідовний вхід та паралельний вихід. В перших регістрах інформація записується одночасно по паралельних входах, а зчитується почергово, в других — записується почергово, а зчитується одночасно. Паралельно-послідовні регістри можуть бути як регістрами зсуву, так і регістрами пам'яті.

26

Інформація в регістрі зберігається за видом числа (слова), зображеного комбінацією сигналів 0 і 1. Кожному розряду числа, що записаний в регістр, відповідає свій розряд, побудований, як правило, на базі тригерів RS-, D- або JK- типу.

На регістрах можна виконувати операції перетворення інформації з одного виду на інший, наприклад, послідовного коду на паралельний. Регістри можуть використовуватися для виконання деяких логічних операцій, наприклад, логічне порозрядне множення.

27