- •1)Дизъю́нкция

- •2) Конъю́нкция

- •3) Инверсия

- •4) Переместительный закон

- •5)Сочетательный закон

- •6. Распределительный закон

- •7.Законы поглощения

- •8. Правило склеивания

- •9. Правило де Моргана

- •10.Стрелка Пирса

- •13. Транзисторные ключи

- •14. Электронная логическая схема операции не.

- •15. Электронная логическая схема операции или

- •18. 19Схема на логических элементах – мультивибратор.

- •20.Схема на логических элементах – одновибратор.

- •21. Схема на логических элементах – мультивибратор.

- •25. Схема на логических элементах – синхронный rs-триггер

- •26.Схема на логических элементах – d-триггер.

- •27.Схема на логических элементах – синхронный jk-триггер.

- •28.Схема на логических элементах – dv-триггер

- •29.Типовой узел цифровых устройств – регистр.

- •30.Типовой узел цифровых устройств – счетчик импульсов.

- •31.Типовой узел цифровых устройств – сумматор.

- •32.Регистр состояния status микроконтроллера pic16f877

- •33. Организация памяти микроконтроллера pic16f877.

- •35.Использование тактового генератора для микроконтроллера pic16f877.

- •44.Характеристика микроконтроллера pic16f877.

- •45.Отладочные средства микроконтроллера pic16f877

- •47. Флаги регистров специального назначения.

29.Типовой узел цифровых устройств – регистр.

Регистры – это узлы ЭВМ, служащие для хранения информации в виде машинных слов или его частей, а так же для выполнения над словами некоторых логических преобразований. Они представляют собой цифровые автоматы Мили, выполненные на триггерах.

Регистры способны выполнять следующие операции:

- установка регистра в состояние 0 или 1 (на всех выходах);

- прием и хранение в регистре n разрядного слова;

- сдвиг хранимого в регистре двоичного кода слова в право или в лево на заданное значение разрядов;

- преобразование кода хранимого слова в последовательный, и наоборот, при приеме или при выдачи двоичных данных;

- поразрядные логические операции.

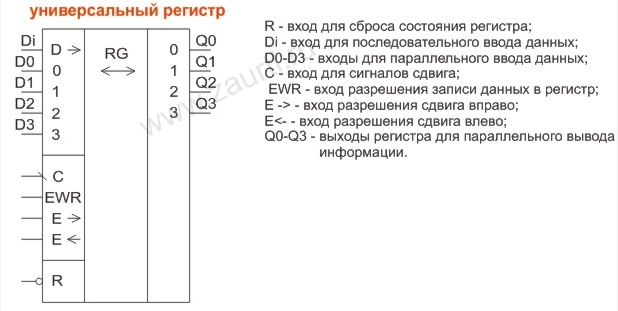

Ниже показано условно графическое обозначение универсального регистра и назначение его выводов:

30.Типовой узел цифровых устройств – счетчик импульсов.

Цифровым счетчиком импульсов называют последовательностный цифровой узел, который осуществляет счет поступающих на его вход импульсов. Результат счета формируется счетчиком в заданном кoдe и может храниться требуемое время.

Счетчики строят на Т-триггерах и ТV-триггерах с применением при необходимости логических элементов в цепях межразрядных связей. Количество триггеров N должно быть таким, чтобы множество внутренних состояний счетчика 2N было не меньше максимального числа импульсов, которое должно быть зафиксировано. С приходом очередного счетного импульса изменяется состояние счетчика, которое в заданном коде отображает результат счета.

Считывание результата параллельным N-разрядным кодом может быть произведено после каждого счетного импульса. Если количество счетных импульсов не ограничивать, то счетчик будет работать в режиме деления их числа на коэффициент (модуль) счета Ксч равный 2N. Через каждые 2N импульсов он будет возвращаться в начальное состояние и снова считать импульсы. Эта операция называется делением, а счетчики, ее осуществляющие, делителями.

Если необходимый коэффициент счета не равен 2N применяют различные способы сокращения числа внутренних состояний счетчика. Для построения счетчика могут применять не только триггеры со счетным входом, но и D-триггеры, и JК-триггеры двухступенчатой структуры или с динамическим управлением.

Счетчики можно классифицировать по ряду признаков. По направлению счета их делят на суммирующие (с прямым счетом), вычитающие

(с обратным счетом) и реверсивные. В суммирующих счетчиках с приходом очередного счетного импульса результат увеличивается на единицу, в вычитающих – уменьшается на единицу. Реверсивными называются счетчики, которые могут работать как в режиме суммирующего счетчика, так и в режиме вычитающего счетчика.

По способу организации переноса различают счетчики с последовательным, параллельным и комбинированным (параллельно-последовательным) переносом.

Конструктивно цифровые счетчики могут быть выполнены в виде совокупности интегральных микросхем-триггepов определенным образом соединенных, и в виде одной микросхемы повышенного уровня интеграции, содержащей сформированную на единой подложке.