- •Курсовая работа

- •2001 Г. Задание на курсовую работу

- •Упрощение заданной функции.

- •Справочные данные и принятые обозначения.

- •Разработка электрической схемы в заданном схемотехническом базисе.

- •Расчет характеристик схемы с помощью программы pspice.

- •Технологический маршрут формирования n-моп транзистора.

- •Выводы по результатам курсовой работы

- •Список используемой литературы :

2001г.

Московский институт электронной техники.

Курсовая работа

по курсу “Микроэлектроника и микросхемотехника”

По теме: ”Проектирование логического

элемента в n-МОП базисе”

Преподаватель Миндеева А. А.

Выполнил студент гр.

2001 Г. Задание на курсовую работу

В рамках курсовой работы необходимо:

Минимизировать заданную логическую функцию с учетом схемотехнического базиса.

Разработать электрическую схему логического элемента в заданном схемотехническом базисе. Рассчитать параметры компонентов.

Провести расчет передаточных и переходных характеристик на PC по программе PSPICE.

Предложить технологический маршрут изготовления логического элемента.

Разработать топологию логического элемента в соответствии с предложенным технологическим маршрутом и топологическими допусками.

Заданная функция имеет вид:

![]()

![]()

Упрощение заданной функции.

У![]() прощение

функции производится с помощью карты

Карно. Так как логическая функция

задана в совершеннодезъюктивной

нормальной форме, то карта Карно

заполняется по1,или когдахотя бы одно слагаемое принимает

значение равное1:

прощение

функции производится с помощью карты

Карно. Так как логическая функция

задана в совершеннодезъюктивной

нормальной форме, то карта Карно

заполняется по1,или когдахотя бы одно слагаемое принимает

значение равное1:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Заполненная карта Карно выглядит так:

|

CD |

00 |

01 |

11 |

10 |

|

00 |

1 |

1 |

1 |

1 |

|

01 |

1 |

0 |

0 |

1 |

|

11 |

0 |

0 |

0 |

0 |

|

10 |

1 |

1 |

1 |

1 |

Для считывания F с карты Карно необходимо сначало минимизировать F по единицам,то есть объединяем соседние состояния, при которых F принимает одинаковые состояния. Здесь объединяются квадраты по четыре состояния. Одно состояние может войти в несколько объединений. В результате объединения записываются те переменные, которые не меняются при переходе из клетки в клетку.

![]()

После считывания проводятся преобразования к нужному элементному базису при использовании теоремы диМоргана и двойной инверсии, в итоге мы получим:

![]()

Справочные данные и принятые обозначения.

Толщина изолирующего диэлектрика dSiO2 = 50нМ

Емкость нагрузки С=0,5 пФ

Материал подзатворного диэлектрика – окись кремния (SiO2)

Относительная диэлетрическая проницаемость SiO2 = 4

Диэлектрическая проницаемость ваккума 0 = 8,85*10-12 Ф/м

Подвижность электронов n = 600 см2/В*с

Подвижность дырок p = 300 см2/В*с

Глубина диффузии хJ= 0.7 мкм

Коэффициент влияния подложки = 0,15

Минимальный топологический размер = 1 мкм

Напряжение логического нуля U0 = 0,2 В

Напряжение логической единицы U1 = 5 В

Напряжение помехоустойчивости Uпу = 0,5 В

Средняя потребляемая мощность Рср = 0,8 мВт

В данном варианте задан ключ с квазилинейной нагрузкой и с алюминиевым затвором.

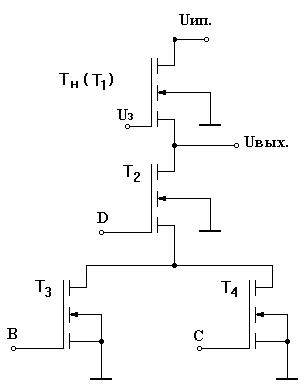

Разработка электрической схемы в заданном схемотехническом базисе.

После упрощения функции, в соответствии с заданной нагрузкой,

получаем следующую элетрическую схему:

Аналитический расчет

параметров транзисторов схемы.

По заданным параметрам определяем Uпор.0 :

Uпор.0 = U0+U0пу = 0,2+0,5=0.7 (В)

Далее находим численные значения следующих величин Uип Uз :

Uип = U1 = 5 (В)

Uз Uип*(1+)+Uпор0 = 5*(1+0,15)+0.7 = 6.45 7 (В )

Определяем значение I0:

Рср=(Р0 + Р1) /2 ; Р1 = 0

Рср = Р0/2 = (Uип * I0)/2

В итоге получаем :

I0 = 2*Рср/Uип = (2*0,8*10-3) / 5 = 0,32*10-3 = 0,32 ( мА )

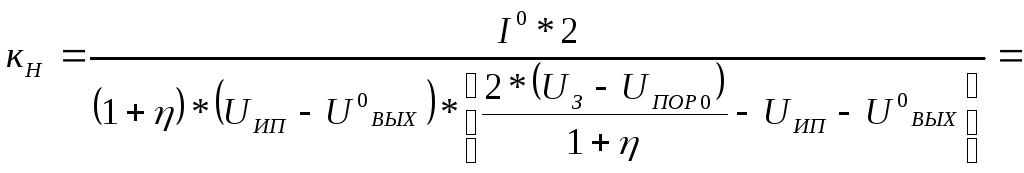

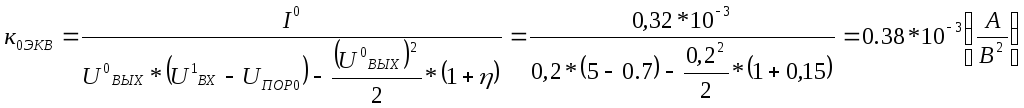

Крутизна нагрузочного транзистора (кн) определяется из следующего выражения :

![]()

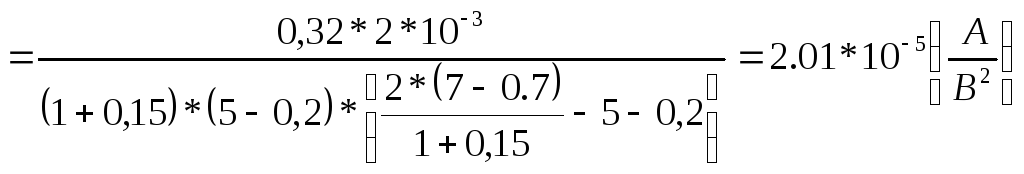

Затем определяем крутизну для остальных транзисторов:

Найденное к0экв - для схемы в целом. Определим крутизну для каждого транзистора по отдельности, в соответствии с его включением. У параллельно включенных транзисторов крутизна равна, а у последовательно включенных :

1/кэкв = 1/к1 + 1/к2 = 2/к

к=2*кэкв

В итоге, крутизны для каждого транзистора примут следующие значения:

Для D- В- С- сигналов:к=2*кэкв=2*0.38*10-3 = 0.76*10-3 (А/В2)

В следующем пункте определим геометрические размеры каждого транзистора по следующей методике :

к = куд*W/L

куд = *Суд

Суд = 0*SiO2/dок

а=W/L=к/куд

При а1 L = Lmin, W = Lmin*а;

При а1 L = Wmin/a, W = Wmin.

Для транзисторов с поликремниевым (Al) затвором :

Lmin = 3*

Wmin= 2*

Суд = 0*SiO2/dок = 4*8.85*10-12/50*10-9 = 0.708*10-3 (Ф)

Так как транзистор n-канальный, то = n= 600 (см2/В*с) :

куд = *Суд = 600*10-4*0,708*10-3 = 424,8*10-7 (А/В2)

Геометрические размеры транзисторов T2 Т3 Т4:

а=W/L=к/куд = 0,76*10-3/424,8*10-7 = 17.99,

так как а1, то L = Lmin= 3*= 3 (мкм).

W = a*Lmin= 17.99*3 = 53.99 54 (мкм).

Геометрические размеры для нагрузочного транзистора Тн (Т1):

к=кн = 2.01*10-5 (А/В2)

а = к/куд = 2.01*10-5/42,48*10-6 = 0.474

так как а1, то W = Wmin.= 2* = 2 (мкм),

L = Wmin/ a = 2/0,474 = 4.22 5 (мкм).

AB

AB