- •Глава 1 3

- •1.1. Компенсация реактивной мощности

- •1.2. Промышленные потребители реактивной мощности

- •1.3. Устройства компенсации реактивной мощности

- •1.4. Основные положения проектирования микропроцессорных устройств.

- •1.5. Техническое задание на разработку контроллера - компенсатора реактивной мощности

- •1.6. Общая характеристика

- •1.7. Обоснование элементной базы

- •1.7.1. Микропроцессор и микропроцессорный комплект

- •1.7.2. Память и логические элементы

- •1.7.3. Силовые элементы

- •1.8. Аппаратные средства контроллера

- •1.8.1. Плата контроллера

- •1.8.2. Плата тиристорного управления

- •1.8.3. Блок питания

- •1.8.4. Подключение контроллера – компенсатора

- •1.9. Алгоритмы контроля и управления

- •1.9.1. Измерение тока, напряжения и угла

- •1.9.2. Принцип управления конденсаторной установкой

- •1.10 Программное обеспечение контроллера

- •1.10.1. Структура программного обеспечения

- •1.10.1.1. Основная программа

- •1.10.1.2. Подпрограмма обработки прерывания trap

- •1.10.1.3. Подпрограмма обработки прерывания rst 7.5

- •1.10.1.4. Комплекс подпрограмм типа bios

- •1.10.2. Распределение адресного пространства

- •Область векторов прерываний

- •X8085.Exe

- •2.3. Аппаратные средства отладки

- •2.4. Программные средства отладки Сервисная программа контроллера-компенсатора

- •2.5. Конструктивное исполнение

- •2.6. Методика поиска неисправностей

- •Глава 3

- •4.1. Состояние и анализ безопасности жизнедеятельности в помещении лпэ

- •4.2. Основные мероприятия и технические средства по обеспечению безопасных и безвредных условий труда в помещении лпэ.

- •4.3. Мероприятия и технические средства по предупреждению чрезвычайных ситуаций и ликвидация их последствий

- •4.3. Мероприятия и технические средства по охране атмосферного воздуха в районе объекта

- •4.5. Расчет молниезащиты здания

- •Глава 5 Заключение

- •Литература

1.7.2. Память и логические элементы

Ниже приведены данные о выбранных микросхемах памяти и ИС логических элементов. Выбор микросхем был сделан исходя из функциональных требований и требований к энергопотреблению.

К573РФ4 – репрограммируемое ПЗУ.

Схема К573РФ4 относится к серии репрограммируемых постоянных ЗУ с длительным сроком хранения информации при включённом и выключенном источнике питания, с электрической записью информации и стиранием информации ультрафиолетовым светом. Она выполнена по nМОП – технологии «с плавающим» затвором [7].

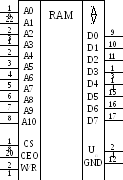

Условное графическое обозначение микросхемы К573РФ4 представлено на рисунке 1.7.2.1.

Рисунок

1.7.2.1. Условное графическое обозначение

К573РФ4 (

Назначение выводов: 2, 3 - 10, 21, 23, 24, 25 –

адресные входы; 11 - 13, 15 - 19 – входы -

выходы данных; 20 – выбор микросхемы;

22 – разрешение по выходу; 27 – сигнал

программирования; 28 – напряжение

питания; 1 – напряжение программирования;

14 - общий; 26 - свободный.)

В таблице 1.7.2.1 приведена таблица истинности микросхемы К573РФ4.

Таблица 1.7.2.1.

Таблица истинности микросхемы К573РФ4

|

C |

CEO |

PR |

A0 – A12 |

UPR |

D0 – D7 |

Режим работы |

|

H |

X |

X |

X |

UCC |

Roff |

Хранение (невыбор) |

|

L |

L |

H |

A |

UCC |

Выходные данные в прямом коде |

Считывание |

|

L |

H |

H |

A |

UCC |

Roff |

Отключение выходов |

|

L |

H |

L |

A |

21,5 0,5B |

Входные данные в прямом коде |

Программирование |

|

L |

H |

H |

A |

21,5 0,5B |

Roff |

Запрет программирования |

|

H |

H |

L |

A |

21,5 0,5B |

Roff |

Запрет программирования |

Параметры микросхемы К573РФ4.

Информационная ёмкость 64 Кбит

Организация, слов разрядов 8192 8

Время выборки адреса не более 300 нс.

Время выборки разрешения не более 120 нс.

Время хранения информации:

при включённых источниках питания не менее 25000 ч.

при выключённых источниках питания не менее 100000 ч.

Напряжение питания UCC = 5В 5%

Напряжение программирования UPR = 5В 5%

Суммарная потребляемая мощность не более 420 мВт.

Диапазон температур - 45 … +70С

Выход три состояния

Совместимость по входу и выходу с ТТЛ схемами

Тип корпуса металлокерамический

КР537РУ10 – статическое ОЗУ.

Микросхема КР537РУ10 относится к группе асинхронных. Она имеет словарную организацию и допускает запись (считывание) информации восьмиразрядными словами. Входы и выходы совмещены, и поэтому соответствующие выводы микросхем обладают свойством двунаправленной проводимости. Записываемая и считываемая информация вводится в микросхему и выводится из неё по одним линиям, что определяет мультиплексный режим работы [8].

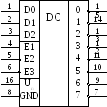

Рисунок

1.7.2.2. Условное графическое обозначение

К537РУ10 (

Назначение выводов: 1-8, 19, 22, 23 – адресные

входы; 9 - 11, 13 - 17 – входы - выходы данных;

18 – выбор микросхемы; 20 – разрешение

по выходу; 21 – сигнал записи - считывания;

24 – напряжение питания; 12 - общий ).

Другой

особенностью этой микросхемы является

наличие дополнительного сигнала

управления СЕО состоянием выхода. Он

может подаваться одновременно с сигналом

выбораCS

или с некоторой задержкой. Из таблицы

1.7.2.2. видно, что отсутствие разрешающего

значения этого сигнала не позволяет

вывести считываемую информацию. В этом

случае выходы находятся в третьем

состоянии. При наличии всех необходимых

для считывания сигналов только в момент

поступления разрешающего сигнала СЕО

выходы переходят в функциональное

состояние и спустя время tA(CEO)

на них

появляется информация.

Другой

особенностью этой микросхемы является

наличие дополнительного сигнала

управления СЕО состоянием выхода. Он

может подаваться одновременно с сигналом

выбораCS

или с некоторой задержкой. Из таблицы

1.7.2.2. видно, что отсутствие разрешающего

значения этого сигнала не позволяет

вывести считываемую информацию. В этом

случае выходы находятся в третьем

состоянии. При наличии всех необходимых

для считывания сигналов только в момент

поступления разрешающего сигнала СЕО

выходы переходят в функциональное

состояние и спустя время tA(CEO)

на них

появляется информация.

Таблица 1.7.2.2.

Таблица истинности микросхемы К537РУ10

|

CS |

CEO |

PR |

A0 – A12 |

UPR |

D0 – D7 |

Режим работы |

|

H |

X |

X |

X |

UCC |

Roff |

Хранение |

|

L |

X |

L |

A |

UCC |

L |

Запись 0 |

|

L |

X |

L |

A |

UCC |

H |

Запись 1 |

|

L |

L |

H |

A |

21,5 0,5B |

Данные в прямом коде |

Считывание |

|

L |

H |

H |

A |

21,5 0,5B |

Roff |

Запрет выхода |

Параметры микросхемы К537РУ10.

Информационная ёмкость 16384 бит

Организация 2048 слов 8 разрядов

Время выборки адреса не более 220 нс.

Напряжение питания UCC = 5В 5%

Потребляемая мощность:

в режиме обращения 370 мВт.

в режиме хранения:

при UCC = 5,25 В 5,25 мВт.

при UCC = 2 В 0,6 мВт.

Диапазон температур - 10 … +70С

Выход три состояния

Совместимость по входу и выходу с ТТЛ- и КМОП- схемами

Тип корпуса пластмассовый

К555ИД7 – двоичный дешифратор (К531, К555)

Микросхема К555ИД7 (условное графическое обозначение и назначение выводов представлено на рисунке 1.7.2.3.) обеспечивает преобразование 3 – разрядного двоично-десятичного числа в десятичное число от 0 до 7 на последовательности выходов дешифратора. Трёхвходовая первая ступень выполнена на шести инверторах, восьмивыходная вторая ступень – на восьми логических элементах И – НЕ. Выход дешифратора выбранного канала имеет низкий уровень, остальные выходы – высокий.

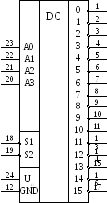

Рисунок

1.7.2.3. Условное графическое обозначение

К555ИД7

( Выводы: 1 – 3 – информационные выходы;

4 – 6 входы разрешения; 8 – общий; 7, 9 –

15 – выходы; 16 – Uп.)

Дешифратор

имеет шину разрешения, поэтому ЛЭ И –

НЕ второй ступени выполнены с четырьмя

входами (один вход разрешения дополнительно

к трём входам адреса канала). Шина

разрешения дешифратора управляется 3

– разрядным числом в функции

![]() .

Вход Е1

может быть использован в качестве входа

выбора данного дешифратора, входы Е2,

Е3 в качестве входов разрешения.

Функционирование дешифратора разрешено

при логической 1 на входе Е1 и логическом

0 на входах Е2, Е3. Такая организация шины

разрешения обеспечивает возможность

каскадирования дешифраторов и реализации

различных вариантов управления и

демультиплексирования одного канала

на восемь.

.

Вход Е1

может быть использован в качестве входа

выбора данного дешифратора, входы Е2,

Е3 в качестве входов разрешения.

Функционирование дешифратора разрешено

при логической 1 на входе Е1 и логическом

0 на входах Е2, Е3. Такая организация шины

разрешения обеспечивает возможность

каскадирования дешифраторов и реализации

различных вариантов управления и

демультиплексирования одного канала

на восемь.

К555ЛЕ4 – три логических элемента 3ИЛИ – НЕ (К155, К555, КМ555)

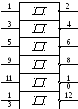

Рисунок

1.7.2.8. Условное графическое обозначение

К555ЛЕ4

Назначение

выводов: 1, 2, 3, 4, 5, 6, 9, 11, 13 – входы; 8, 10,

12 – выходы; 7 – общий; 14 – Uп.

К155ИД3 – дешифратор – мультиплексор 4 на 16.

Дешифратор К155ИД3 (условное графическое обозначение и назначение выводов представлено на рисунке 1.7.2.4.) выполняет две функции:

Рисунок

1.7.2.4. Условное графическое обозначение

К155ИД3

(Назначение выводов: 20-23 – информационные

входы; 18, 19 – стробирующие входы; 12 –

общий; 1-11, 13-17 – выходы; 24 – Uп.)

Дешифрирование 4-разрядного двоичного кода. В этом случае выходы

А0 – А3 являются информационными входами, на которые подаётся 4 – разрядное двоичное закодированное число. Каждому из 16 возможных 4-разрядных двоичных чисел соответствует один из 16 выходов дешифратора. Кроме четырёх входов А0 – А3 устройство имеет ещё два входа S1 и S2, которые при выполнении устройством функции дешифрирования играют роль стробирующих входов. При этом на стробирующих входах должен быть низкий уровень. Если хотя бы на одном из стробирующих входов устанавливается высокий уровень напряжения, то на всех 16 выводах устройства будет высокий уровень напряжения независимо от того, какой код подан на входы А0 – А3.

Демультиплексирование. В этом случае входы А0 – А3 являются селектирующими входами. Соответствующий код на этих входах позволяет сигналу проходить от информационного входа к выбранному выходу. Роль информационного входа при выполнении функции демультиплексирования играет один из входов S1 или S2. Другой вход используется как стробирующий. На стробирующем входе должен быть низкий уровень напряжения, в противном случае сигнал с информационного входа будет блокирован и не сможет пройти на выход устройства.

К555ТЛ2 – шесть триггеров Шмитта с инвертором (К155, К555, КМ555)

Триггер Шмитта существенно отличается от других триггеров прежде всего тем, что он не выполняет функции хранения информации. Его характеристика передачи имеет гистерезис с двумя пороговыми значениями напряжений на входе, при которых происходят сбрасывание и отпускание триггера. Таким образом триггер Шмитта формирует прямоугольные импульсы из колебаний произвольной формы.

Рисунок

1.7.2.5. Условное графическое обозначение

К555ТЛ2

(Назначение

выводов: 1,3,5,9,11,13 – входы; 2,4,6,8,10,12 –

выходы; 7 – общий; 14 - Uп)

Основные параметры микросхемы:

Напряжение срабатывания 1,6 В.

Напряжение отпускания 0,8 В

Средняя задержка 15 нс.

Частота переключения 30 МГц

Потребляемая мощность 50 мВт.

Тип корпуса 201.14.1

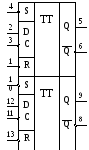

К555ТМ2 – два D - триггера (К155, КМ155, К531, КМ555)

Микросхема

К555ТМ2

(рисунок

1.7.2.6.)

является универсальным D-триггером

с однофазным приёмом информации и с

независимой установкой в состояние

низкого и высокого уровней.

Микросхема

К555ТМ2

(рисунок

1.7.2.6.)

является универсальным D-триггером

с однофазным приёмом информации и с

независимой установкой в состояние

низкого и высокого уровней.

Рисунок

1.7.2.6. Условное графическое обозначение

К555ТМ2

(Назначение

выводов: 1,2,3,4,10,11,12,13 – входы; 5,6,8,9 –

выходы; 7 – общий; 14 - Uп

).

Логическая структура D-триггера содержит следующие элементы: основной асинхронный RS-триггер (Т3); вспомогательный синхронный RS-триггер записи высокого уровня в основной триггер (Т1); вспомогательный синхронный RS-триггер записи низкого уровня в основной триггер (Т2).

Запись информации в D-триггере происходит по фронту импульса синхронизации. С приходом фронта импульса синхронизации в момент времени t информация, поступающая на вход D, принимается во все вспомогательные триггеры Т1, Т2, но на выходе появляется с задержкой в момент времени t + 1: Q( t + 1) = D( t ). Таким образом D-триггер следит за изменением входной информации в момент прихода фронта импульса синхронизации.

Основные параметры микросхемы:

Средняя задержка 15 нс.

Частота переключения 30 МГц

Потребляемая мощность 40 мВт.

Тип корпуса 201.14.2

К

Рисунок

1.7.2.7. Условное графическое обозначение

К555ЛП5

(Назначение

выводов: 1, 2, 4, 5, 9, 10, 12, 13 – входы; 3, 6, 8,

11 – выходы; 7 – общий; 14 – Uп

).

S

S