- •Глава 1 3

- •1.1. Компенсация реактивной мощности

- •1.2. Промышленные потребители реактивной мощности

- •1.3. Устройства компенсации реактивной мощности

- •1.4. Основные положения проектирования микропроцессорных устройств.

- •1.5. Техническое задание на разработку контроллера - компенсатора реактивной мощности

- •1.6. Общая характеристика

- •1.7. Обоснование элементной базы

- •1.7.1. Микропроцессор и микропроцессорный комплект

- •1.7.2. Память и логические элементы

- •1.7.3. Силовые элементы

- •1.8. Аппаратные средства контроллера

- •1.8.1. Плата контроллера

- •1.8.2. Плата тиристорного управления

- •1.8.3. Блок питания

- •1.8.4. Подключение контроллера – компенсатора

- •1.9. Алгоритмы контроля и управления

- •1.9.1. Измерение тока, напряжения и угла

- •1.9.2. Принцип управления конденсаторной установкой

- •1.10 Программное обеспечение контроллера

- •1.10.1. Структура программного обеспечения

- •1.10.1.1. Основная программа

- •1.10.1.2. Подпрограмма обработки прерывания trap

- •1.10.1.3. Подпрограмма обработки прерывания rst 7.5

- •1.10.1.4. Комплекс подпрограмм типа bios

- •1.10.2. Распределение адресного пространства

- •Область векторов прерываний

- •X8085.Exe

- •2.3. Аппаратные средства отладки

- •2.4. Программные средства отладки Сервисная программа контроллера-компенсатора

- •2.5. Конструктивное исполнение

- •2.6. Методика поиска неисправностей

- •Глава 3

- •4.1. Состояние и анализ безопасности жизнедеятельности в помещении лпэ

- •4.2. Основные мероприятия и технические средства по обеспечению безопасных и безвредных условий труда в помещении лпэ.

- •4.3. Мероприятия и технические средства по предупреждению чрезвычайных ситуаций и ликвидация их последствий

- •4.3. Мероприятия и технические средства по охране атмосферного воздуха в районе объекта

- •4.5. Расчет молниезащиты здания

- •Глава 5 Заключение

- •Литература

1.7. Обоснование элементной базы

1.7.1. Микропроцессор и микропроцессорный комплект

При разработке контроллера – компенсатора был выбран микропроцессор К1821ВМ85А (Intel 8085), хорошо зарекомендовавший себя в промышленных устройствах управления. Основными достоинствами этого микропроцессора является низкая потребляемая мощность – 0.2 Вт, высокая надёжность и помехозащищённость. Микропроцессор имеет одно напряжение питания, возможность последовательного ввода-вывода данных, встроенные тактовый генератор, системный контроллер и шинный формирователь [5].

Адресная шина микропроцессора 8085. В большинстве 8 – разрядных микропроцессоров каждой линии шины адреса соответствует свой вывод корпуса. Независимо от режима работы микропроцессора вывод A0 всегда выполняет функцию A0. Это упрощает применение 16 – разрядной шины адреса: 16 выводов корпуса группируют в соответствии со своим назначением и объединяют в системную шину адреса. В микропроцессоре 8085 используется другой принцип организации адресной шины – временное мультиплексирование функций, выполняемых выводами корпуса. Одни и те же выводы в различные моменты времени могут выполнять различные функции. Это позволяет «увеличить» число выводов 40 – выводного микропроцессора [6].

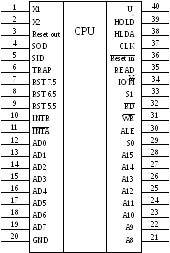

Восемь мультиплексируемых выводов микропроцессора 8085 выполняют функции шины данных или служат младшими разрядами шины адреса. Они служат для выдачи адреса из микропроцессора или для ввода – вывода данных. На рисунке 1.7.1.1. эти выводы обозначены AD0 – AD7. Восемь старших разрядов системной шины адреса A8 – A15 служат только для выдачи адреса.

Если применяется мультиплексирование выводов микропроцессора, необходимо блокировать появление на них данных AD0 – AD7 при выдаче разрядов адреса A0 – A7. Для блокировки нужно точно знать, когда по этим выводам передаются разряды адреса. Для этого служит специальный вывод корпуса микропроцессора (вывод 30), обозначенный ALE (разрешение записи адреса). Сигнал ALE обычно равен логическому 0 и устанавливается в состояние логической 1 только тогда, когда по выводам AD0 – AD7 микропроцессора 8085 передаётся младший байт адреса A0 – A7. К моменту сброса сигнала ALE адрес с выводов должен быть записан в устройство, для которого он предназначен.

Трёхстабильные буферы 74LS367 используются для буферирования только старших разрядов адреса A8 – A15, адресные линии A0 – A7 буферируются регистром 74LS374. Регистр 74LS374 является одновременно и регистром и буфером.

В технической документации микропроцессора 8085 обусловливается, что адрес должен выдаваться по заднему фронту сигнала ALE. Однако запись данных в 8- разрядный регистр 74LS374 осуществляется по переднему фронту тактового импульса. Чтобы записать разряды адреса A0 – A7 в 8 – разрядный регистр 74LS374 по заднему фронту сигнала ALE, этот сигнал необходимо инвертировать.

И ногда

используется регистр другого типа,

разрешающий передачу данных на выходеQ

в том случае, когда тактовый импульс

соответствует логической единице. При

сбросе тактового импульса данные на

выходе этого регистра остаются

неизменными. Таким регистром является

ИС 74LS373,

которая

позволяет выдавать информацию на шину

адреса сразу же после выдачи адреса

микропроцессором

8085.

ногда

используется регистр другого типа,

разрешающий передачу данных на выходеQ

в том случае, когда тактовый импульс

соответствует логической единице. При

сбросе тактового импульса данные на

выходе этого регистра остаются

неизменными. Таким регистром является

ИС 74LS373,

которая

позволяет выдавать информацию на шину

адреса сразу же после выдачи адреса

микропроцессором

8085.

Рисунок

1.7.1.1. Условное графическое обозначение

микропрцессора К1821ВМ85А

( Intel 8085 ).

Для стробирования поступающего из микропроцессора 8085 адреса можно использовать регистры любых типов при условии, что выходные токи регистров не вызывают перегрузки адресных выводов A0 – A7 микропроцессора.

Б уферированная

шина данных микропроцессора 8085.

Мультиплексируемую шину данных

микропроцессора 8085 можно буферировать.

Пусть в качестве буфера шины данных

используется схема 74LS245.

Если микропроцессор работает в режиме

приёма данных, то сигнал RD

на выводе

32 имеет активный низкий уровень. Этот

сигнал поступает на вход DIR

со схемы

74LS245.

уферированная

шина данных микропроцессора 8085.

Мультиплексируемую шину данных

микропроцессора 8085 можно буферировать.

Пусть в качестве буфера шины данных

используется схема 74LS245.

Если микропроцессор работает в режиме

приёма данных, то сигнал RD

на выводе

32 имеет активный низкий уровень. Этот

сигнал поступает на вход DIR

со схемы

74LS245.

Ш

ина

управления микропроцессора 8085.

Рассмотрим третью шину управления

микропроцессора 8085. Будем считать, что

шина управления состоит из четырёх

линий для передачи следующих сигналов:

чтение данных из памяти MEMR;

запись данных в память MEMW;

чтение данных из порта ввода IOR;

запись

данных в порт вывода IOW.

Для формирования шины управления

используются управляющие выводы

микропроцессора 8085 IO/M

(вывод 34), RD

(вывод 32) и

WR (вывод

31). Логические уровни сигналов управления

микропроцессора 8085 приведены в таблице

1.7.1.1.

ина

управления микропроцессора 8085.

Рассмотрим третью шину управления

микропроцессора 8085. Будем считать, что

шина управления состоит из четырёх

линий для передачи следующих сигналов:

чтение данных из памяти MEMR;

запись данных в память MEMW;

чтение данных из порта ввода IOR;

запись

данных в порт вывода IOW.

Для формирования шины управления

используются управляющие выводы

микропроцессора 8085 IO/M

(вывод 34), RD

(вывод 32) и

WR (вывод

31). Логические уровни сигналов управления

микропроцессора 8085 приведены в таблице

1.7.1.1.

Таблица 1.7.1.1.

Логические уровни сигналов управления МП К1821ВМ85А (Intel 8085)

|

Системная операция |

Вывод 32 |

Вывод 31 |

Вывод 34 |

|

IOR |

0 |

1 |

1 |

|

IOW |

1 |

0 |

1 |

|

MEMR |

0 |

1 |

0 |

|

MEMW |

1 |

0 |

0 |

С

игналIO/M

равен логической 1, если осуществляется

операция чтения данных из устройства

ввода (IOR)

или запись данных в устройство ввода

(IOW).

При

выполнении операции чтения данных из

памяти (MEMR)

или записи данных в память (MEMW)

сигнал IO/M

равен

логическому 0.

игналIO/M

равен логической 1, если осуществляется

операция чтения данных из устройства

ввода (IOR)

или запись данных в устройство ввода

(IOW).

При

выполнении операции чтения данных из

памяти (MEMR)

или записи данных в память (MEMW)

сигнал IO/M

равен

логическому 0.

С

игналыRD и

WR

имеют

активный уровень (логический 0), когда

в системе выполняется операция,

соответствующая назначению вывода.

игналыRD и

WR

имеют

активный уровень (логический 0), когда

в системе выполняется операция,

соответствующая назначению вывода.

Так как микропроцессор К1821ВМ85А совместим по архитектуре и системе команд с микропроцессором КР580ВМ80А используем ИС серии К580. К ним относятся такие микросхемы как КР580ИР82 (буферный регистр), КР580ВВ55А (программируемый параллельный интерфейс), КР580ВИ53 (трехканальный программируемый таймер), КР580ВВ51А (универсальный синхронно-асинхронный приёмопередатчик).