- •Введение

- •Техническое задание

- •Описание мпи Общие сведения.

- •Общая организация.

- •Функциональная организация.

- •Временные диаграммы взаимодействия устройства и мпи в выбранном режиме

- •Описание бмк 5501хм2

- •Используемые семисегментные индикаторы.

- •Реализация проекта Определение списка выводов бис.

- •Синтез структурной схемы устройства

- •Определение структуры устройства на верхнем уровне иерархии

- •Блок интерфейса с мпи

- •Первичный вариант

- •Альтернативный вариант

- •Внутренние регистры устройства

- •Блок индикации

- •Арифметико-логическое устройство (алу)

- •Синтез принципиальной схемы устройства Реализация принципиальной схемы на верхнем уровне иерархии

- •Реализация блока inout (интерфейса с мпи)

- •Реализация блока win (схемы управления адресным окном)

- •Реализация блоков outdv (буферных блоков)

- •Реализация блока dc8b (определения смещения внутри окна)

- •Реализация блока dc8n4 (индикации)

- •Реализация блока mux4x1

- •Реализация блока dec(семисегментного индикатора)

- •Реализация блоков reg8 (внутренних регистров)

- •Реализация блока summ8 (алу)

- •Реализация блока deccom (дешифрации команд)

- •Заказ контрольных точек

- •Моделирование работы устройства

- •Разработка топологии устройства Размещение устройства на бмк 5501хм2

- •Трассировка и оценка задержек

- •Оптимизация размещения

- •Маршрут проектирования

- •Технико-экономическое обоснование выбора проектирования схемы на бмк

- •Технико-экономический анализ прогрессивности принимаемого решения и формирование исходных данных для расчета

- •Выбор различных вариантов реализации схемы для сравнения и приведения их к сопоставимому виду

- •Расчет капитальных вложений

- •Расчет текущих затрат

- •Расчет основных показателей сравнительной экономической эффективности

- •Расчет капитальных вложений

- •Расчет текущих затрат

- •Расчет основных показателей сравнительной экономической эффективности

- •Список принятых сокращений

- •Инженерно-психологические факторы при обработке программ на эвм. Экологическая безопасность. Предисловие

- •Цели и задачи инженерно-психологического проектирования

- •Понятие интерфейса взаимодействия и принципы его проектирования

- •Человек как звено обработки информации Зрительная система человека и ее основные характеристики

- •Характеристики слухового аппарата человека

- •Преобразование информации в кратковременной памяти человека

- •Сенсомоторная деятельность оператора

- •Надежность выполнения операций

- •Надежность работы оператора с ручкой управления

- •Задачи инженерно-психологического проектирования взаимодействия человека и эвм

- •Экология

- •Выводы по главе 6

Синтез принципиальной схемы устройства Реализация принципиальной схемы на верхнем уровне иерархии

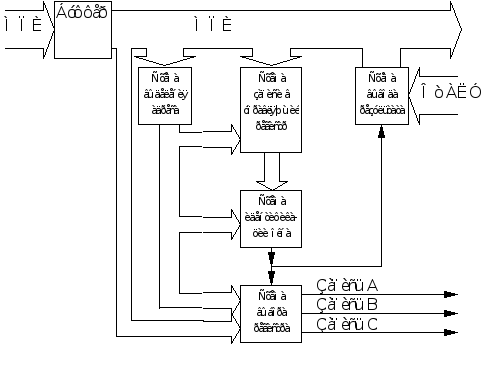

Схема УСТРОЙСТВА на верхнем уровне иерархии приведена на рисунке 9.

Представленные на схеме блоки выполняют следующие функции:

INOUT-Блок интерфейса с МПИ.

SUMM-Арифметико-логическое устройство

DC8N4-Блок индикации

RGU8-Внутренние регистры УСТРОЙСТВА

Реализация блока inout (интерфейса с мпи)

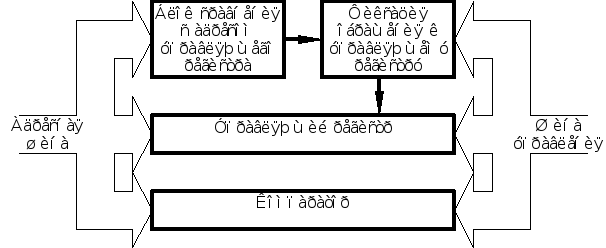

Блок интерфейса с МПИ служит для ввода и вывода информации, а также для управления УСТРОЙСТВОМ.

С учетом всего вышесказанного мы можем установить требования предъявляемые к интерфейсному блоку и определиться с его внутренней структурой:

Внутри блока должно обеспечиваться разделение адреса и данных

должен быть узел, обеспечивающий формирование и управление адресным окном (управляющий регистр со схемой записи)

необходим узел проверяющий попадание текущего адреса в адресное окно

необходима схема формирования сигналов управления внутренними регистрами

необходимо обеспечить возможность вывода результата с АЛУ на МПИ в соответствии с ГОСТ.

Структурная схема блока примет вид, показанный на рис.10.

Рис.9.Принципиальная логическая схема УСТРОЙСТВА

Рис.10..Структурная схема блока интерфейса с МПИ

Рассмотрим функции выполняемые отдельными блоками:

буффер-выполняет функции преобразования внешних сигналов во внутренние сигналы БИС без их логического изменения

схема выделения адреса - идентифицирует состояние шины в момент передачи по ней адреса

схема записи в управляющий регистр - идентифицирует обращение к управляющему регистру и записывает в него начальный адрес окна

схема идентификации окна - определяет обращение к адресному окну

схема идентификации регистра - определяет регистр к которому происходит обращение

схема вывода результата - обеспечивает вывод данных с выхода АЛУ на МПИ

Принципиальная логическая схема блока INOUT Приведена на рисунке 11.

Рассмотрим функции блоков, составляющих схему:

WIN-схема управления адресным окном и идентификации обращения по адресам, лежащим в адресном окне

OUTD-буфферные схемы для преобразования внешних сигналов БИС во внутренние и обратно, имеют третье состояние

RGU3-регистр для хранения смещения внутри адресного окна

DC8B-дешифратор смещения внутри окна

Рис.11.Принципиальная логическая схема блока INOUT

Реализация блока win (схемы управления адресным окном)

Для управления адресным окном нам необходимо знать адрес его начала. Однако мы должны иметь возможность оперативно изменять этот адрес. Для достижения этой цели мы зарезервируем один из адресов адресного пространства шины (в данном случае FFFFh) и присвоим его (адрес) регистру управления адресным окном. Поскольку внутри окна нам необходимо три адреса то легче всего позиционировать окно по 14 разрядам адреса. При этом под окно будут отведены 4 адреса, один из которых не будет использоваться.

При обращении на шине по любомуадресу блок управления сравнивает старшие 14 разрядов адреса и содержимое регистра управления окном. При совпадении этих величин на выходе блока появляется сигнал.

С учетом всего сказанного мы можем построить структурную схему блока управления окном. Она приведена ниже.

Рис.12.Структурная схема блока управления адресным окном

Принципиальная логическая схема построенная на основе данной структурной приведена на рисунке 13.

Блоки приведенные на рисунке 13 выполняют следующие функции:

COMPFF-определяет, является ли текущий адрес адресом управляющего регистра

COMP-определяет, лежит ли текущий адрес внутри адресного окна

REG-регистр хранения начального адреса адресного окна (управляющий регистр)

DT-регистр-защелка

Принципиальные логические схемы этих блоков и их раскрытие до нижнего уровня иерархии приведено на рисунках 14-19.

Рис.13.Принципиальная логическая схема блока WIN (управления адресным окном)

Рис.14.Принципиальная логическая схема блока COMPFF

Рис.15.Принципиальная логическая схема блока COMPFF

Рис.16.Принципиальная логическая схема блока COMP

Рис.17.Принципиальная логическая схема блока REG8

Рис.18.Принципиальная логическая схема блоков DT и DTT

Рис.19.Принципиальная логическая схема блока COMPA