- •12.1 Обобщённая структура компьютерных сетей

- •12.2 Классификация компьютерных сетей

- •7 Прикладной 6 Представительный 5 Сеансовый 4 Транспортный 3 Сетевой2 Канальный1 Физический

- •3.2.1 Коды с исправлением ошибок

- •3.2.2 Коды обнаруживающие ошибки

- •1.1 Основные понятия и определения

- •1.4 Многоуровневая организация вычислительных процессов

- •2.1 Комбинационные схемы

- •1) Конъюнкция (логическое умножение) .

- •2) Дизъюнкция (логическое сложение) .

- •3) Отрицание (инверсия) .

- •4) Конъюнкция и инверсия (Штрих Шеффера) .

- •5) Дизъюнкция и инверсия (Стрелка Пирса) .

- •6) Эквивалентность .

- •7) Отрицание эквивалентности .

- •3.1 Функциональные узлы последовательного типа

- •3.1.1 Регистры

- •3.1.2 Счётчики

- •3.2.1 Шифраторы и дешифраторы

- •3.2.2 Компараторы

- •3.2.3 Сумматоры

- •4.1 Основные характеристики и классификация процессоров

- •6.2.1 Прикладная программная модель процессоров Pentium

- •6.2.2 Системная программная модель процессоров Pentium

- •6.5 Перспективы развития процессоров

- •7.1 Иерархическая организация памяти

- •7.5 Ассоциативная память

- •8.4 Сегментно-страничная организация памяти

8.4 Сегментно-страничная организация памяти

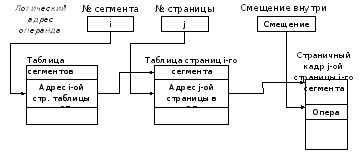

В соответствии с /2, 3, 8/, достоинства сегментной и страничной организации сочетает в себе сегментно-страничный способ распределения памяти, при котором память разбивается на сегменты, а сегменты, в свою очередь, разделены на страницы фиксированной длины. При этом размер сегмента выбирается не произвольно, а задаётся кратным размеру страницы. Сегмент может содержать произвольное, но обязательно целое число страниц, даже если одна из страниц заполнена частично. Для преобразования логических адресов в физические используются две таблицы соответствия. Каждый сегмент имеет отдельную таблицу страниц. В дескрипторной таблице сегментов перечисляются все сегменты с указанием начальных адресов страничных таблиц, относящихся к каждому сегменту. Каждая таблица страниц, в свою очередь, определяет положение каждой из страниц сегмента в памяти. Страницы сегмента могут располагаться не подряд – часть страниц может находиться в ОП, остальные – в ВЗУ. Схема вычисления физического адреса операнда при сегментно-страничной организации памяти представлена на рисунке 8.4 /3/. Виртуальный адрес операнда состоит из 3-х составляющих: номера сегмента, номера страницы в этом сегменте, смещения внутри данной страницы. Для получения физического адреса операнда сначала по номеру сегмента в таблице сегментов определяется начальный адрес соответствующей ему страничной таблицы, затем по номеру страницы в таблице страниц определяется начальный адрес конкретной страницы в ОП и, наконец, к базовому адресу страницы в ОП добавляется смещение внутри страницы.

Рисунок 8.4 – Вычисление физического адреса при

сегментно-страничной организации памяти

В заключение следует отметить, что процессор только предоставляет аппаратные средства поддержки виртуальной памяти, а их реальное использование зависит от корректного построения ОС.

В следующей главе рассмотрим принципы организации и функционирования подсистемы ввода вывода ВМ.