- •12.1 Обобщённая структура компьютерных сетей

- •12.2 Классификация компьютерных сетей

- •7 Прикладной 6 Представительный 5 Сеансовый 4 Транспортный 3 Сетевой2 Канальный1 Физический

- •3.2.1 Коды с исправлением ошибок

- •3.2.2 Коды обнаруживающие ошибки

- •1.1 Основные понятия и определения

- •1.4 Многоуровневая организация вычислительных процессов

- •2.1 Комбинационные схемы

- •1) Конъюнкция (логическое умножение) .

- •2) Дизъюнкция (логическое сложение) .

- •3) Отрицание (инверсия) .

- •4) Конъюнкция и инверсия (Штрих Шеффера) .

- •5) Дизъюнкция и инверсия (Стрелка Пирса) .

- •6) Эквивалентность .

- •7) Отрицание эквивалентности .

- •3.1 Функциональные узлы последовательного типа

- •3.1.1 Регистры

- •3.1.2 Счётчики

- •3.2.1 Шифраторы и дешифраторы

- •3.2.2 Компараторы

- •3.2.3 Сумматоры

- •4.1 Основные характеристики и классификация процессоров

- •6.2.1 Прикладная программная модель процессоров Pentium

- •6.2.2 Системная программная модель процессоров Pentium

- •6.5 Перспективы развития процессоров

- •7.1 Иерархическая организация памяти

- •7.5 Ассоциативная память

- •8.4 Сегментно-страничная организация памяти

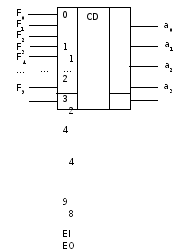

3.2.1 Шифраторы и дешифраторы

Шифраторы и дешифраторы относятся к преобразователям кодов. Шифратор преобразует код «1 из N» в двоичный, а дешифратор выполняет обратную операцию, преобразует двоичный код в код «1 из N».

Шифратор – это логическая схема, вырабатывающая на выходе определённое двоичное значение длиной n бит в зависимости от того, на каком из её 2n входов присутствует логическая 1. Полный шифратор имеет 2n входов и n выходов.

Условное

графическое изображение шифратора

приведено на рисунке 3.3, а таблица 3.2

отражает функционирование шифратора

на примере шифратора 10![]() 4

(10 входов, 4 выхода). Выходы шифратора

принято обозначать их двоичными весами.

4

(10 входов, 4 выхода). Выходы шифратора

принято обозначать их двоичными весами.

|

|

F0 ... F9 – входы шифратора; a0 ... a3 – выходы шифратора; EI – сигнал разрешения работы шифратора (разрешено при EI=1); EO – сигнал разрешения для разрешения работы следующего шифратора (при наращивании шифраторов). |

Рисунок 3.3 – Условное обозначение шифратора

Если логическая единица может присутствовать на нескольких входах, то применяется приоритетный шифратор, реагирующий на самый старший разряд входного слова. Такие шифраторы часто применяются для определения приоритетного претендента на использование какого-либо ресурса. Каждому устройству назначается претенденту назначается фиксированный приоритет на запрос ресурса. При одновременном наличии нескольких запросов обслуживается запрос с наибольшим приоритетом.

Таблица 3.2 – Принципы функционирования шифратора

|

Активный вход |

Выход | |||

|

a0 |

a1 |

a2 |

a3 | |

|

F0 |

0 |

0 |

0 |

0 |

|

F1 |

0 |

0 |

0 |

1 |

|

F2 |

0 |

0 |

1 |

0 |

|

F3 |

0 |

0 |

1 |

1 |

|

F4 |

0 |

1 |

0 |

0 |

|

F5 |

0 |

1 |

0 |

1 |

|

F6 |

0 |

1 |

1 |

0 |

|

F7 |

0 |

1 |

1 |

1 |

|

F8 |

1 |

0 |

0 |

0 |

|

F9 |

1 |

0 |

0 |

1 |

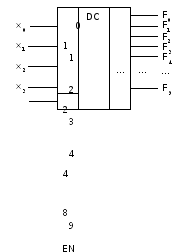

Дешифратор – это логическая схема, которая при подаче на её вход n- разрядного двоичного числа переводит один из своих 2n выходов в активное состояние (состояние логической 1) /4/. Таким образом, полный дешифратор имеет n входов и 2n выходов. Входы дешифратора принято обозначать их двоичными весами.

Условное

обозначение дешифратора представлено

на рисунке 3.4. Таблицу, отражающую

функционирование дешифратора (на примере

дешифратора 4![]() 10,

приводить не будем в силу её очевидности

(она будет представлять собой результат

транспонирования таблицы 3.2, приведённой

выше).

10,

приводить не будем в силу её очевидности

(она будет представлять собой результат

транспонирования таблицы 3.2, приведённой

выше).

|

|

x0 ... x3 – входы дешифратора; F0 ... F9 – выходы дешифратора; EN – сигнал разрешения работы дешифратора (разрешено при EN=1);

|

Рисунок 3.4 – Условное обозначение дешифратора

Шифраторы и дешифраторы используются в функциональных блоках и устройствах, где требуется преобразование кодов. Например, шифратор клавиатуры, шифратор и дешифратор адресов памяти и т.д.

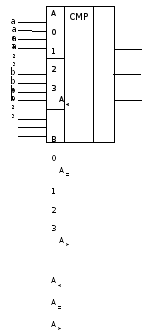

3.2.2 Компараторы

Компараторы (устройства сравнения) определяют отношения между двумя словами /5/.

Основные отношения, через которые модно выразить все остальные, это «равно» и «больше». Функции, вырабатываемые компараторами, определяются следующим образом: они принимают единичное значение (истинны), если соблюдается условие, указанное в индексе обозначения функции. Например, функция FA=B = 1, если A=B и принимает нулевое значение при A≠B.

В сериях цифровых элементов обычно выпускаются компараторами с тремя выходами «>», «<», «=». Условное обозначение компаратора (на примере компаратора с тремя выходами) представлено на рисунке 3.5.

|

|

a0 ... a3 – входы для первого слова; b0 ... b3 – входы для второго слова; A<, A=, A> - контакты для наращивания разрядности компаратора (с левой стороны) и выходы компаратора (с правой строны);

|

Рисунок 3.5 – Условное обозначение компаратора с 3 выходами

Каждая операция сравнения вычисляется в соответствии с логической формулой над двоичными переменными. Например, вычисление функции A>B отражено в таблице 3.3.

Таблица 3.3 – Вычисление функции A>B

-

A

B

A>B

0

0

0

0

1

0

1

0

1

1

1

0

Операции сравнения над многоразрядными словами выполняются на основе поразрядных операций над одноимёнными разрядами обоих слов.