- •2. Цифровые устройства [3, 4, 8, 9, 12, 13, 14, 16]

- •2.1. Общие сведения о цифровых интегральных схемах

- •Кмоп (564, к537, к588) – логика, основанная на комплементарной моп-технологии.

- •Перевод десятичного числа в восьмеричное

- •2.2.2. Элементы двоичной арифметики

- •2) Дополнительный код отрицательного числа создается путем единичного значения знакового разряда, инвертирования всех остальных цифровых разрядов и добавления «1» к младшему разряду;

- •Контрольные вопросы

- •2.3. Основы алгебры логики

- •2.3.1. Основные понятия и определения

- •2.3.2. Основные аксиомы и законы алгебры логики

- •2.3.3. Формы представления Булевых функций

- •2.3.3.1. Алгебраическое представление булевых функций

- •На основании законов булевой алгебры доказываются следующие свойства минтермов:

- •2.3.3.2. Представление Булевых функций в виде карт Карно

- •2.3.4. Минимизация Булевых функций

- •Контрольные вопросы

- •2.4. Синтез комбинационных логических устройств

- •2.4.1. Кодирующие устройства

- •2.4.1.1. Дешифраторы

- •2.4.1.2. Мультиплексоры и демультиплексоры

- •2.4.1.3. Шифраторы

- •2.4.2. Комбинационные двоичные сумматоры

- •Контрольные вопросы

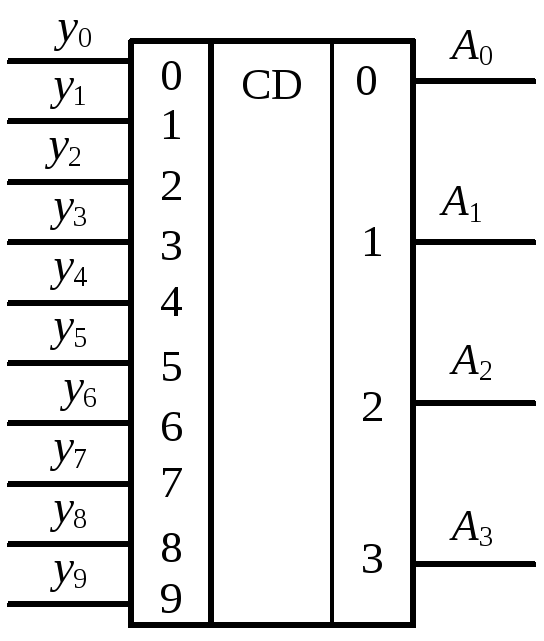

2.4.1.3. Шифраторы

Шифратор – это логическое устройство, выполняющее функцию, обратную дешифрированию. Схема шифратора имеет в общем случае m входов, из которых принимает истинное значение только один, и n выходов, из которых формируется двоичный код возбужденного входа. Очевидно, что m = 2n. Принцип построения шифратора поясним на примере шифратора, преобразующего унитарный код (числа 0…7) в трехразрядный двоичный код (сокращенно шифратор 8–3).

В табл. 2.11 отражена связь между входными сигналами y шифратора и значениями разрядов соответствующего двоичного числа, на основании которой получены выражения выходных функций А: А2 = y4 + y5 + y6 + y7; A1 = y2 + y3 + y6 + y7; A0 = y1 + + y3 + y5 + y7. Из полученных выражений следует, что выходные

Т а б л и ц а 2.11

|

i |

y7 |

y6 |

y5 |

y4 |

y3 |

y2 |

y1 |

y0 |

A2 |

A1 |

A0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

4 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

5 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

7 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

с

Рис.

2.14

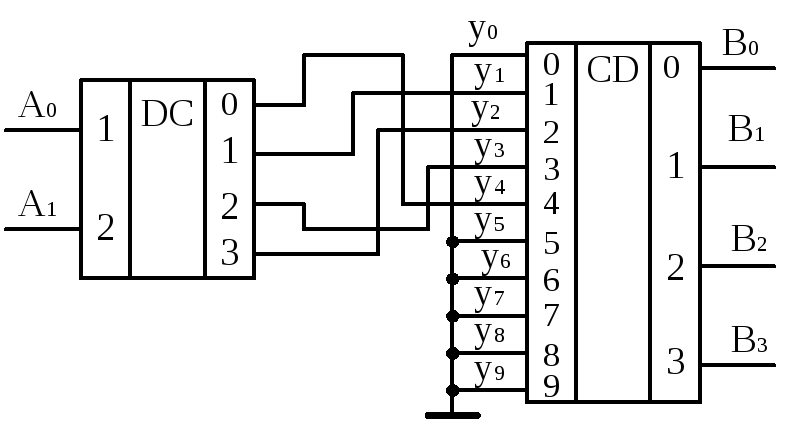

В общем случае описать работу преобразователя кода достаточно простым способом (как, например в случае шифратора) затруднительно или просто невозможно. Тогда единственно приемлемой формой задания закона функционирования преобразователя кода становится таблица истинности, из которой с помощью СДНФ или СКНФ создается ее алгебраическое выражение, реализуемое на стандартных логических элементах. Эффективным здесь оказывается использование пары дешифратор – шифратор, как это иллюстрируется следующим примером. Пусть соответствие входов А и выходов В преобразователя кода задано таблицей истинности (табл. 2.12).

Для получения выражений выходных функций В из табл. 2.12 можно идти обычным путем, используя описания функций в форме СДНФ или СКНФ с последующей их реализацией. Построение схемы станет иным, если составить другую таблицу, в которой двоичные коды входных и выходных сигналов заменены их десятичными эквивалентами (табл. 2.13).

Т а б л и ц а 2.12 Т а б л и ц а 2.13

|

А1 |

А0 |

В2 |

В1 |

В0 |

|

А |

В |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

4 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

2 |

3 |

|

1 |

1 |

0 |

1 |

0 |

|

3 |

2 |

Рис. 2.15

Преобразуя двоичный код входных сигналов в унитарный с помощью дешифратора и осуществляя вновь его шифрацию, получим схему рис. 2.15. Часть выходов дешифратора и шифратора может быть не использована, а свободным входам шифратора следует задать значение логического нуля.