Электроника Ч2

.pdf

221

2.1. АЦП последовательного счета.

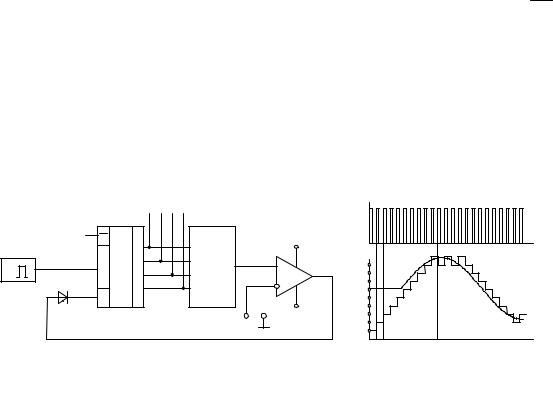

Структурная схема АЦП приведена на рис. 33.4, а. В состав схемы входят задающий генератор ЗГ, реверсивный счетчик импульсов СТ, ЦАП, аналоговый компаратор К и вентиль D. Работа схемы иллюстрируется гра- фиками рис. 33. 4, б.

Задающий генератор вырабатывает импульсы счета Uc с частотой дис- кретизации преобразуемой величины. Эти импульсы поступают на счетный вход реверсивного счетчика. Счетчик имеет вход разрешения счета EC ,

вход направления счета E ±1 и один счетный вход С. Для организации сче-

та в прямом направлении на вход E ±1 необходимо подать низкий уровень напряжения, для счета в обратном направлении – высокий. Число импуль- сов, поступивших на вход С, отображается состоянием выходов Q1 – Q4. Такой счетчик может быть реализован ИС К555ИЕ13.

EC

E±1 |

Допустим, что на инвертирующий вход компаратора поступает вход- ной аналоговый сигнал – положительное напряжение Uвх (пунктирная линия графика на рис. 33.4, б). Рассмотрим работу схемы с момента времени t = 0, когда на схему подано напряжение питания.

В момент времени t = 0 реверсивный счетчик находится в нулевом со- стоянии, т. е. Q1 = Q2 = Q3 = Q4 = 0. Напряжение на выходе ЦАП также рав- но нулю: UЦАП = 0. Следовательно, UЦАП – Uвх < 0, и на выходе компаратора

222

формируется отрицательное напряжение. Это напряжение запирает диод D и

падает на его большом сопротивлении. На вход E ±1воздействует низкий уровень напряжения. Начинается счет импульсов задающего генератора Uс на сложение. С каждым импульсом Uс код счетчика и соответствующее ему напряжение UЦАП увеличиваются.

Увеличение UЦАП продолжается до момента времени t1, после которого оно становится больше Uвх. Компаратор переключается в состояние положи-

тельного напряжения, которое через диод D передается на вход E ±1 и пе- реводит счетчик в режим работы на вычитание. Очередной импульс задаю- щего генератора уменьшает код счетчика, уменьшается UЦАП, и компаратор вновь переключается в первоначальное состояние. Далее процессы повто- ряются, при этом напряжение на выходе компаратора колеблется около зна- чения Uвх. Выходной сигнал ЦАП снимается с выходов Q1 – Q4 и отобража- ет Uвх в цифровой форме.

2.1. АЦП поразрядного уравновешивания

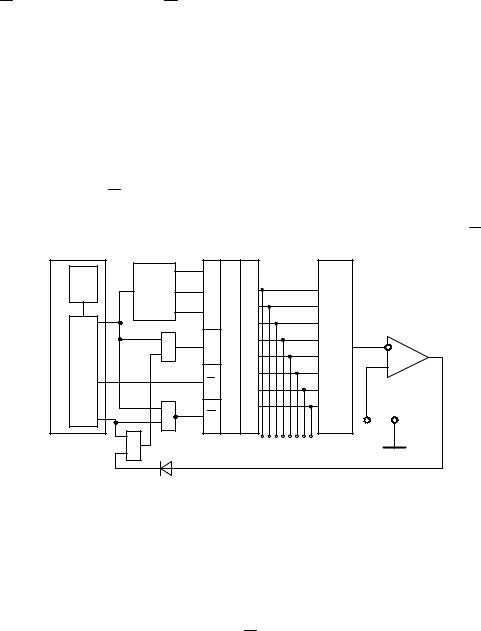

Метод поразрядного уравновешивания или последовательного при- ближения целесообразно применять в тех случаях, когда на интервале меж- ду двумя соседними отсчетами приращение аналогового напряжения !U значительно больше Uкв, а также, когда необходимо выполнять АЦП со строгой периодичностью за время, не зависящее от конкретных значений сигнала. Вариант упрощенной структурной схемы АЦП поразрядного урав- новешивания приведен на рис. 33.5. Графики напряжений, поясняющие ра- боту схемы, приведены на рис. 33.6.

Схема включает регистр поразрядного кодирования RG, ЦАП, компа- ратор, формирователь адреса и узел синхронизации. В его состав входят вспомогательные логические элементы: “И”, “ИЛИ” и “ИЛИ – НЕ”.

223

В качестве регистра поразрядного кодирования может быть применен восьмиразрядный регистр хранения с адресацией - К555ИР30. Регистр имеет три адресных входа: А0, А1, А2, информационный вход D, вход установки в

нуль R , вход разрешения E и восемь информационных выходов Q0 – Q7. Выходы регистра являются и выходами АЦП.

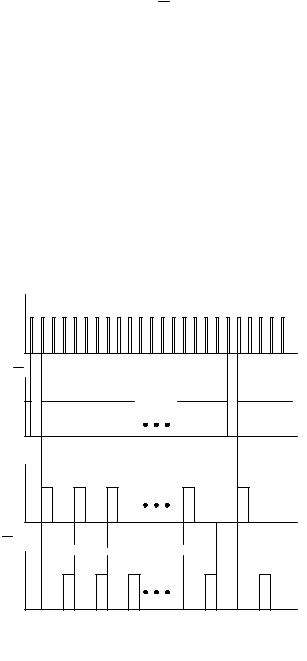

Узел синхронизации содержит задающий генератор и формирователь импульсов управления. Задающий генератор вырабатывает прямоугольные импульсы Uзг с тактовой частотой fТ (рис. 33.6), определяющей быстродейст- вие АЦП. Формирователь импульсов управления преобразует импульсы гене-

ратора в импульсы R , обеспечивающие обнуление разрядов регистра, в им-

пульсы управления формирователем адреса Uадр., а также в импульсы E и D.

{ |

Преобразование аналогового напряжения в цифровую форму осуще- ствляется циклами. Каждый цикл состоит из n тактов, причем, n – число разрядов АЦП (например, в схеме рис.33.5 n = 8). Начало цикла определяет-

ся временным положением импульса R . Этим импульсом все разряды реги- стра приводятся в нулевое состояние.

224

Начало первого такта определяется началом первого импульса Uадр.., который поступает на вход формирователя адреса через логический эле-

мент ИЛИ – НЕ на вход разрешения E , а через элемент ИЛИ – на вход D регистра. В результате воздействия этого импульса на указанные входы ус- танавливается адрес старшего (восьмого) разряда регистра, и в этот разряд записывается единица.

На выходе регистра последовательного приближения формируется на- чальная кодовая комбинация 10000000. Эта комбинация воздействует на вход ЦАП, отклик которого представляет напряжение UЦАП., соответствую- щее середине допустимого диапазона изменений входных аналоговых сиг- налов.

Напряжение UЦАП. поступает на инвертирующий вход компаратора. На прямой вход компаратора поступает аналоговый сигнал Uвх. Если Uвх > UЦАП., на выходе компаратора устанавливается положительное напряжение,

225

которое через диод D передается на вход элемента И. Импульсом E, D эле-

мент И открывается, и уровень логической единицы через ячейку ИЛИ пе-

редается на вход D регистра. Одновременно на входе разрешения E элемен- том ИЛИ – НЕ формируется разрешающий низкий уровень. Единица фикси- руется в старшем разряде, и первый такт цикла завершается. На этом этапе определяется значение старшего разряда кодовой комбинации.

Второй такт начинается вторым импульсом Uадр... В результате воздей- ствия этого импульса устанавливается адрес седьмого разряда регистра, и в этот разряд записывается единица. На выходе регистра формируется кодо- вая комбинация 11000000. Далее процессы проходят так же, как и в первом такте. Отличия могут заключаться только в результатах сравнения напряже- ния UЦАП, соответствующего новой кодовой комбинации, с Uвх.

Допустим, что на втором этапе UЦАП > Uвх. На выходе компаратора ус- танавливается отрицательное напряжение. Это напряжение ограничивается диодом D, и на входе элемента И формируется 0. На интервале очередного импульса E, D логический 0 фиксируется в седьмом разряде регистра.

Физические процессы, протекающие на последующих тактах, анало- гичны рассмотренным. На восьмом такте определяется значение младшего разряда, и кодовая комбинация с точностью Uкв. соответствует Uвх. Вывод данных может быть организован как в параллельном, так и в последователь- ном коде.

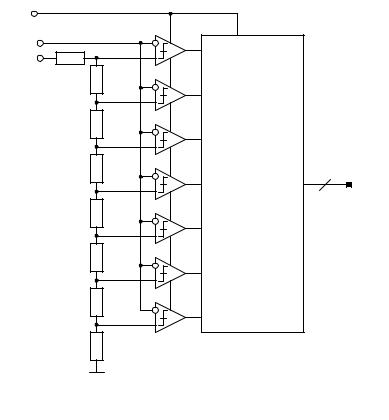

2.3.АЦП одновременного считывания

АЦП одновременного считывания отличаются высоким быстродейст- вием, но это качество окупается существенным усложнением схемного ре- шения. Схема n-разрядного АЦП состоит из 2n резисторов и 2n-1 компарато- ров, размещенных, как это показано на рис. 33.7. На прямой вход каждого i го компаратора подается опорное напряжение Uоп i, причем, его значение от-

226

личается от опорного напряжения соседних компараторов на величину од- ного кванта Uкв. При фиксированном входном напряжении все компараторы, размещенные на схеме ниже некоторой точки, имеют входное напряжение выше опорного. На их логическом выходе формируется "1". У компарато- ров, расположенных выше этой точки, входное напряжение меньше опорно- го, и их логический выход устанавливается в "0". Поэтому 2n–1 выходов компаратора ведут себя аналогично ртутному термометру, и выходной код такого АЦП иногда называют кодом термометра. В реальных схемах код термометра преобразуется шифратором в n-разрядный двоичный код.

Входной сигнал подается на все компараторы сразу. Следовательно, задержка выходного сигнала по отношению к входному определяется толь- ко переходными процессами в одном компараторе и в n-разрядном кодере.

227

Весь процесс преобразования осуществляется очень быстро. Максимальная частота дискретизации рассматриваемых АЦП может достигать 1 ГГц при ширине полосы пропускания по уровню полной мощности более 300 МГц.

Недостатки АЦП. Высокое быстродействие накладывает особые тре- бования к режиму работы элементов схемы. Каждый компаратор должен иметь довольно высокий уровень потребления энергии. Кроме того, добав- ление одного разряда к общей разрешающей способности параллельного преобразователя требует удвоения количества компараторов и резисторов. Это ограничивает практическую разрешающую способность высокоскоро- стных параллельных преобразователей до 8 разрядов, так как при более вы- соких разрешающих способностях слишком велико выделение тепла. Сле- довательно, к недостаткам АЦП одновременного считывания относятся ог- раниченная разрешающая способность, высокий уровень рассеивания энер- гии вследствие большого количества высокоскоростных компараторов и от- носительно большие размеры кристалла (а потому – высокая стоимость).

КОНТРОЛЬНЫЕ ВОПРОСЫ И ЗАДАЧИ

33.1.Какие функциональные узлы обязательны для делителя Кельвина?

33.2.Чем ЦАП с токовым выходом отличается от преобразователя Кельвина?

33.3.Четырехразрядный делитель Кельвина имеет Uоп = 1 В. Определите Uкв и Uвых делителя при поступлении на его вход кодовой комбинации 1010.

33.4.Четырехразрядный ЦАП с токовым выходом имеет Uоп = 1 В, R = 1000 Ом. Чему равен ток на выходе схемы, если на ее вход поступает кодовая комбинация 1010?

33.5.Определите число сегментов m, при котором в n разрядном ЦАП число звеньев делителя Кельвина (резистор – ЭК, плюс триггер) минимально. Найдите общую зависимость числа звеньев М от числа сегментов m.

33.6.В чем состоит суть АЦП методом последовательного счета?

228

33.7. Анализируя графики рис. 33.4, б, сформулируйте причину отклонения UЦАП.

от Uвх.

33.8. Полагая максимальную скорость приращения входного сигнала равной !Uвх[В/С], сформулируйте требования к частоте дискретизации fд., при которой разность

UЦАП – Uвх < Uкв..

33.9.В чем состоит суть АЦП методом поразрядного уравновешивания?

33.10.Приведите достоинства и недостатки АЦП одновременного считывания. Целесообразно ли применение к схеме рис. 33.7 секционирования?

ЛЕКЦИЯ 34. МИКРОПРОЦЕССОРЫ

1. ОБЩИЕ СВЕДЕНИЯ

Цифровые вычисления, логическое проектирование, программирова- ние, цифровая обработка информации и принятие решений стали возмож- ными с 1951 г., когда был создан первый компьютер. На начальном этапе развитие ЭВМ шло в направлении увеличения их вычислительной мощи. Это были дорогостоящие комплексы, и далеко не все предприятия могли иметь даже одну централизованную ЭВМ для решения задач первостепен- ной важности. Применение цифровой техники для решения большого пе- речня частных задач, например, управление станками, приводом электро- двигателей и т. д. было еще невозможно. Кроме того, на начальном этапе за- дачи программирования и проектирования электронных средств, в том чис- ле самих ЭВМ, рассматривались как обособленные задачи.

С момента появления миникомпьютеров в 1965 году проблемы, с которыми сталкивались прикладные программисты и разработчики машин, стали переплетаться. Миникомпьютеры стали применяться как составные

229

части систем, требующих быстрого принятия решений – систем реального времени.

С появлением в 1971 г. микропроцессоров началась эра программи- руемой логики. Теперь понятия программирования и принципы проектиро- вания логических схем сблизились настолько, что от программиста требует- ся проектирования аппаратуры, а от проектировщика – полное понимание принципов программирования. Область применения микропроцессоров зна- чительно расширилась. Сегодня они применяются в карманных калькулято- рах и в кассовых аппаратах магазинов, в научных и бытовых приборах, в оборудовании контор и в медицинском оборудовании.

Создание микропроцессоров во многом стало возможным изобретению в 1959 г. интегральных схем, а несколько позже – больших интегральных схем (БИС), позволяющих размещать тысячи транзисторов на одной полу-

проводниковой подложке. Микропроцессор – это программируемое логиче-

ское устройство, изготовленное по БИС – технологии. Отдельно взятое, та-

кое устройство не может решить какую – либо задачу. Чтобы решить задачу, его нужно запрограммировать и соединить с памятью и устройством ввода /

вывода. Совокупность микропроцессора, памяти и устройства ввода / выво-

да, направленная на выполнение определенной функции, называется микро-

процессорной системой или микрокомпьютером. Таким образом, микропро-

цессор является основной частью – ядром микрокомпьютера. Одновременно он открывает возможность для применения программируемых устройств в тех логических системах, для которых фактор стоимости оказывается важнее, чем скорость и разнообразие вычислений. Именно программирование микро- процессора позволяет применять его к решению широкого класса задач.

В последние годы огромный интерес к микропроцессорам проявляют инженеры – проектировщики аппаратуры. Это объясняется тем, что ограни- ченный набор БИС, выполняющих вполне определенные функции, позволя-

230

ет реализовать необходимое устройство цифровой обработки методами про- граммирования. Относительно низкая стоимость, малые габариты и потреб- ляемая мощность, высокая надежность и исключительная гибкость в приме- нениях ставят микропроцессорные наборы БИС вне конкуренции по сравне- нию с любой другой элементной базой цифровых устройств.

2. СТРУКТУРА МИКРОПРОЦЕССОРА

Обобщенная структурная схема микропроцессора приведена на рис. 34.1. Входящие в его состав программный счетчик (счетчик команд), стек, а также регистр команд служат для обработки команд. Команда – это кодовая

комбинация (слово), предписывающая процессору определенное действие.

Триггер переноса, АЛУ, общие (рабочие) регистры и регистр адреса данных предназначены для обработки данных (операндов). Дешифратор команд, а также блок управления и синхронизации (БУС) обеспечивают управление работой всей структуры. Взаимодействие всех функциональных узлов осу- ществляется по внутренним каналам передачи данных. Связь микропроцес- сора с запоминающим устройством и устройством ввода / вывода происхо- дит по адресной шине, шине данных и управляющей шине.

Микропроцессор работает со словами, состоящими из восьми битов. Такие слова, называемые байтами, удобны при выполнении арифметиче- ских и логических операций и используются в большинстве выпускаемых микропроцессоров. Если в расчетах встречаются числа “большей длины”, то применяются специальные программы для вычислений с “двойной точно- стью”, “тройной точностью” и т. д.

Для задания адреса памяти обычно используется 16 разрядов. Это по- зволяет прямо адресовать 216 = 65536 ячеек памяти. Число 65536 часто запи- сывают в виде 64К. Индексом К обозначают величину 210 = 1024.