- •1. Основные понятия высокопроизводительных вычислений

- •1.1 Характеристики и требования высокоскоростной обработки

- •1.2 Способы повышения скорости обработки

- •2. Взаимосвязь структур алгоритмов и исполнителей

- •3 Структурная организация высокопроизводительных вычислительных систем

- •3.1 Классификация вс по Флину

- •3.2 Параллелизм на уровне команд

- •3.3 Параллелизм на уровне процессоров

- •4 Параллельные алгоритмы в задачах сортировки

- •4.1 Проблемы сортировки на вычислительных машинах параллельного действия

- •5 Методы построения распределенных алгоритмов на основе понижения порядка производной

- •5.1 Переход от произвольной математической зависимости к системам дифференциальных уравнений

- •5.2 Методы численного интегрирования по Стилтьесу

- •5.3 Разностно-квантованные схемы интегрирования уравнений Шеннона в относительной форме записи

- •5.4 Примеры реализации формальных методов перехода от произвольной математической зависимости к системам дифференциальных уравнений

- •5.5 Разностно-квантованные схемы интегрирования. Расчет основных параметров цис

- •5.6 Задания для самостоятельного выполнения

- •5.6.1 Задание № 1

- •5.6.2 Задание № 2

- •Контрольные вопросы

- •5.6.3 Задание№ 3

- •5.6.4 Задание № 4

- •5.7 Примеры выполнения заданий

- •5.7.1 Моделирования функции , с использованием методов цис

3.2 Параллелизм на уровне команд

Центральный процессор – базовый элемент построения вычислительной системы, реализующий основные операции по обработке данных. В общем случае все действия, реализуемые при обработке любой машинной команды, принято называть циклом. Цикл обработки машинной команды включает следующие шаги:

Извлечение команды из оперативной памяти (ИК);

Декодирование команды, при котором определяют количество используемых операндов, их месторасположение и адреса в регистровой и/или оперативной памяти, а также устанавливают, какая операция должна быть выполнена (ДК).

Извлечение данных из оперативной памяти по сформированным на предыдущем шаге исполнительным адресам (ИД);

Обработка данных, связанная с выполнением арифметико-логических преобразований над операндами (ОД);

Запись результатов либо в регистровой памяти процессора, либо в оперативной памяти (ЗР);

Обработка прерываний, реализующая механизм реакции на возникновение особых случаев в процессе обработки машинной команды (ПР).

Цикл обработки машинной команды (ЦОМК) можно реализовать в виде последовательного выполнения действий в рамках каждого шага. В этом случае невозможно начать обработку очередной машинной команды, пока не завершено выполнение предыдущей команды. Повысить производительность работы процессора с последовательным принципом обработки машинных команд возможно лишь за счет повышения тактовой частоты. Однако рост частоты, на которой работает процессор, обладает ограничением, вызванным задержками распространения сигналов при прохождении через логические элементы схемы и внутренние линии соединений. Поэтому неограниченно повышать частоту процессора невозможно.

Альтернативным способом повышения производительности процессорного элемента является использование подхода параллельной обработки машинных команд. В рамках этого направления реализованы и активно применяются на практике принципы конвейерной и суперконвейерной обработки, суперскалярная и векторная организация вычислений.

3.2.1 Конвейерная обработка. Вычислительный конвейер обладает структурой, представленной совокупностью независимых ресурсов (блоков), каждый из которых отвечает за выполнение одного определенного шага цикла обработки машинной команды. Таким образом, в конвейере можно активизировать одновременное выполнение сразу нескольких машинных команд, но на разных стадиях цикла обработки. В общем случае конвейер в каждый момент времени способен обрабатывать максимум n машинных команд, где n – количество независимых блоков реализации стадий ЦОМК. Результаты работы предыдущего блока используют в качестве исходных данных для работы последующего блока (рисунок 3.4). Общими правилами для организации конвейерной обработки являются:

а) разбиение ЦОМК на большое количество независимых этапов. На практике данное число не превышает 20;

б) время выполнения операций на каждом этапе должно быть постоянным. Данный параметр принято называть тактом конвейера.

|

|

|

Рисунок 3.4. Структура конвейерного процессора |

На рисунке 3.5 представлены временные диаграммы работы конвейера при реализации шести машинных команд. В данном примере конвейер реализует пять стадий ЦОМК. На первом такте происходит обработка фазы извлечения машинной команды 1 в блоке ИК. На втором такте результаты выполнения операций в блоке ИК поступают в блок 2, где происходит декодирование извлеченной машинной команды 1. В это же время освободившийся блок ИК участвует в извлечении команды 2.

Начиная с такта 5, конвейер загружен полностью и обеспечивает одновременное выполнение пяти машинных команд. С этого момента на выходе конвейера на каждом такте формируется результат выполнения очередной команды.

Однако при работе конвейера возможно возникновение конфликтов (рисков), которые нарушают регулярность выполнения машинных команд или приводят к возникновению ошибок. Различаю риски трех типов:

|

|

|

Рисунок 4.5. Временная диаграмма работы конвейерного процессора |

а) структурный, который происходит при попытке нескольких блоков одновременно обратиться к одному и тому же ресурсу вычислительной системы;

б) риск по данным, возникает, когда наблюдается взаимосвязь различных команд по данным. Здесь возможно некорректное использование данных за счет не синхронизированных операций чтения и записи в разных командах;

в) риск по управлению, как результат неоднозначности при выборке следующей команды в случае команд условного перехода.

Минимизацию издержек, вызванных возникновением рисков, обеспечивают за счет рациональной организации алгоритмов решения, возможностей компиляторов, которые отслеживают потенциальные конфликты и искусственно устраняют их, а также аппаратных или аппаратно-программных механизмов предсказания хода развития вычислений на основе истории предыдущих исходов и событий.

Оценивать производительность конвейерной обработки принято следующими параметрами.

Ускорение – отношение времени обработки набора команд без конвейера и при его использовании (S). Время обработки потока из N команд на конвейере с K позициями и тактом конвейера вычисляют по выражению (3.1)

![]() (3.1)

(3.1)

Время вычисления потока из N команд на последовательном процессоре рассчитывают по выражению (4.2)

![]() .

(3.2)

.

(3.2)

Таким образом, ускорение вычисления на процессоре с конвейерной организацией равно (4.3)

![]() .

(3.3)

.

(3.3)

Эффективность – доля ускорения, приходящаяся на одну позицию конвейера (Е)

![]() .

(3.4)

.

(3.4)

Пропускная способность – эффективность (4.4), деленная на длительность такта конвейера (Р)

![]() .

(3.5)

.

(3.5)

Высокую производительность работы конвейера получают при соблюдении регулярности поступления объектов обработки и минимизации нарушения естественного порядка следования машинных команд.

3.2.2 Суперконвейерная обработка. Существует несколько способов, чтобы повысить скорость работы конвейера. Во-первых, за счет декомпозиции каждой стадии цикла обработки машинных команд на несколько подстадий с сокращением такта конвейера и соответствующим повышением частоты. Во-вторых, путем реализации в процессоре нескольких конвейеров, работающих с перекрытием. Первый способ принято называть суперконвейеризацией [6], второй – суперскалярной обработкой.

При организации процессора с суперконвейерной обработкой увеличивают количество выполняемых операций в рамках ЦОМК и выделяют для реализации каждой такой операции отдельный блок. При этом добиваются существенного снижения сложности выполняемых действий, что приводит к сокращению времени на их реализацию, т.е. каждый блок может функционировать с большей тактовой частотой. Во многом это становится возможным, поскольку на многих позициях конвейера выполнение операций занимает менее половины машинного такта. Как следствие, можно удвоить частоту тактовых импульсов конвейера, что обеспечивает выполнение сразу двух действий за один период машинного такта.

За счет декомпозиции на каждой стадии можно выполнять операции для нескольких команд, что повышает степень параллелизма. На рисунке 3.6 представлена временная диаграмма работы процессора с суперконвейерной организацией, предусматривающей декомпозицию каждой стадии ЦОМК на две подстадии. Используя данный подход, появляется возможность дополнительно сократить продолжительность выполнения набора машинных команд.

Однако на практике не всегда удается достичь существенного выигрыша производительности вычислений от перехода к суперконвейерной обработке. Во многом это связано с повышением вероятности возникновения конфликтов, а также с существенным усложнением логики устройства управления суперконвейерного процессора. Кроме того, при ошибке предсказания условного перехода необходимо произвести очистку конвейера. При большом числе ступеней и подступеней наблюдается довольно длительный простой процессора, вызванный задержкой полного заполнения конвейера. Промах предсказания ветвления приводит к серьезным штрафам в работе суперконвейерного процессора, которые снижают общий показатель эффективности его работы.

|

|

|

Рисунок 4.6. Временная диаграмма работы суперконвейерного процессора |

Однако совершенствование механизмов предотвращения рисков обеспечивает надежную работу суперконвейера с высокой производительностью.

3.2.3 Суперскалярная обработка Суперскалярный процессор включает в свой состав несколько самостоятельных блоков обработки данных, отвечающих за выполнение определенных классов операций. Термин «скалярный» используют, чтобы особо отметить принципиальное отличие данных процессоров от вычислителей, работающих с векторными данными [3]. Такая организация позволяет процессору одновременно выполнять несколько команд над скалярными данными. В общем случае суперскалярная обработка происходит параллельно на разных конвейерах процессора (рисунок 3.7). Здесь на стадии 1 ЦОМК необходимо производить выборку нескольких команд, каждая из которых поступает на обработку в свой конвейер и блок выполнения команд. Для обеспечения множественной выборки команд и данных необходима специальная организация памяти.

|

|

|

Рисунок 3.7. Структура многоконвейерного суперскалярного процессора |

Снизить сложность управления суперскалярным процессором удается за счет использования одного конвейера, с большим числом блоков обработки (рисунок 3.8). Обычно операции, реализуемые на стадиях 1 – 3, требуют существенно меньше времени, чем собственно выполнение машинной команды. Таким образом, стадии 1 – 3 обеспечивают подготовку команды для обработки и загрузку соответствующего операционного блока. Если исходные данные очередной команды зависят от результата выполнения предыдущей команды, то такая команда не может поступить на обработку, пока не завершится обработка предыдущей. В общем случае суперскалярный процессор может менять порядок выполнения машинных команд, заданный в исходном коде программы, не нарушая логики ее работы.

Как правило, для каждой группы машинных команд в суперскалярном процессоре реализован независимый блок обработки, а иногда и несколько. Например, АЛУ обработки чисел в формате с плавающей точкой, АЛУ обработки чисел в формате с фиксированной точкой, блоки загрузки и сохранения данных и т.д.

|

|

|

Рисунок 3.8. Суперскалярный процессор с единственным конвейером |

Эффективность работы суперскалярных процессоров соизмерима с показателями суперконвейерных вычислителей при естественном порядке следования машинных команд. При наличии условных переходов суперскалярный процессор обеспечивает меньшие задержки, вызванные штрафом за ошибку предсказания перехода. На рисунке 3.9 приведены сравнительные диаграммы функционирования суперконвейерного и суперскалярного процессоров при выполнении одинаковых машинных программ.

|

|

|

Рисунок 3.9. Временная диаграмма работы процессора: суперконвейерного (а) и суперскалярного (б) |

Производительность суперскалярных процессоров во многом зависит от возможности параллельного выполнения команд в каждой конкретной программе. Данную возможность связывают с понятием параллелизм на уровне команд (instruction-level parallelism). Распараллеливание операций в процессоре связано с рядом ограничений, основными из которых являются

зависимость по данным,

процедурная зависимость,

конфликт использования ресурсов,

зависимость по выходу,

обратная зависимость.

Если в соседних командах программы отсутствует зависимость по данным, то их можно извлечь и одновременно обработать в двух независимых операционных блоках. В противном случае выполнение последующей команды должно быть отложено на столько тактов, пока не будут сформированы для нее все исходные данные.

Процедурная зависимость связана с двумя ситуациями – наличием команд условного перехода, когда до завершения данной команды невозможно определить адрес следующей команды, и использованием команд переменной длины, когда извлечение следующей команды невозможно до полного или частичного декодирования предыдущей команды.

Конфликт использования ресурсов возникает, когда для выполнения разных машинных команд необходим один и тот же функциональный узел процессора – память, шина, регистр и т.д.

Зависимость по выходу предусматривает невозможность совместного выполнения (группирования) не соседних машинных команд в силу влияния результатов их выполнения на получение некорректных результатов при выполнении других команд. Другими словами зависимость по выходу запрещает нарушать порядок выполнения машинных команд, как он представлен в программе.

Обратная зависимость возникает в том случае, когда последующая команда изменяет данные, используемые при выполнении предыдущей команды. В этом случае последующая команда не может быть завершена, пока не начнется выполнение предыдущей команды и не будут извлечены соответствующие данные.

Последние два ограничения возникают при использовании технологии свободного порядка запуска или свободного порядка завершения команд, которая реализует опережающий просмотр команд, используемых в программе. При такой организации команда после декодирования поступает в буфер, где ожидает освобождение необходимого функционального узла. Когда необходимый ресурс становится свободным для выполнения команды, команда извлекается из буфера и поступает на позицию выполнения конвейера. При этом из буфера может быть извлечена любая первая команда, для выполнения которой необходим освободившийся узел и этому не мешает какой-либо конфликт или зависимость.

Таким образом, к аппаратным и программным ресурсам суперскалярного процессора предъявляют следующие требования [7]:

реализация параллельного считывания нескольких команд и прогнозирование ветвления после команд условного перехода;

реализация механизма, изменяющего порядок выполнения команд по сравнению с последовательностью их расположения в программе без изменения логики ее работы;

построение логики выявления зависимостей по данным и механизма обмена этими данными для корректного выполнения команд;

реализация механизма параллельного выполнения нескольких машинных команд с возможностью нескольких одновременных обращений к памяти;

реализация механизма, управляющего фиксацией результатов выполнения отдельных команд в порядке, который соответствует исходному потоку команд, описанному в программе.

3.2.4 Векторный процессор. Многие задачи, решаемые с помощью средств вычислительной техники и требующие высокой производительности, ориентированы на выполнение однотипных операций над структурированными типами данных, например массивами или векторами. Элементы массива могут быть целочисленными или вещественными, действительными или комплексно-сопряженными числами. Эффективную обработку таких структур данных можно организовать на основе использования процессора с векторной организацией.

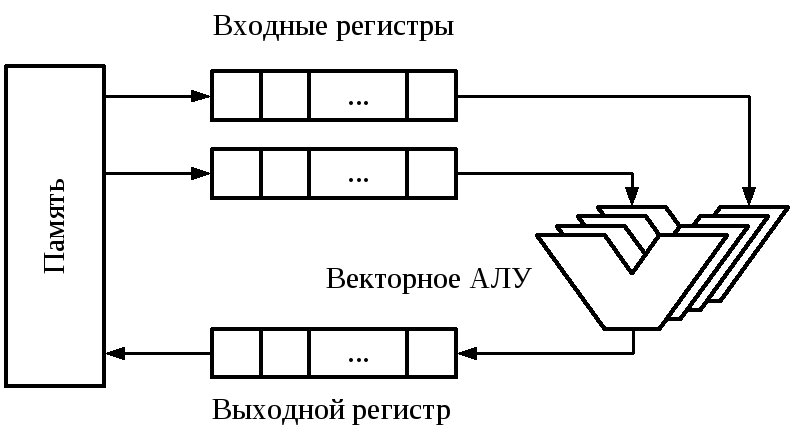

Векторный компьютер обеспечивает параллельное выполнение операций над n-элементами векторов-операндов с записью полученных результатов в соответствующий n-элементный вектор. В общем случае векторный компьютер можно построить с использованием векторного АЛУ (рисунок 3.10, а) или с использованием нескольких однотипных конвейерных АЛУ, работающих синхронно над разными наборами данных (рисунок 3.10, б).

Векторное АЛУ оперирует с n-элементами одновременно, выполняя над каждой парой исходных данных одинаковые действия. Результатом его работы также является вектор. Векторный процессор можно использовать также для выполнения скалярных операций. Однако в этом случае удобнее реализовать механизм преобразования скалярного операнда в вектор, каждый элемент которого равно скалярному операнду, и использовать его на уровне векторной операции.

В векторных процессорах с несколькими конвейерными АЛУ сочетают векторную обработку с конвейеризацией. В этом случае все действия над структурированными данными представляют набором простых операций, которые затем реализуют отдельной стадией конвейера. На последней стадии происходит формирование результата вычислений. Таким образом, при обработке векторных данных после заполнения конвейер обеспечивает формирование результата на каждом такте синхросигнала.

|

|

|

а) |

|

|

|

б) |

|

Рисунок 3.10. Векторный процессор: с векторным АЛУ (а), с конвейерным АЛУ (б) |